文章目录

- 前言

- 一、介绍

- 1、目标

- 2、过程

- 二、步骤 1:在 FPGA 中创建设计

- 1、打开 Lab1_1.slx 文件

- 2、运行仿真

- 3、使用 System Generator 创建 FIR 滤波器

- <1>、从库浏览器寻找需要的模块

- <2>、配置系统生成器块

- <3>、在 FPGA 上实现设计

- 三、步骤 2:在 FPGA 中创建优化设计

- 1、运行 Lab1_2.slx 文件

- 2、进行优化设计

- 四、步骤 3:使用离散资源创建设计

- 1、运行 Lab1_3.slx 文件

- 2、将分立组件添加到设计中

- 五、步骤 4:使用数据类型

- 第 1 部分:使用浮点数据类型进行设计

- <1>、打开 Lab1_4_1.slx 文件

- <2>、配置及运行

- 第 2 部分:定点数据类型设计

- <1>、打开 Lab1_4_2.slx 文件

- <2>、配置及运行

- 总结

前言

有关 System Generator 的安装以及简介可以参考我之前的博客 Matlab Simulink支持system generator插件,本文将初体验 System Generator,以达到如下目的:

- 了解如何使用 System Generator 创建和验证模型

- 利用工作空间变量轻松地对模型进行参数化

- 将模型综合到 FPGA 硬件中,然后创建更优化的硬件版本的设计

- 了解如何使用定点数据类型在准确性与硬件面积和性能之间进行权衡

一、介绍

在本实验练习中,你将学习如何使用 System Generator 在 Simulink 中指定设计并将设计合成为 FPGA。本教程使用标准 FIR 滤波器,并演示系统生成器如何为您提供设计选项,使你能够控制最终 FPGA 硬件的保真度。

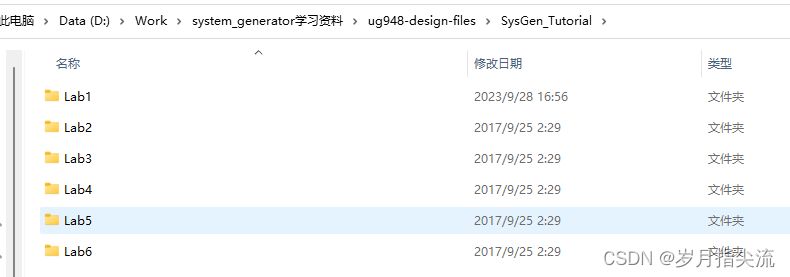

本教程中的每个实验都有单独的项目文件和源代码。您可以在 www.xilinx.com 网站上找到本教程的设计文件。

①、从 Xilinx 网站下载参考设计文件。

②、将 zip 文件内容解压缩到硬盘驱动器或网络位置上任何可写访问的位置。

1、目标

完成本实验后,你将能够:

- 使用系统生成器块集捕获你的设计

- 在复杂或离散的块集中捕获你的设计

- 使用 Vivado 设计环境在 FPGA 中合成你的设计。

2、过程

本实验有四个主要部分:

- 在第 1 步中,你将使用 Xilinx FIR 编译器块审查现有的 Simulink 设计,并在 Vivado 中审查最终的门级结果

- 在步骤 2 中,你将使用过采样来创建更有效的设计

- 在步骤 3 中,使用标准离散块集部件设计相同的滤波器

- 在第 4 步中,你将了解如何使用数据类型,如浮点型和定点型

二、步骤 1:在 FPGA 中创建设计

在此步骤中,你将学习 System Generator 的基本操作以及如何将 Simulink 设计合成到 FPGA 中。

1、打开 Lab1_1.slx 文件

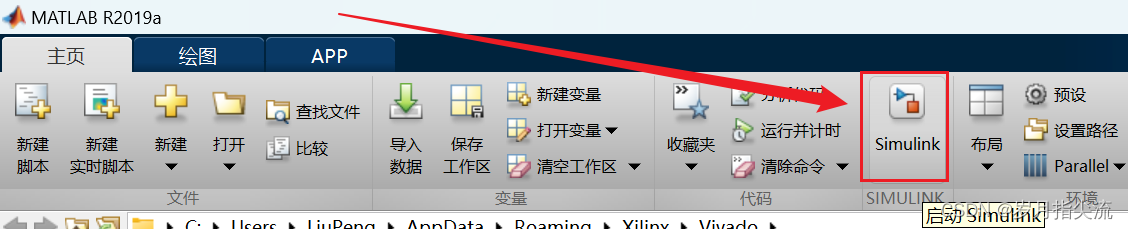

①、双击桌面 System Generator 2017.4

②、点击 Simulink

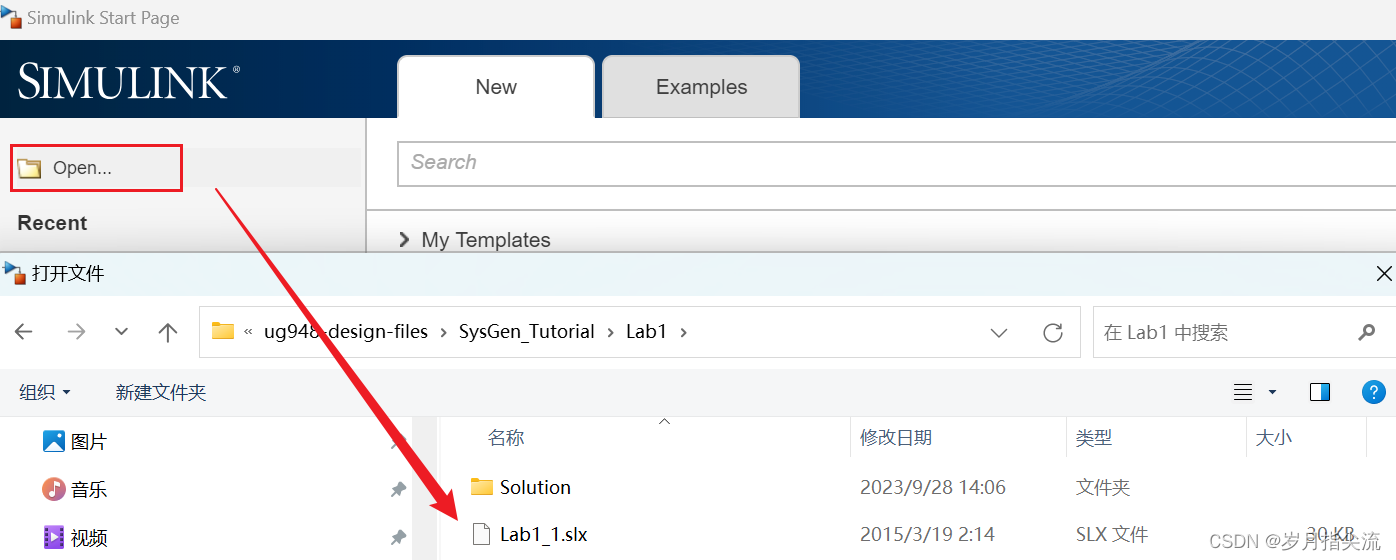

③、打开 Lab1_1.slx 文件

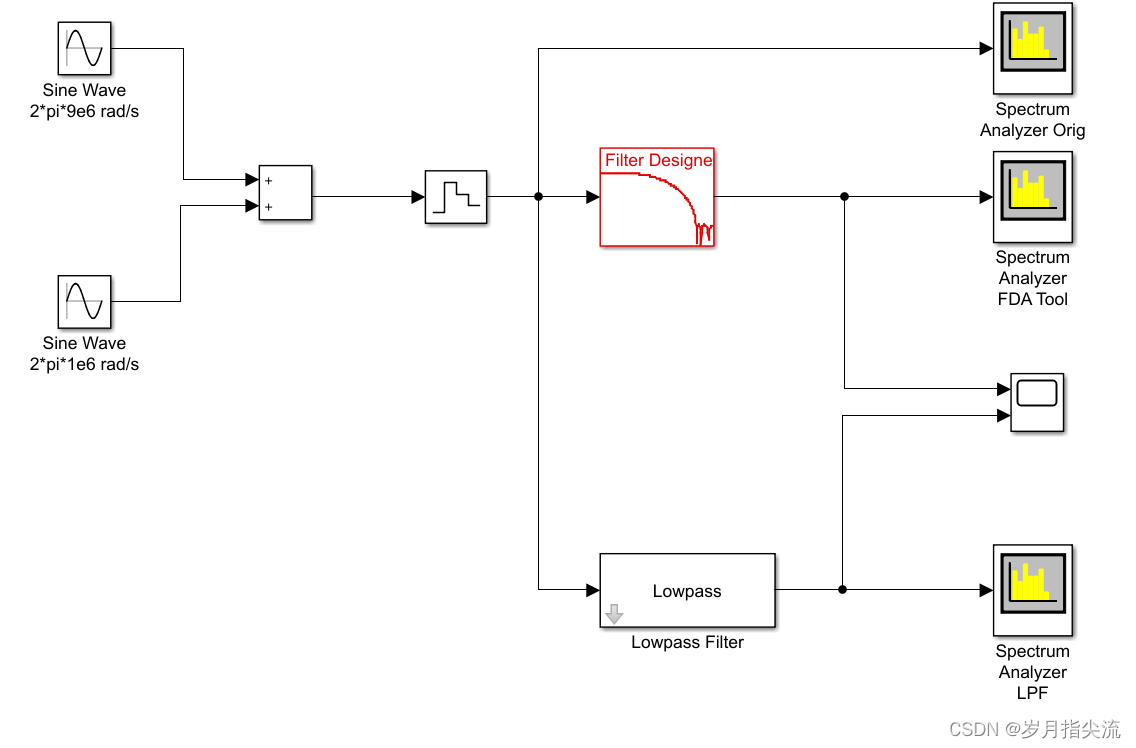

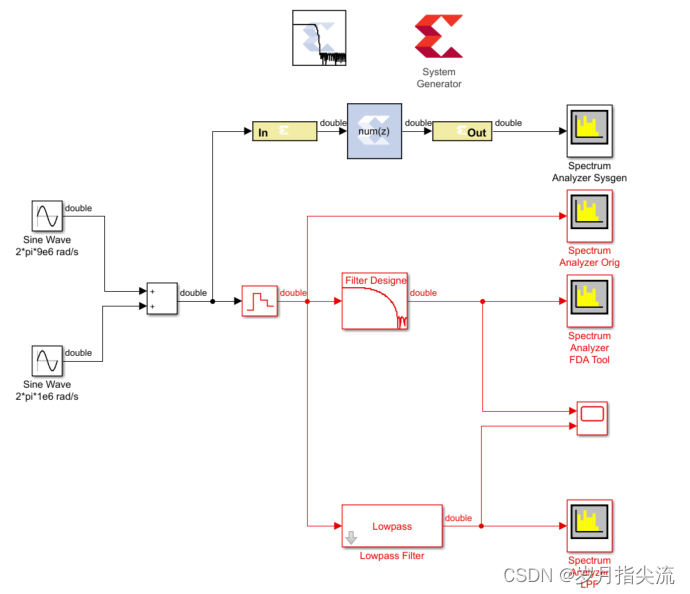

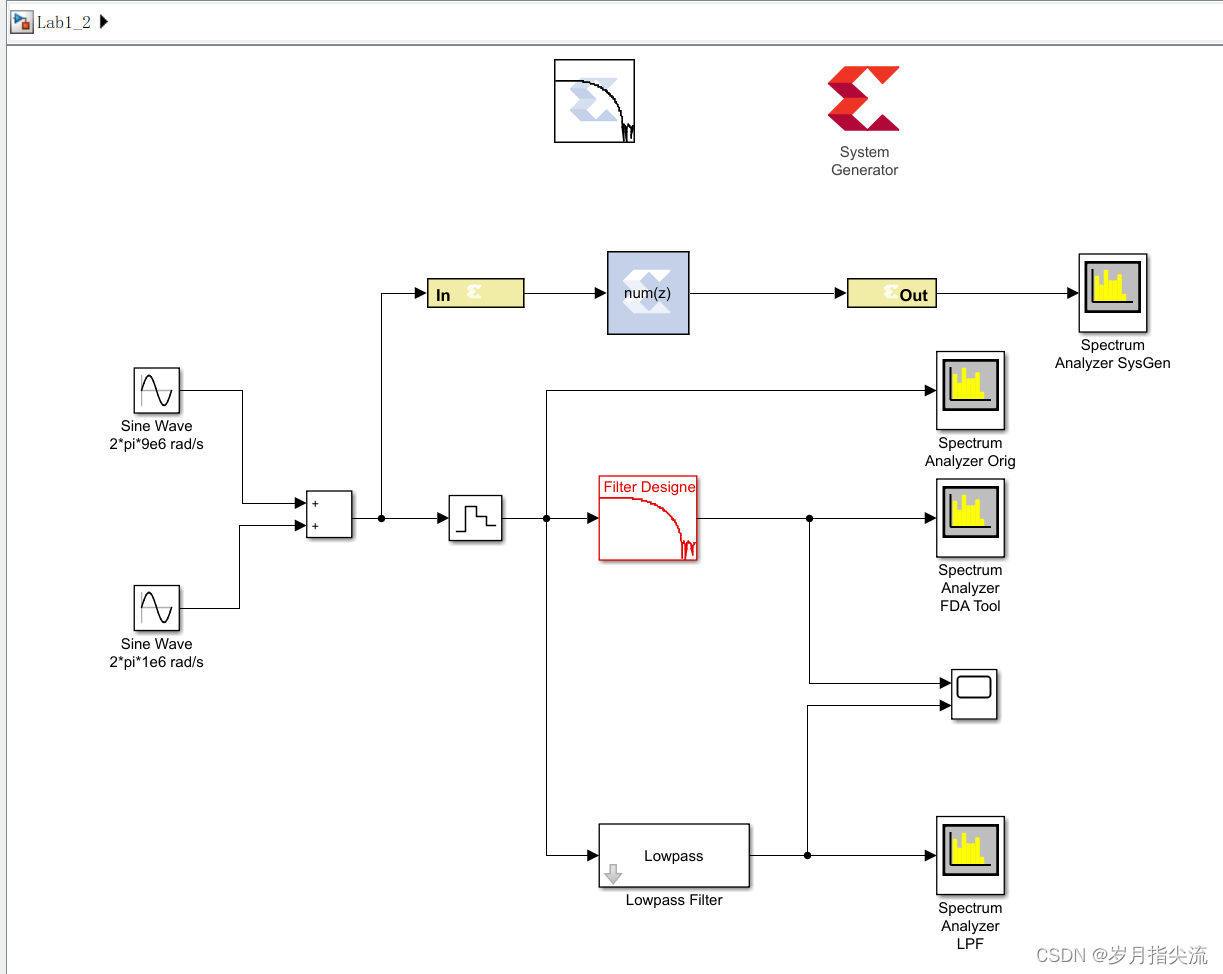

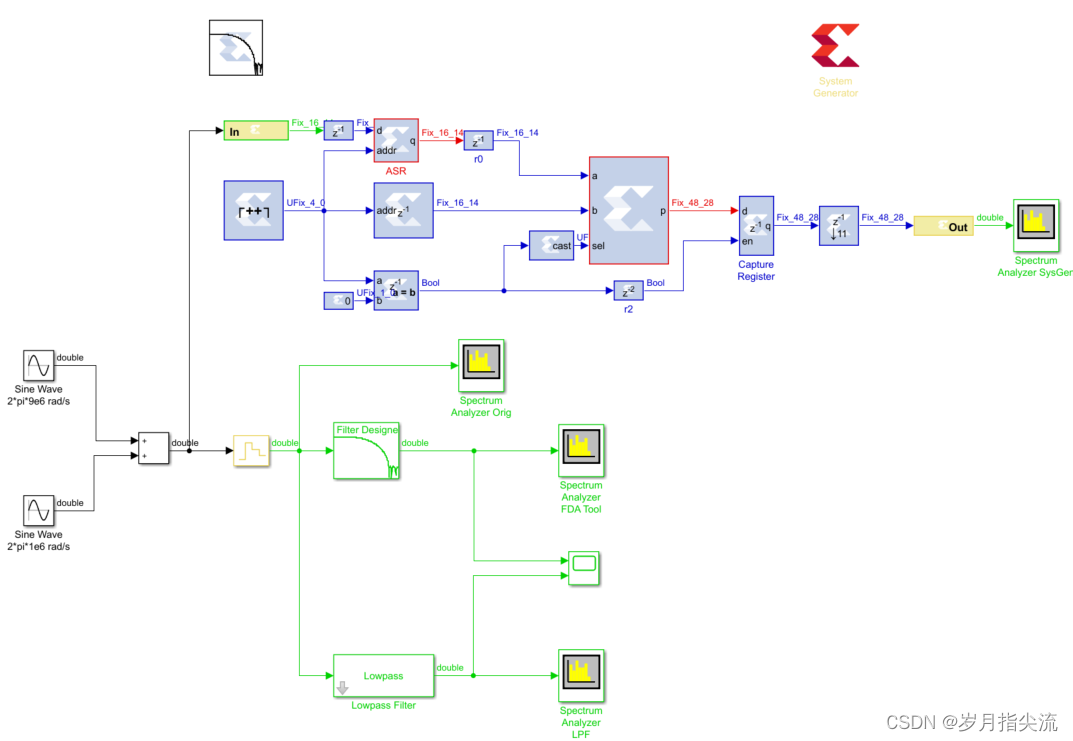

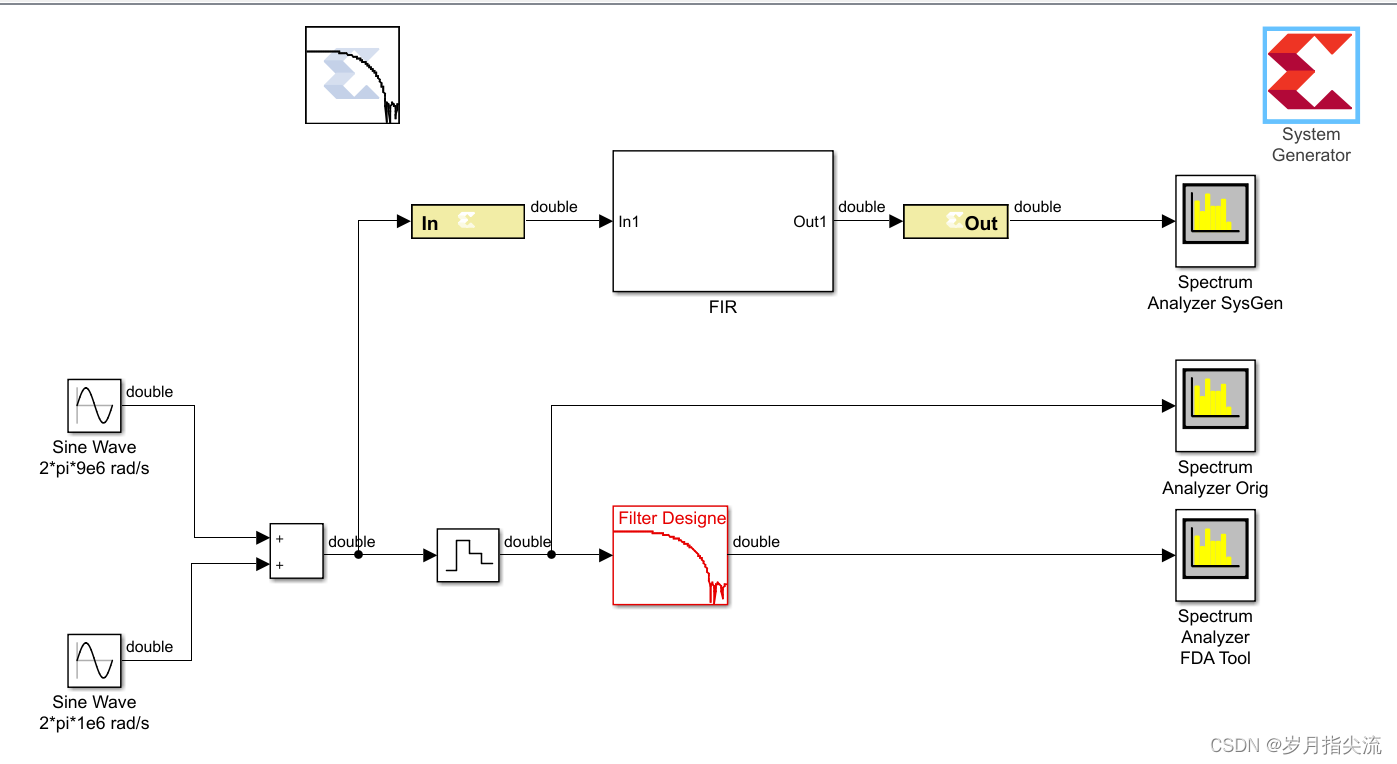

Lab1_1 设计打开,显示两个正弦波源被加在一起,分别通过两个低通滤波器。本设计强调低通滤波器可以使用Simulink FDATool 或低通滤波器块实现。

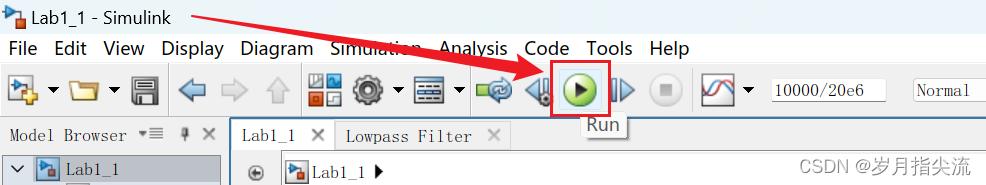

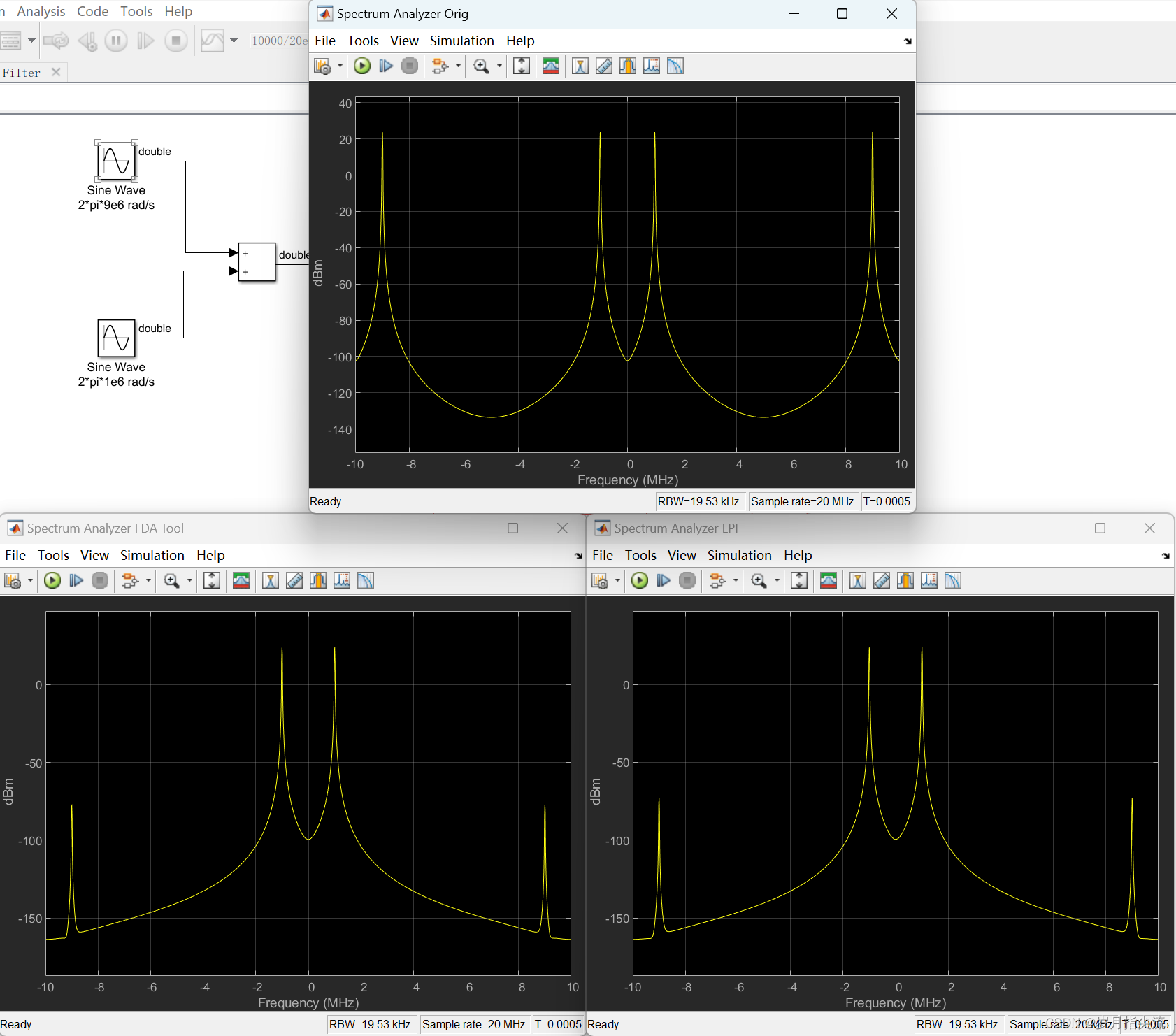

2、运行仿真

从 Simulink 项目工作表中,选择 Simulation>Run 或单击 Run 仿真按钮。

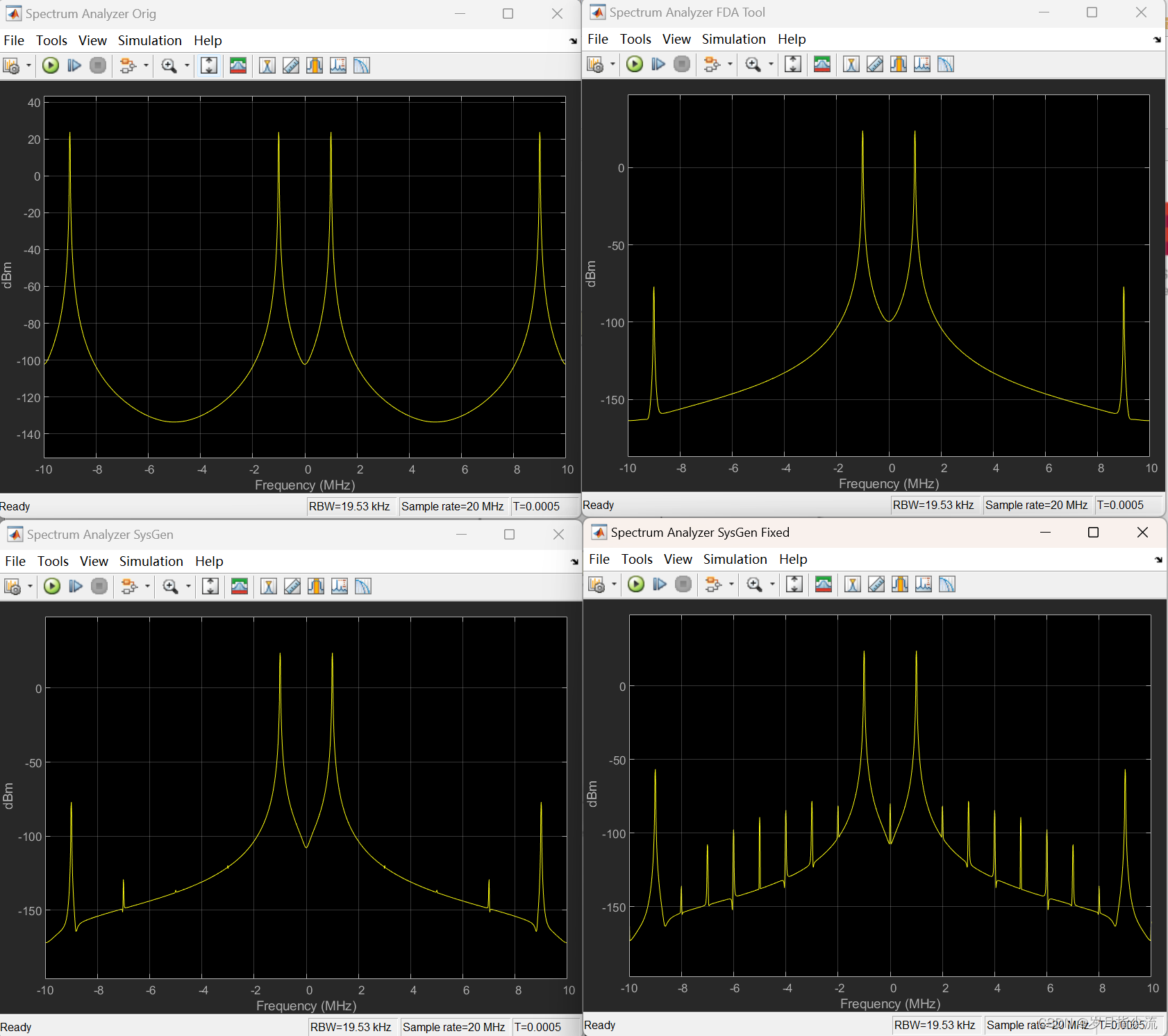

仿真完成后,你可以看到初始求和波形的频谱,显示 1MHz 和 9MHz 分量,以及两个滤波器的结果,显示 9MHz 信号的衰减。

3、使用 System Generator 创建 FIR 滤波器

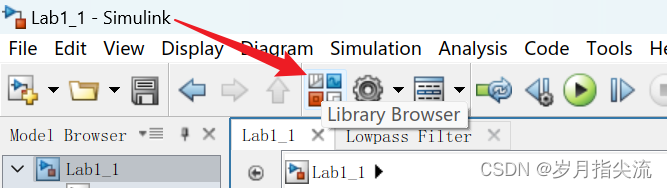

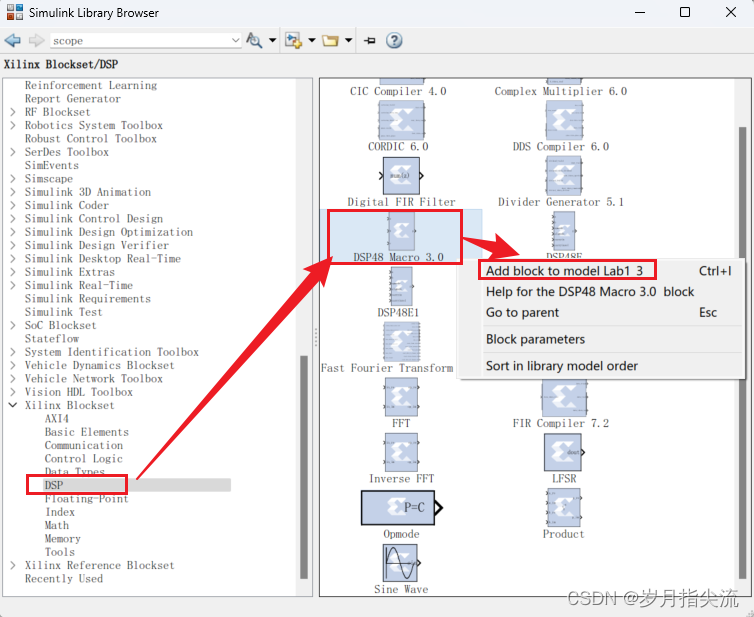

<1>、从库浏览器寻找需要的模块

现在,你将使用 System Generator 块创建同一过滤器的一个版本,以便在 FPGA 中实现

①、点按 Simulink 工具栏中的 “库浏览器” 按钮以打开 Simulink 库浏览器。

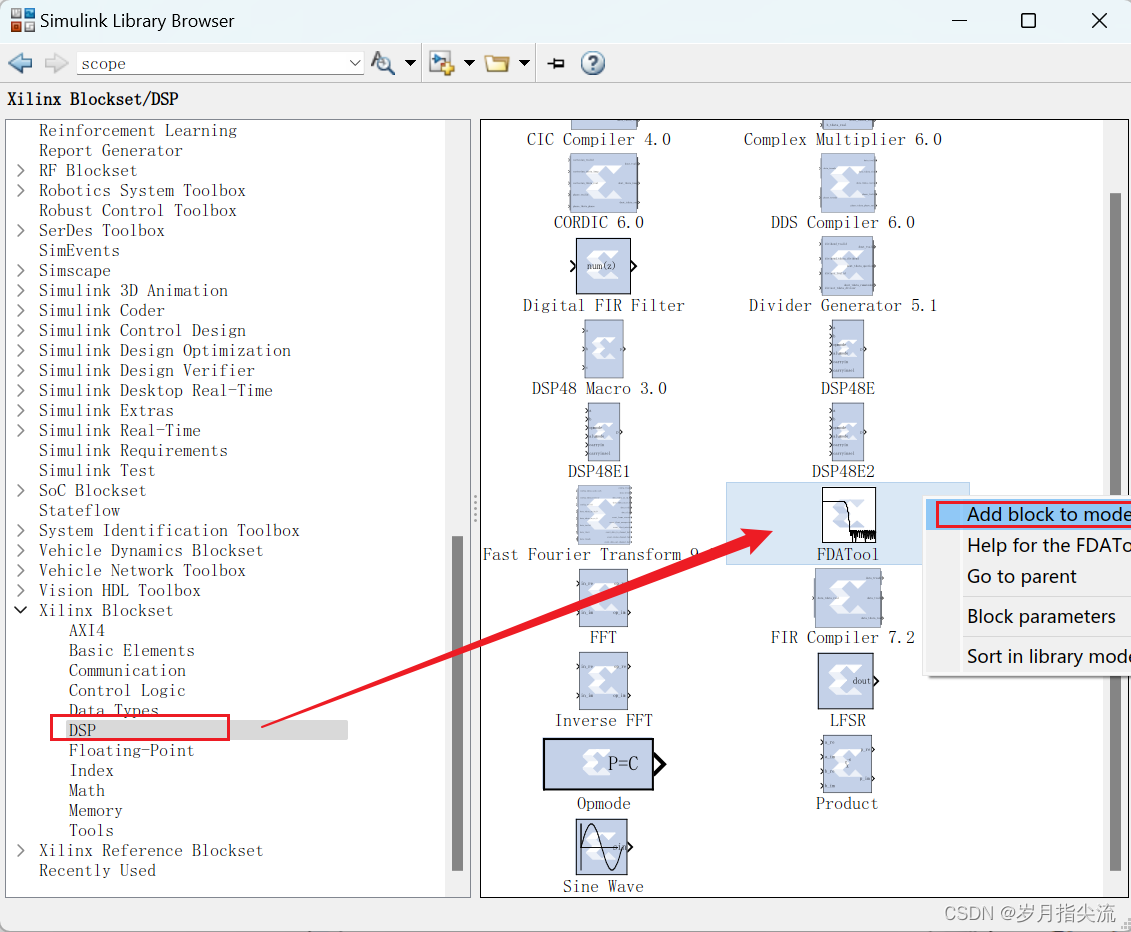

②、展开 Xilinx 模块组菜单,选择 DSP,然后选择数字 FIR 滤波器。右键单击数字 FIR 滤波器块,然后选择 Add 块对 Lab1_1 进行建模。

您可以通过访问块属性定义数字 FIR 滤波器块的滤波器系数——双击数字 FIR 滤波器块来查看这些——或者,在这种情况下,它们可以使用 FDATool 来定义。

③、在与上一步相同的 DSP 模块组中,选择 FDATool 并将其添加到 Lab1_1 设计中。

FPGA 设计需要定义三个重要方面:

- 输入端口

- 输出端口

- FPGA 技术

接下来的三个步骤将展示如何将这些属性中的每一个添加到 Simulink 设计中。

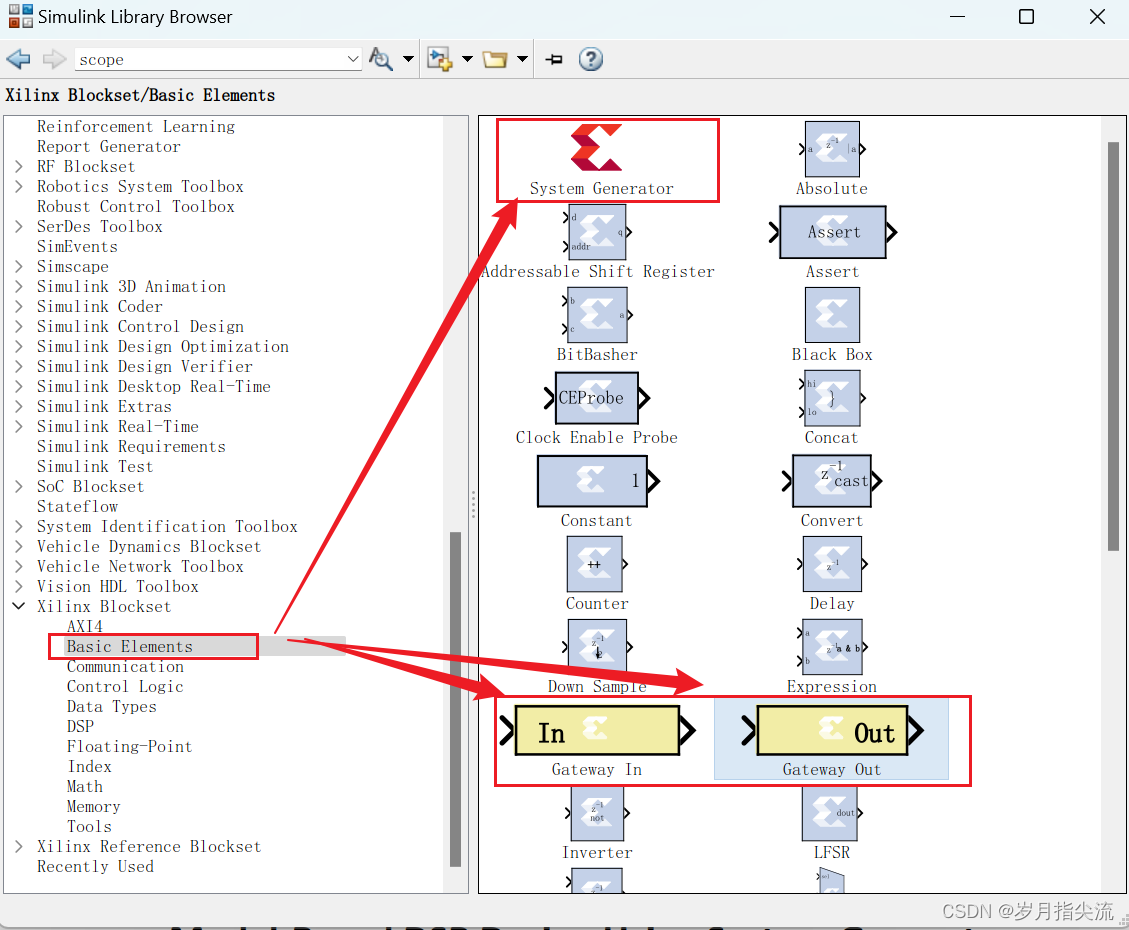

④、在 “基本元素” 菜单中,选择 “Gateway In”、“Gateway Out” 和 “System Generator” 并将其添加到设计中

⑤、复制一个现有的 Spectrum Analyzer 块,通过单击实例名称标签并编辑文本,将实例重命名为 Spectrum Analyzer SysGen。

⑥、如下图所示连接块。使用鼠标左键进行端口和网络之间的连接。

设计过程的下一部分是配置系统生成器块

<2>、配置系统生成器块

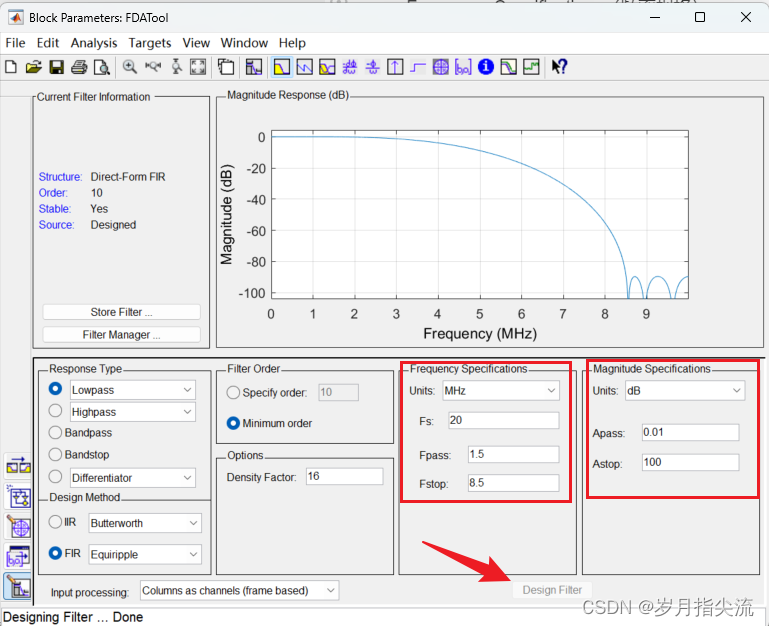

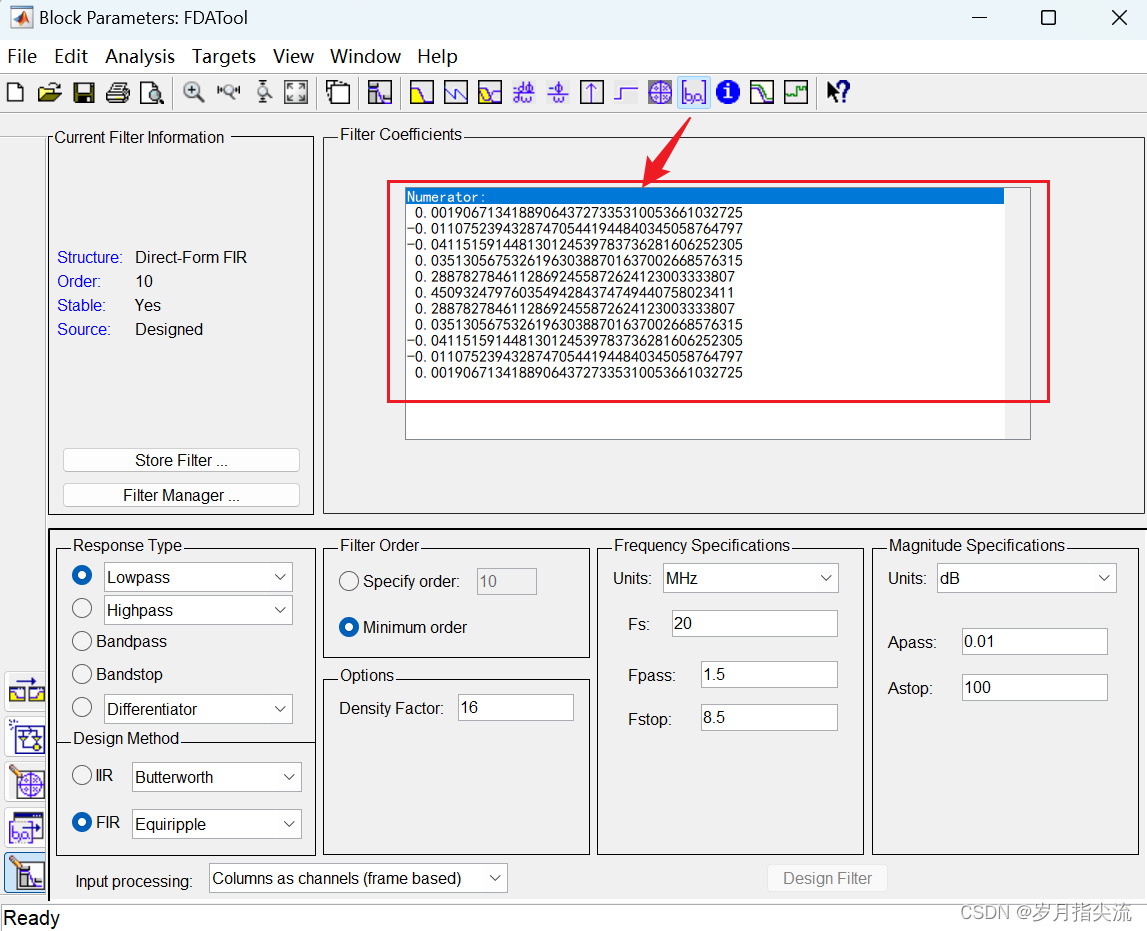

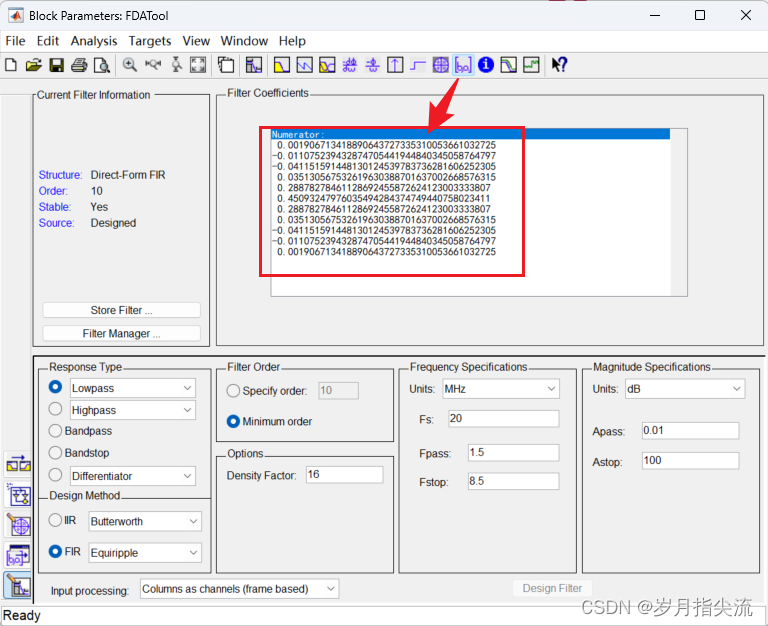

第一个任务是定义新滤波器的系数。对于此任务,您将使用 Xilinx 块版本的 FDATool。如果您打开现有的 FDATool 模块,您可以查看现有的频率和幅度规格。

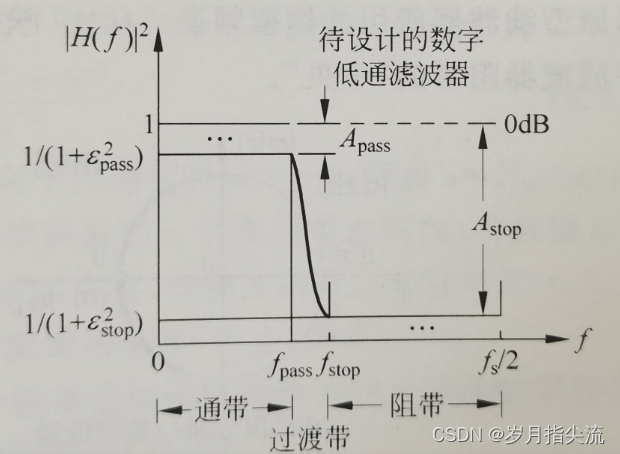

①、双击 FDATool 实例以打开属性编辑器,将过滤器规格调整为以下值 (如下图所示)

- Frequency Specifications(频率规格)

- Units = MHz

- Fs = 20

- Fpass(通带边界频率) = 1.5

- Fstop(阻带边界频率) = 8.5

- Magnitude Specifications(震级规格)

- Units = dB

- Apass(通带平坦度(通带衰减)) = 0.01

- Astop(阻带衰减) = 100

并点击 Design Filter

上图设计滤波器时调整的参数可以参考下图:

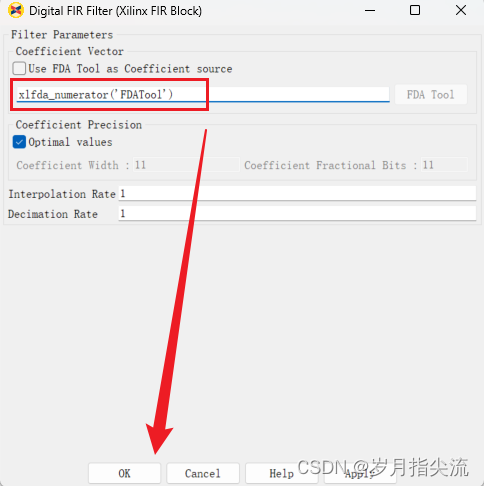

②、将 FDATool 实例的过滤器参数与 Digital FIR Filter 实例关联起来。

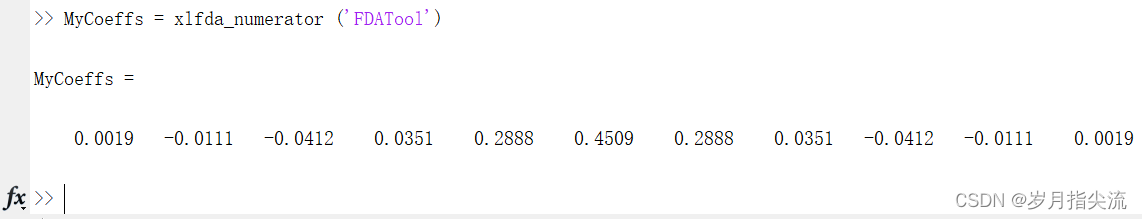

双击数字 FIR 过滤器实例打开属性编辑器,在 Filter Parameters 部分,用 xlfda_numerator(‘FDATool’) 替换现有的系数(系数向量),以使用 FDATool 实例定义的系数,单击 “确定” 退出 “数字FIR滤波器” 属性编辑器。

在 FPGA中,设计以特定的时钟速率工作,并使用特定数量的位来表示数据值。

标准 Simulink 环境中使用的连续时间和 FPGA 硬件环境中的离散时间之间的过渡是通过定义 “Gateway In” 块的采

样率来确定的。这决定了连续输入波形的采样频率。该采样率由 System Generator 自动传播到设计中的其他块。

以类似的方式,用于表示数据的位数在“Gateway In 块”中定义,也通过系统传播。

这两个属性(速率和位宽度)决定了表示连续时间信号的精确度。这两个属性也会对最终硬件的大小、性能和成本

产生影响。

System Generator 允许您使用 Simulink 环境来定义、仿真和检查这些属性的影响。

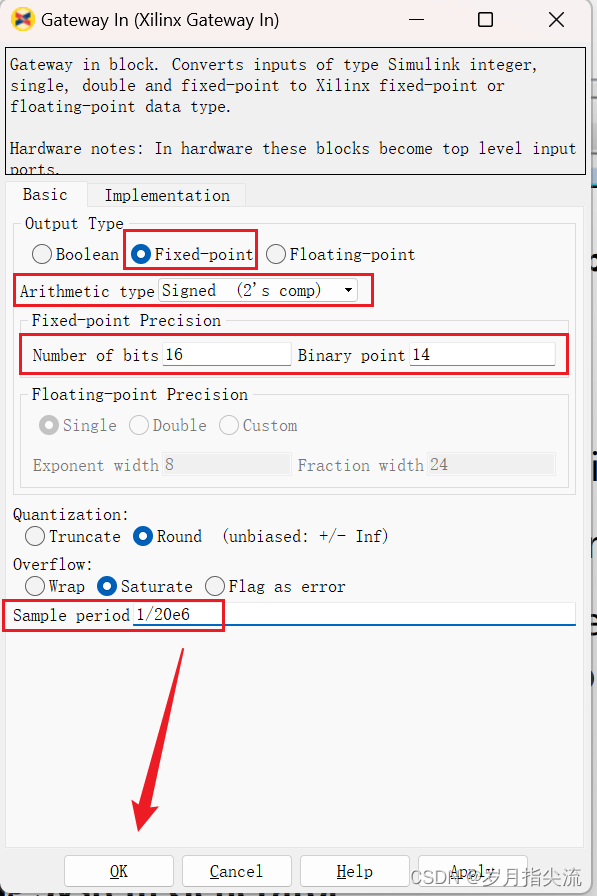

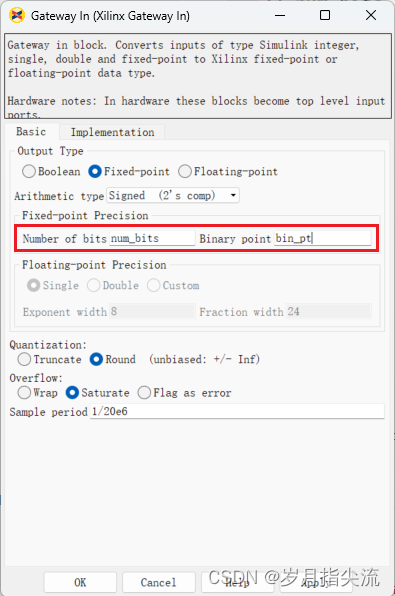

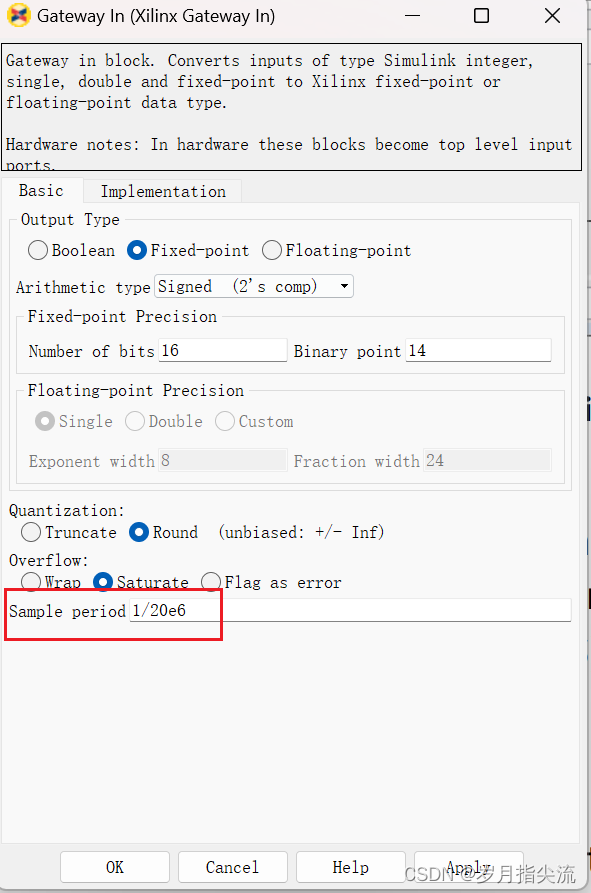

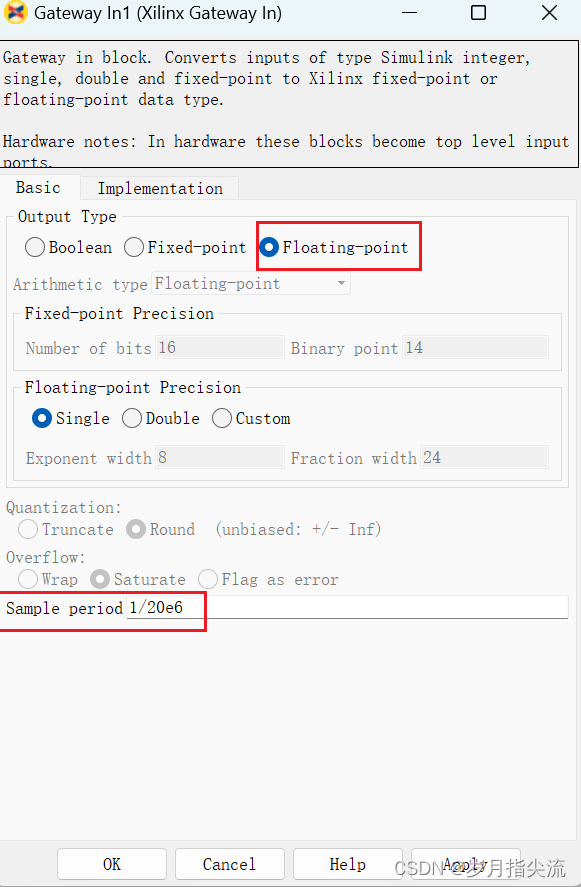

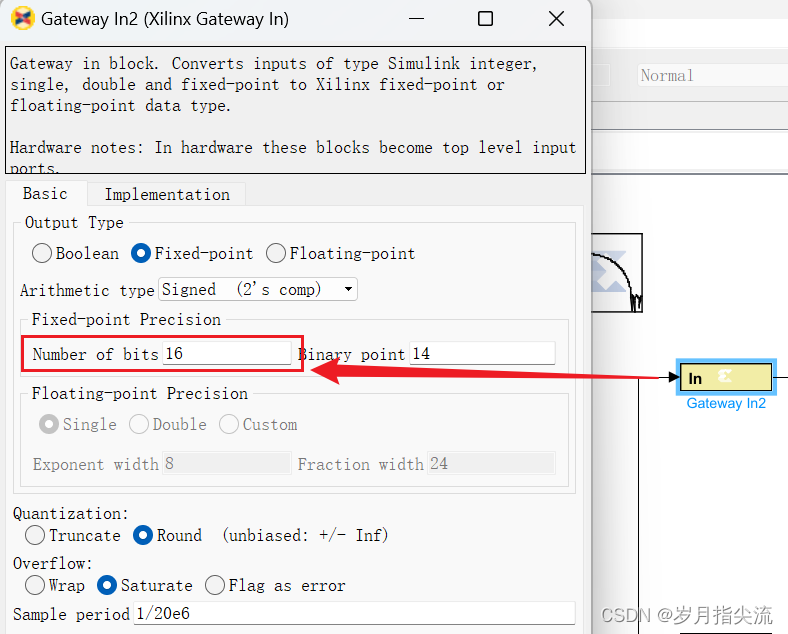

③、双击 Gateway In 块打开属性编辑器

由于设计中正弦波的最高频率为 9MHz,因此采样理论规定输入端口的采样频率必须至少为 18MHz。对于本设计,将使用 20MHz。在属性编辑器的底部,将采样周期设置为 1/20e6

现在,将位宽保留为默认定点 2 的补码 16 位,其中 14 位表示二进制点以下的数据。这使我们能够表示 -20 到 1.999的范围,这超过了正弦波(振幅均为1)求和所需的范围。

单击 “确定” 关闭 “Gateway In 块” 属性编辑器,这使我们现在能够使用精确的采样率和位宽来精确地验证硬件。

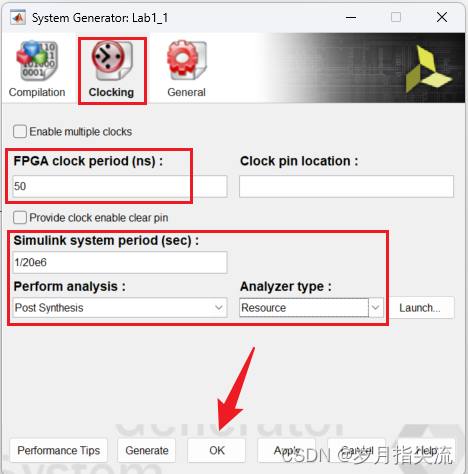

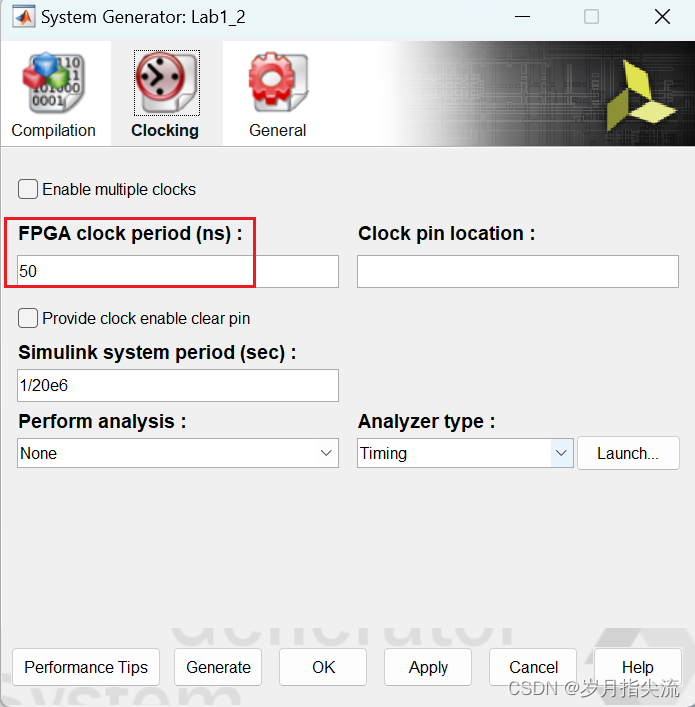

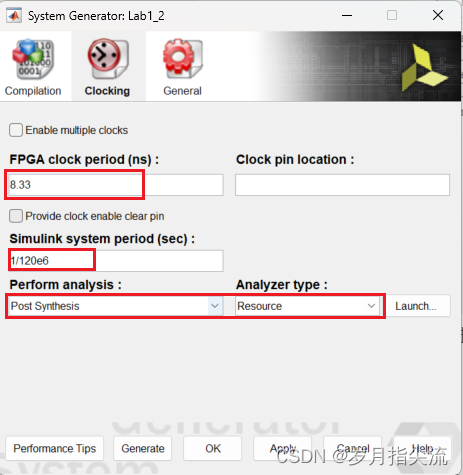

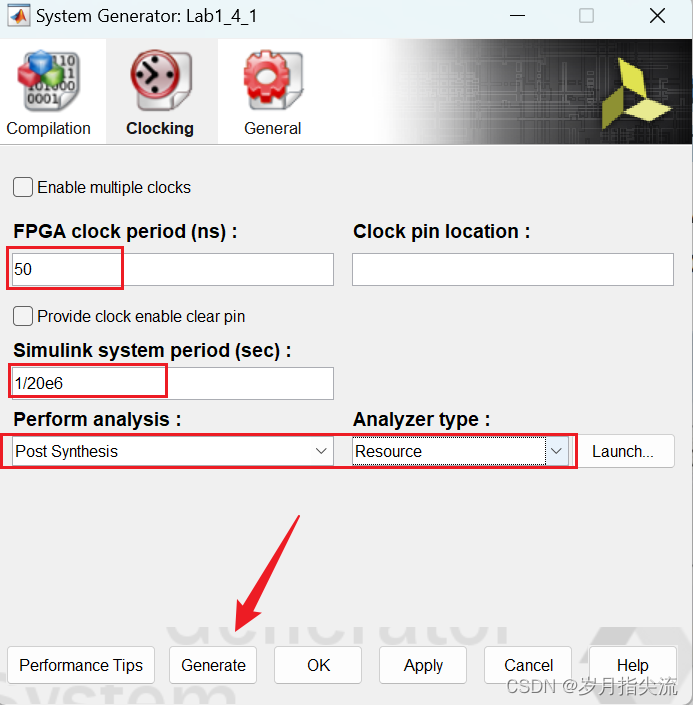

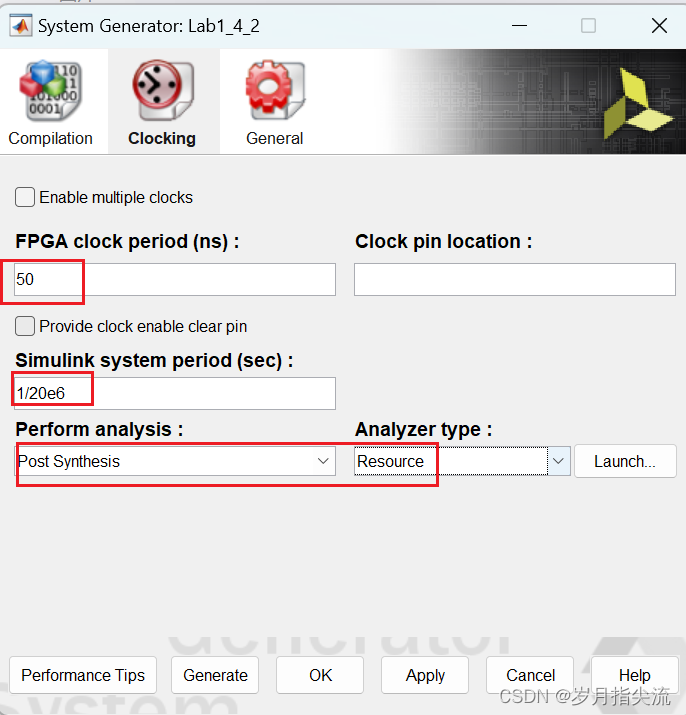

④、双击 System Generator 标记以打开属性编辑器。由于输入端口以 20MHz 采样以充分表示数据,因此必须将 FPGA 的时钟速率和 Simulink 采样周期定义为至少 20MHz。

选择时钟选项卡

- 设置 FPGA 时钟周期为 50ns (1/20 MHz)

- 指定 Simulink 系统周期为1/20e6 秒

- 从执行分析菜单中,选择合成后,从分析器类型菜单中选择资源,如下所示。此选项提供完成后的资源使用详细信息

单击 “确定” 退出系统生成器令牌

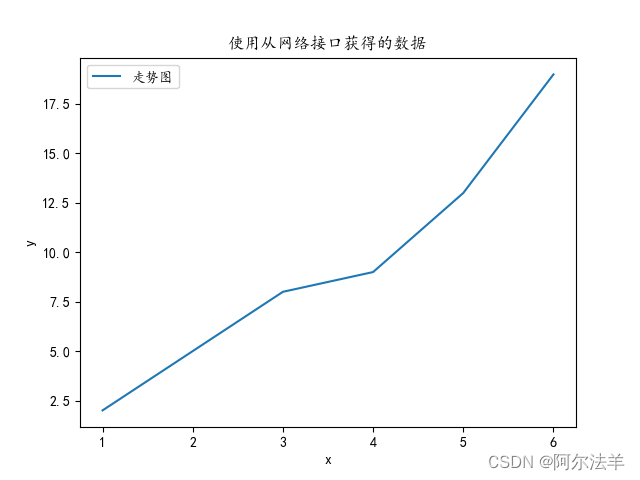

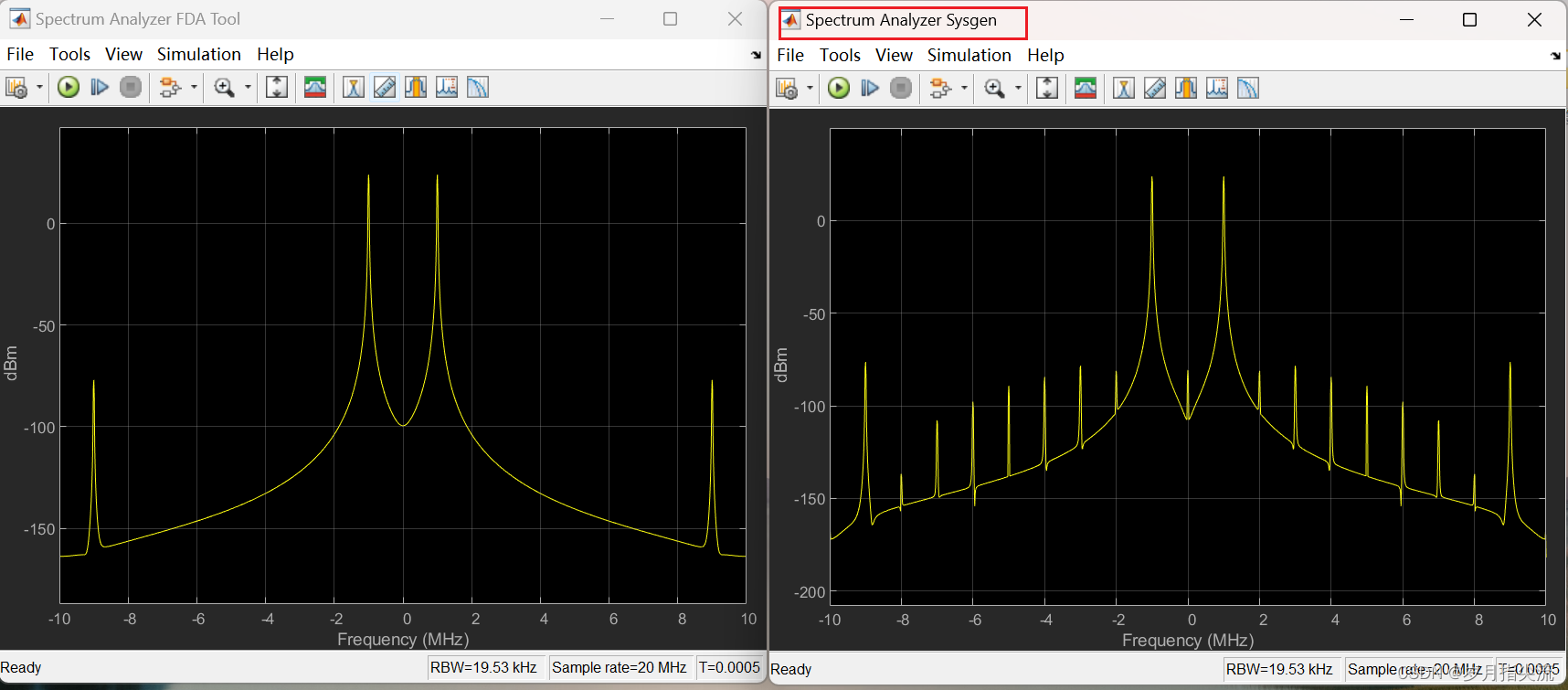

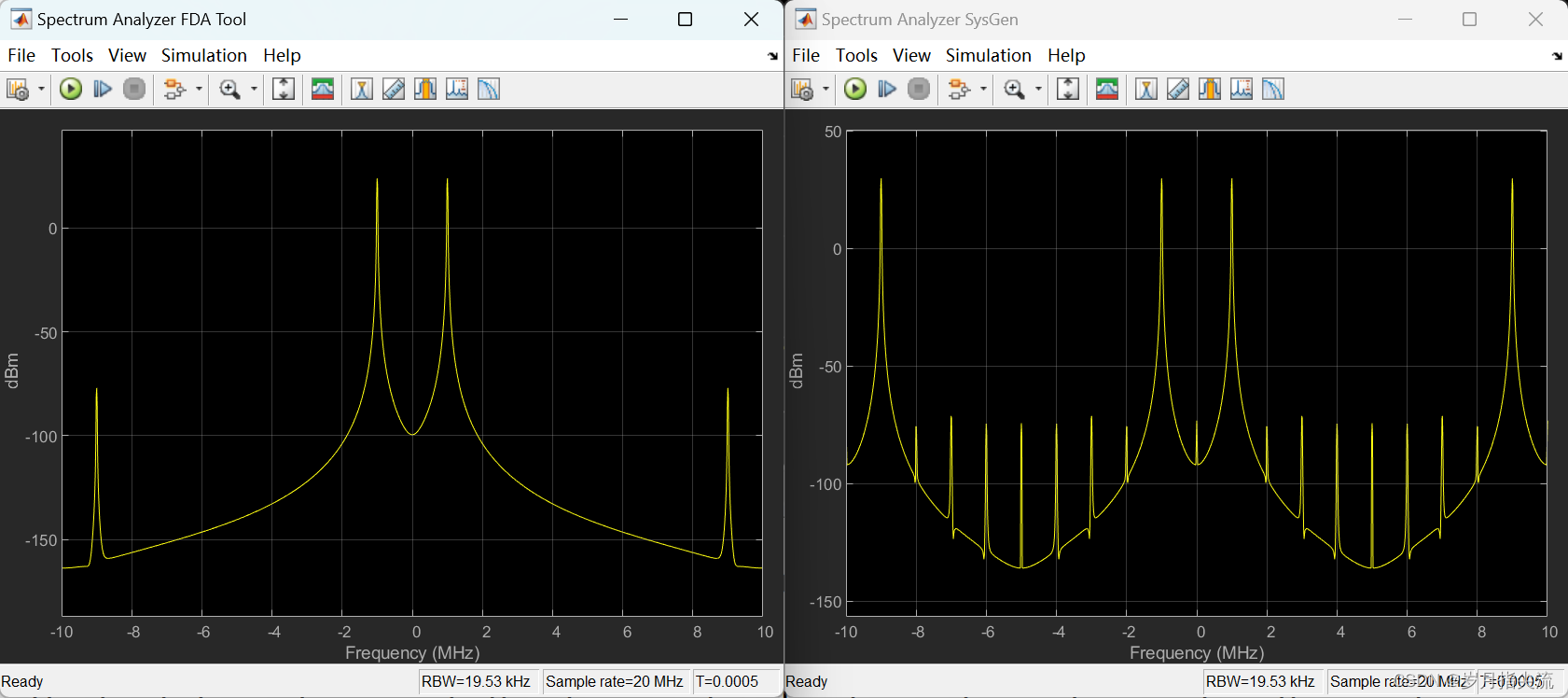

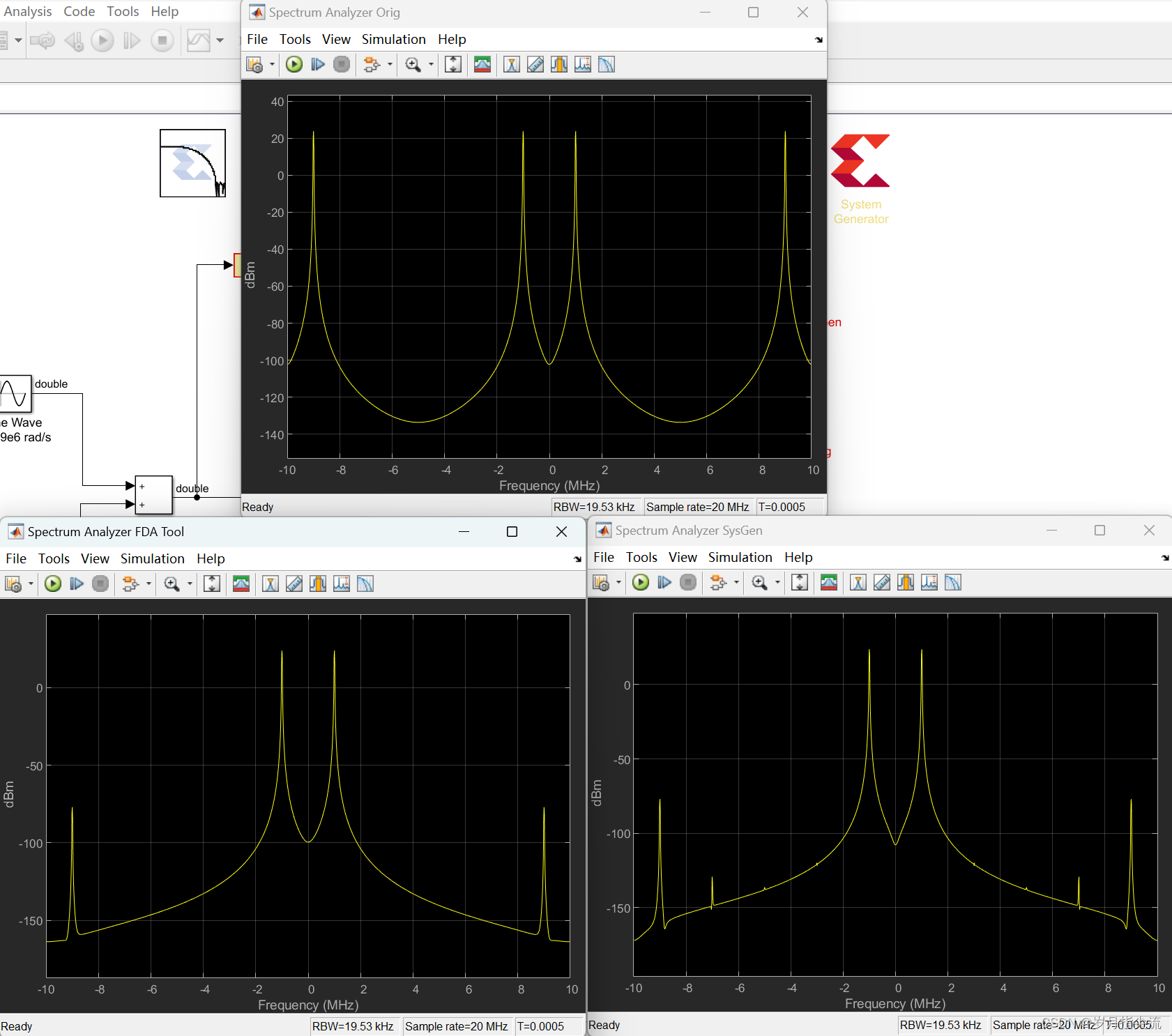

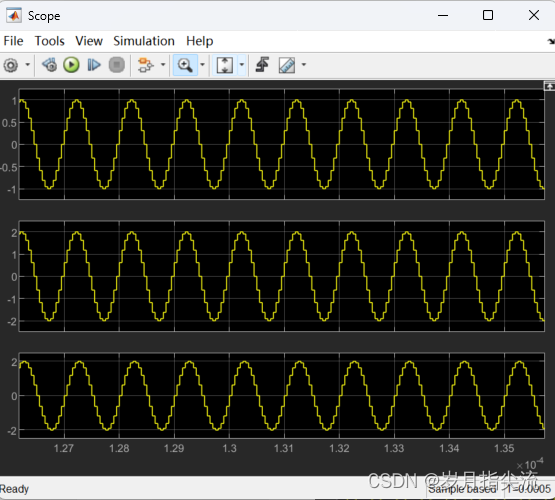

⑤、单击 Run simulation 按钮来模拟设计并查看结果,结果如下图

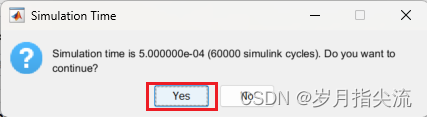

由于新的设计是周期和比特精确的,模拟可能需要比以前更长的时间来完成

结果如上所示,在右侧(在Spectrum Analyzer SysGen窗口中),与原始设计略有不同(在Spectrum Analyzer FDA Tool窗口中显示在左侧)。这是由于在离散时间硬件中描述连续时间系统时固有的量化和采样效应。

<3>、在 FPGA 上实现设计

最后一步是在硬件上实现这个设计。此过程将把 “Gateway In” 和 “Gateway Out” 块之间包含的所有内容合成为硬件描述。该设计描述以 Verilog 硬件描述语言(HDL)输出。此过程由 System Generator 令牌控制。

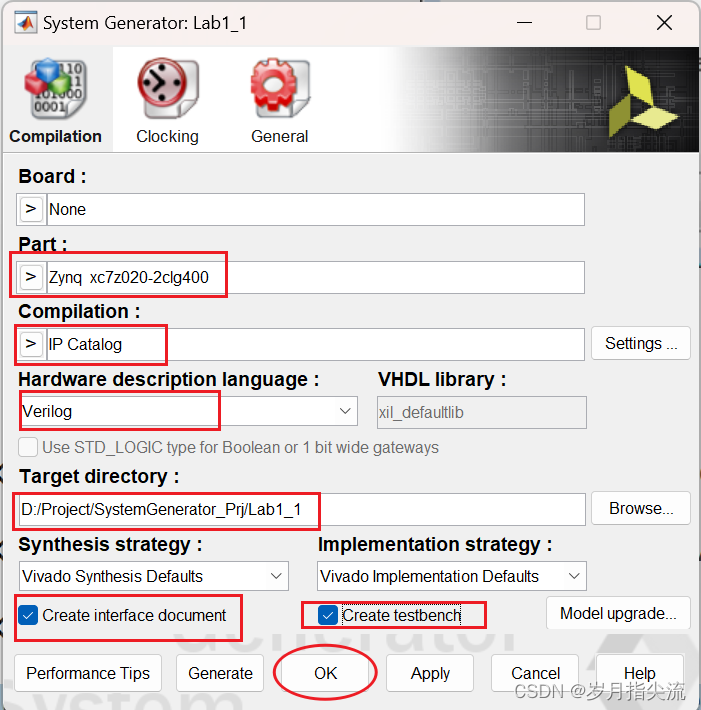

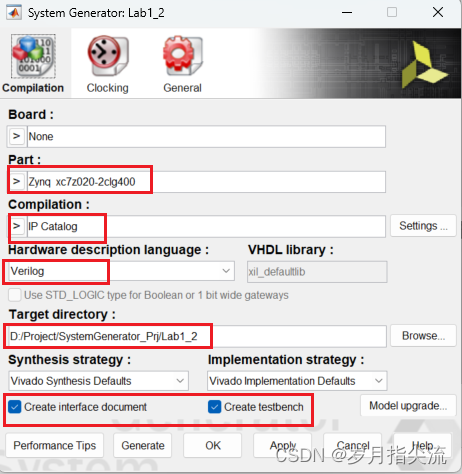

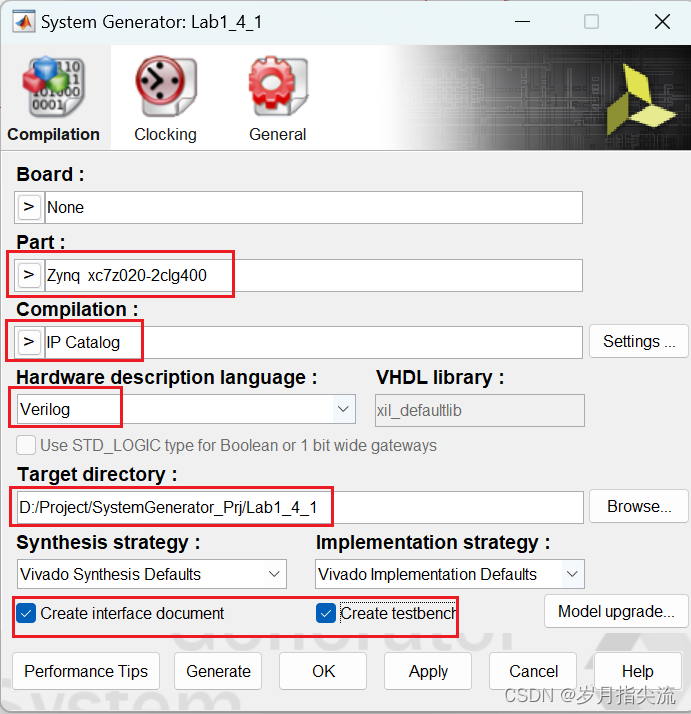

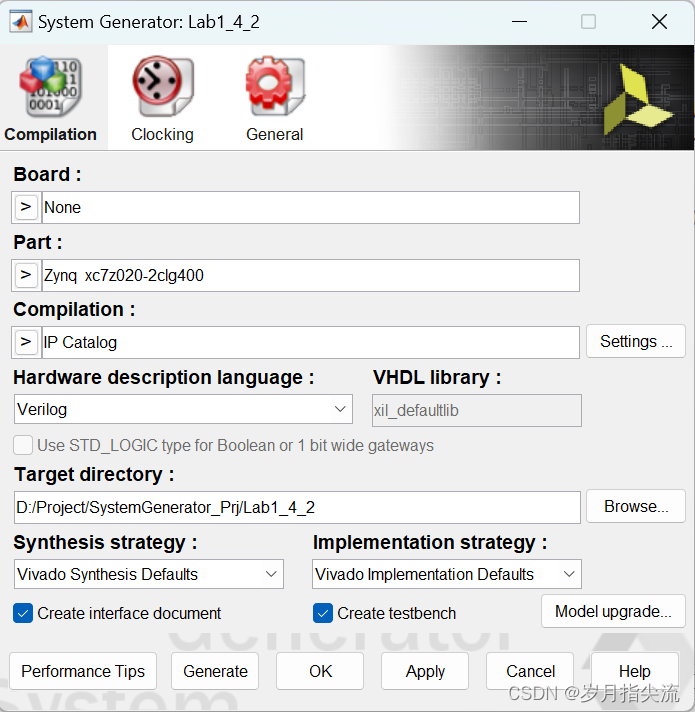

①、双击 System Generator 令牌以打开 Properties Editor,选择 Compilation 选项卡以指定有关设备和设计流的详细信息。从 Compilation 菜单中选择 IP Catalog 编译目标,以确保输出为 IP Catalog 格式。Part 菜单选择 FPGA 设备,我这里使用 zynq-7020 。使用默认的硬件描述语言 Verilog,目标生成目录自己定义。将创建接口文档和创建 testbench 选项勾选。

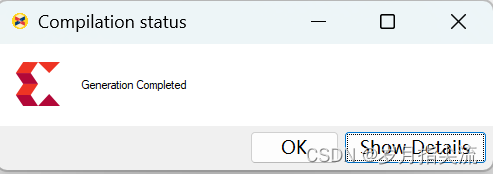

②、单击 Generate 将设计编译成硬件。编译过程将在 Simulink 块中捕获的设计转换为工业标准的 RTL(寄存器传输级)设计描述。RTL 设计可以综合成一个硬件设计。

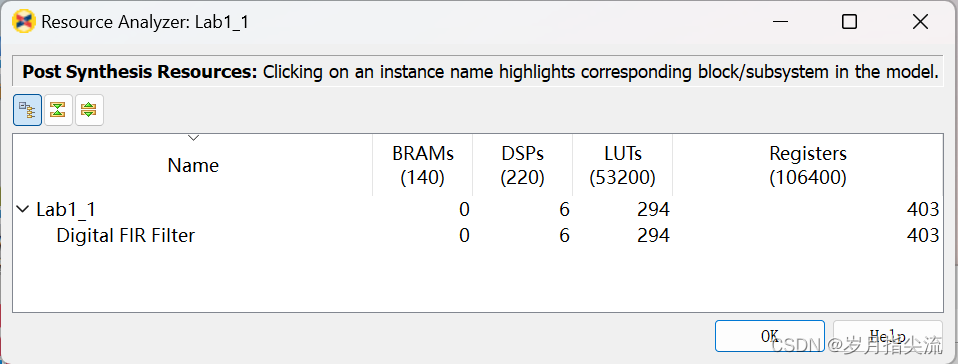

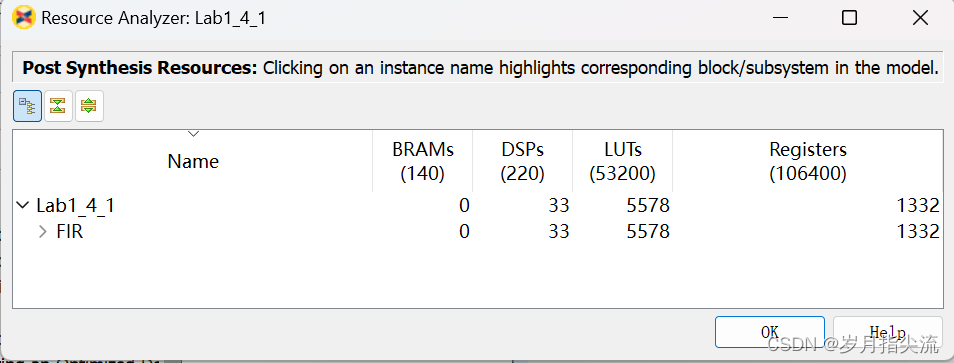

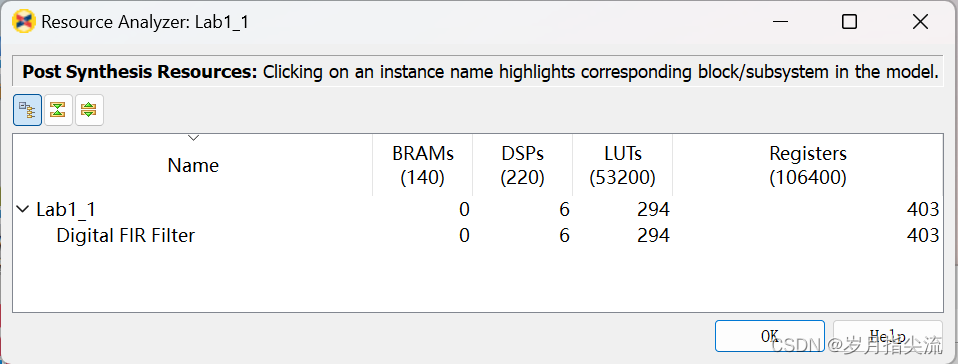

当硬件设计描述生成后,将出现 Resource Analyzer 窗口。

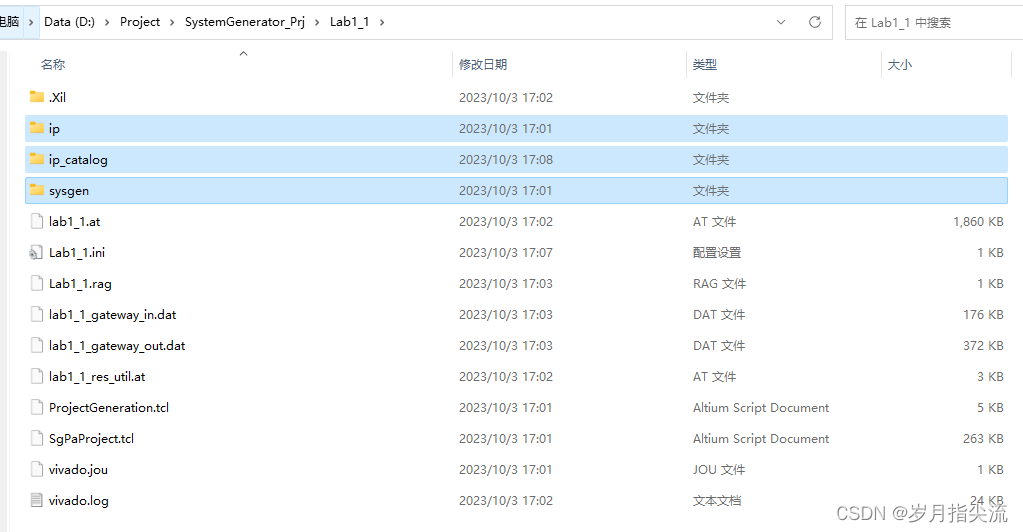

③、查看生成的工程文件

设计编译过程的输出写入 D:\Project\SystemGenerator_Prj\Lab1_1 目录。该目录包含三个子目录:

- sysgen:这包含了用工业标准 Verilog 格式编写的 RTL 设计描述。这是为希望查看详细结果的硬件设计经验丰富的用户提供的

- ip:该目录包含以 Xilinx IP Catalog 格式捕获的设计 IP,用于将设计传输到 Xilinx Vivado 设计套件中。实验5:使用AXI接口和IP集成商,在本文档后面介绍,详细解释如何将您的设计 IP 转移到 Vivado 设计套件中,以便在FPGA 中实现

- ip_catalog:此目录包含一个示例 Vivado 项目,其中已包含设计 IP。本项目仅作为快速分析的手段提供。上面的图显示了综合设计后所使用的资源的汇总。您还可以使用 ip_catalog 目录中的 Vivado 项目示例来查看硬件中的结果。

④、同时出现 “编译状态” 对话框,单击 OK 以关闭编译状态对话框

重要事项:ip_catalog 目录中提供的 Vivado 项目不包含顶级 I/O 缓冲区。综合结果为最终的设计结果提供了很好的估计,但是本项目的结果不能用来创建最终的 FPGA。

三、步骤 2:在 FPGA 中创建优化设计

在本步骤中,您将看到如何使用 FPGA 通过过采样来创建步骤1中使用的相同设计的更优化版本。您还将了解如何使用工作空间变量。

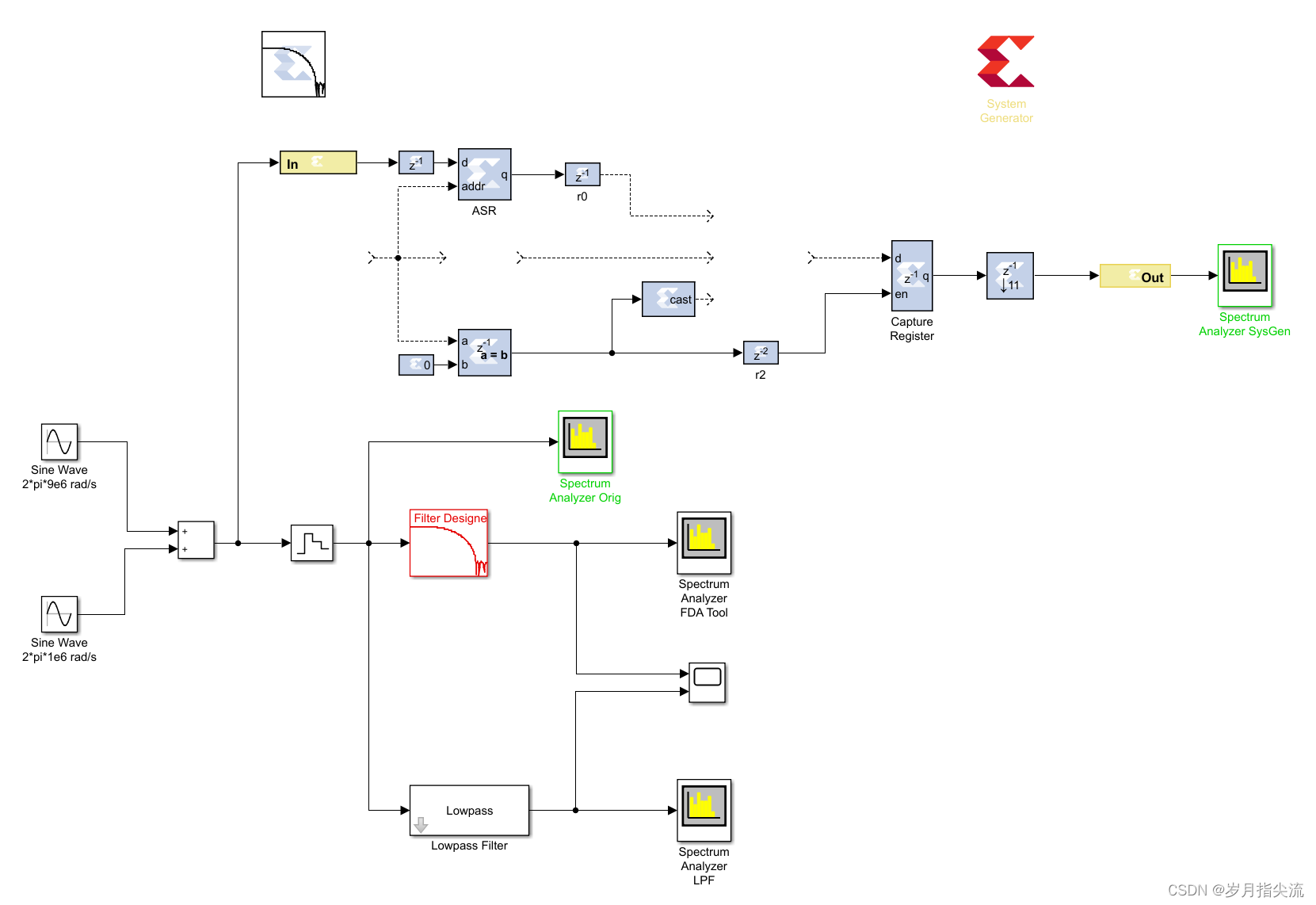

1、运行 Lab1_2.slx 文件

可以看到 Lab1_2.slx 与上面我们修改后的 Lab1_1.slx 是同样的设计,且运行结果也一模一样

2、进行优化设计

①、双击 System Generator 令牌以打开 Properties Editor。如第前面步骤 1 所述,该设计要求最小采样频率为18 MHz,目前设置为20 MHz(50 ns FPGA时钟周期)。

FPGA 器件的时钟频率很容易超过 20MHz。以更高的时钟频率运行 FPGA 将允许 System Generator 使用相同的硬件资源来计算多个中间结果。

②、双击 FDATool 实例打开属性编辑器,单击 Filter Coefficients 按钮查看过滤系数

这表明过滤器使用了 11 个对称系数。这将需要至少 6 次乘法。如步骤 1 Resource Analyzer 所示:Lab1_1 资源分析仪,其中最终硬件使用 6 个 DSP48 组件,用于执行乘法的 FPGA 资源。当前的设计以 20MHz 的速率对输入进行采样。如果输入以当前频率的 6 倍采样,则可以使用单个乘法器执行所有计算。

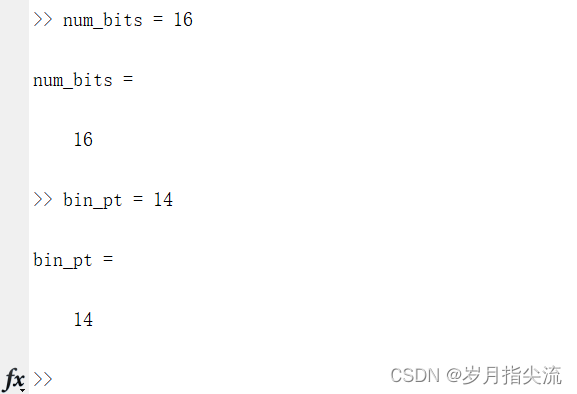

③、现在,将用工作空间变量替换此设计的一些属性。首先,需要定义一些工作空间变量

在 MATLAB 命令窗口中:

- 输入num_bits = 16

- 输入bin_pt = 14

④、在设计 Lab1_2 中,双击 Gateway In 块打开属性编辑器,在定点精度部分,将 16 替换为 num_bits,将 14 替换为 bin_pt,如下所示

单击 OK 保存并退出属性编辑器

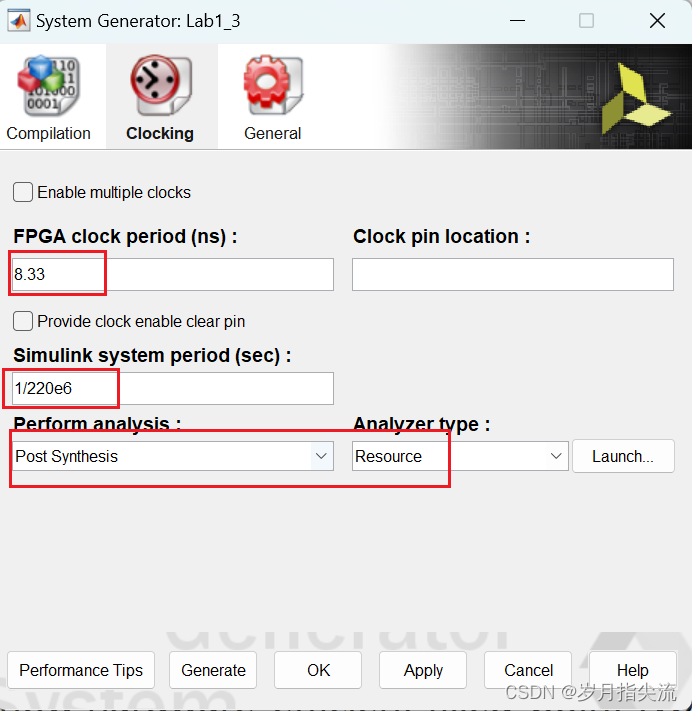

⑤、在 System Generator 令牌中,以这种方式将采样频率更新为 120 MHz(6 * 20 MHz)

- 设置 FPGA 时钟周期为 8.33 ns(1/120MHz)

- 指定 Simulink 系统周期为 1/120e6 秒

- 从执行分析菜单,选择合成后,从分析器类型菜单,选择资源如下所示。此选项提供完成后的资源使用详细信息

Compilation 按照下图配置

⑥、按 “生成” 将设计编译成硬件描述。在这种情况下,可以忽略 Diagnostic Viewer 中出现的消息,因为你有意将设计的时钟设置在采样率以上,以允许资源共享并减少资源。关闭“诊断查看器”窗口。

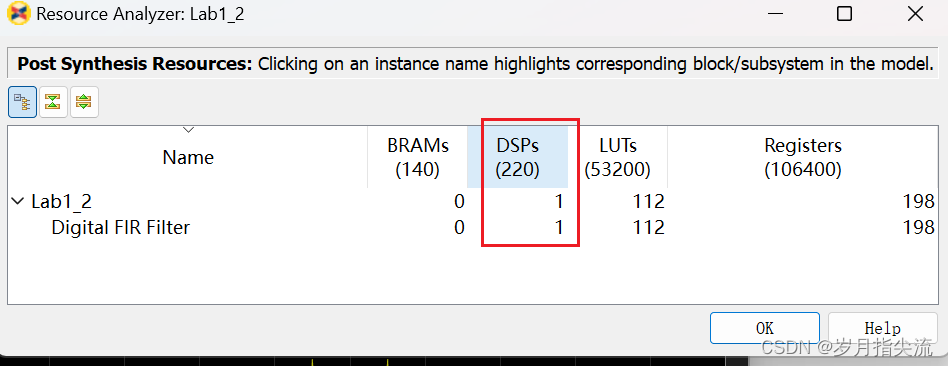

⑦、生成完成后,单击 OK 以关闭编译状态对话框。生成完成后,Resource Analyzer 窗口打开,可以很好地估计合成后的最终设计结果,如下所示

硬件设计现在只使用一个 DSP48 资源(一个乘法器),与上图 Lab 1_1 resource Analyzer 中的结果相比,使用的资源大约减少了一半

四、步骤 3:使用离散资源创建设计

在本步骤中,你将看到如何使用 System Generator 来构建使用离散组件的设计,以实现非常高效的硬件设计

1、运行 Lab1_3.slx 文件

这将打开如下图所示的 Simulink 设计。此设计与前两步中的设计类似。然而,这一次滤波器是用离散元件设计的,只是部分完成。作为此步骤的一部分,你将完成此设计并学习如何添加和配置离散部件。

这个离散滤波器就是这样工作的:

- 采样通过端口 In 到达,延迟后存储在移位寄存器(实例 ASR)中

- 滤波器系数需要一个 ROM

- 需要一个计数器来选择数据和系数样本进行计算

- 需要一个乘法累加单位来进行计算

- 最后的下采样单元每 n 个周期选择一个输出

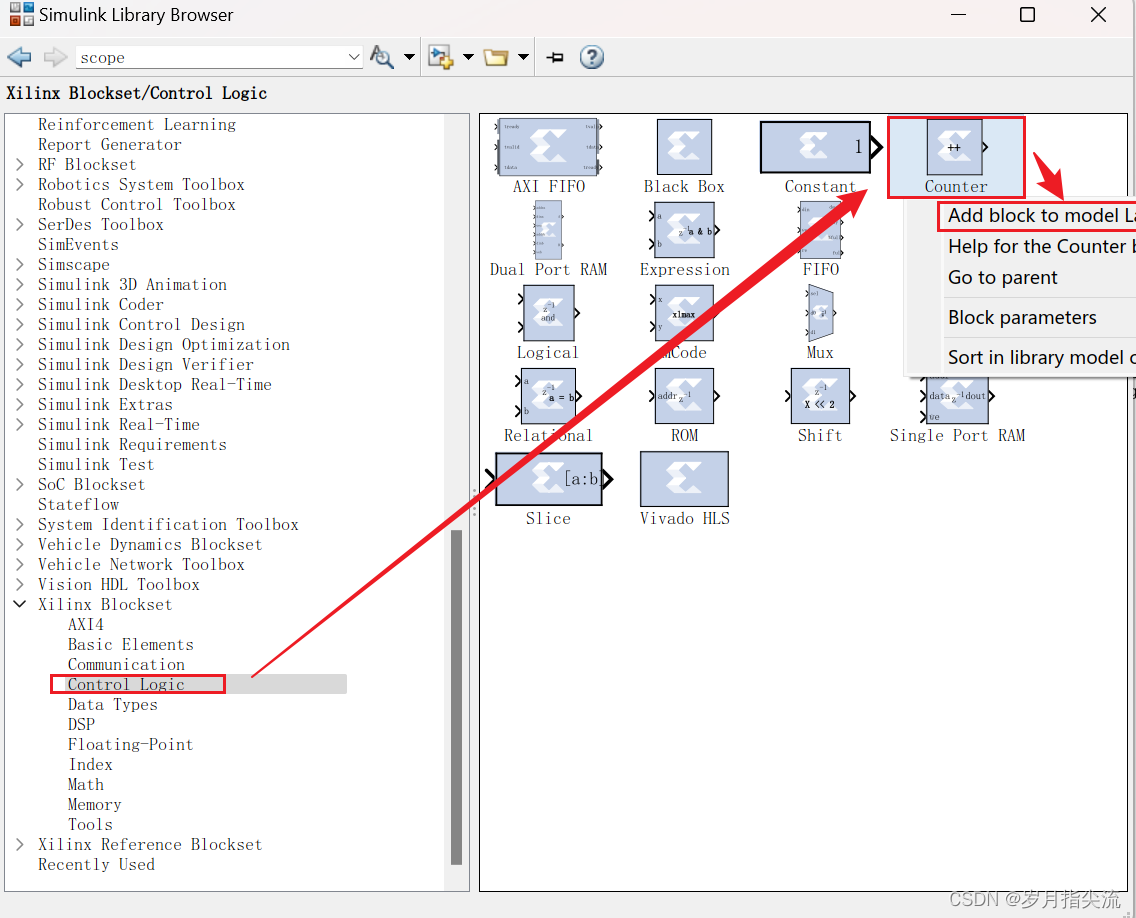

2、将分立组件添加到设计中

①、单击 Simulink 工具栏中的库浏览器按钮,打开 Simulink 库浏览器。

- a. 展开 Xilinx Blockset 菜单

- b. 如下图所示,选择 Control Logic 部分,然后选择 Counter 并用鼠标右键单击以将该组件添加到设计中

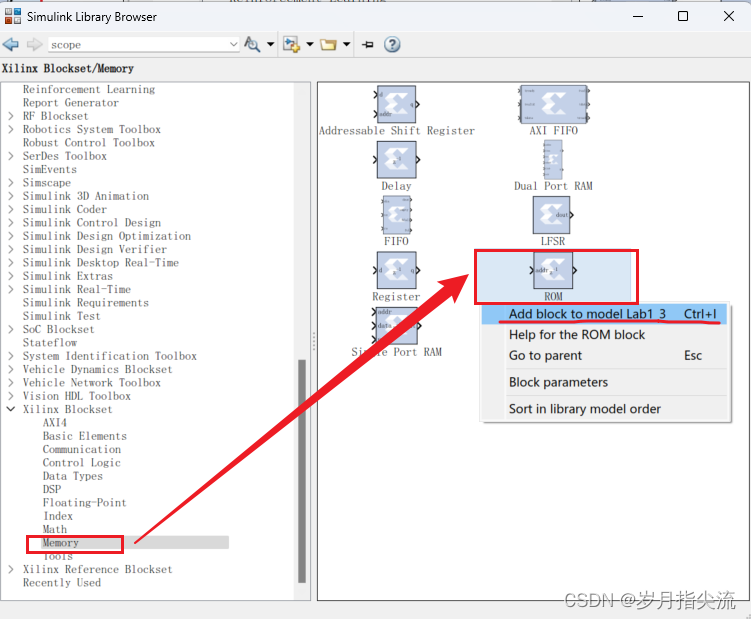

- c. 选择 Memory 部分(如图左下角所示),并在设计中添加一个 ROM

- d. 最后,选择 DSP 部分,并在设计中添加 DSP48 Macro 3.0

②、将三个新实例连接到设计的其余部分,如下所示

现在,将配置实例以正确过滤数据

③、双击 FDATool 实例并从工具栏中选择 Filter Coefficients 以查看过滤器规范

这显示了与步骤 1 中前面步骤相同的规格,并确认有 11 个系数。你还可以确认,通过双击输入网关,输入采样率再次为 20Mhz(采样周期= 1/20e6)。有了这些信息,您现在就可以配置离散组件了。关闭 FDATool 属性编辑器。

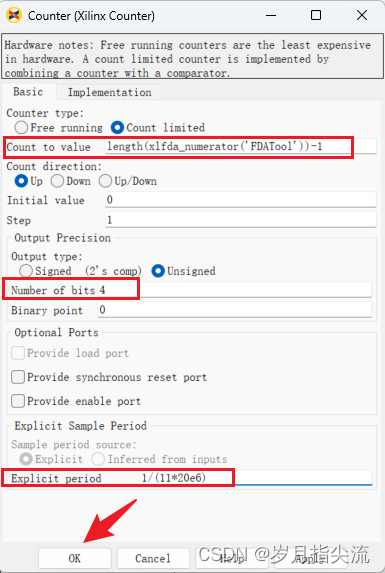

④、双击 Counter 实例打开属性编辑器

- a. 对于计数器类型,选择 Count limited 并为 Count 输入以下值:length(xlfda_numerator(‘FDATool’))-1,这将确保计数器计数从 0 到 10(11个系数和数据地址)

- b. 对于输出类型,将默认值保留为 Unsigned,并在位数中输入值 4。计数到 11 只需要 4 个二进制地址位

- c. 对于显式周期,请输入 1/(11*20e6),以确保采样周期为输入数据速率的 11 倍。滤波器必须为每个输入样本执行11次计算。点击 OK 退出属性编辑器。

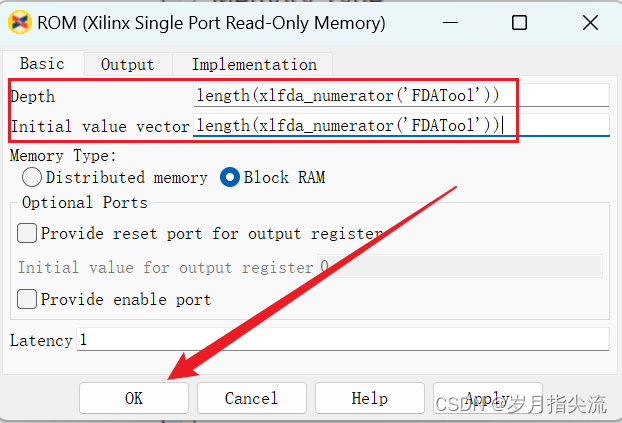

⑤、双击 ROM 实例打开 Properties Editor

- a. 对于 Depth,输入值 length(xlfda_numerator(‘FDATool’))。这将确保 ROM 有 11 个元素

- b. 对于初始值向量,输入:xlfda_numerator(‘FDATool’)。系数值将由 FDATool 实例提供

单击 OK 退出属性编辑器

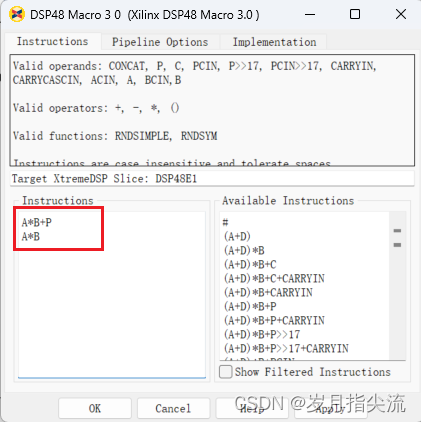

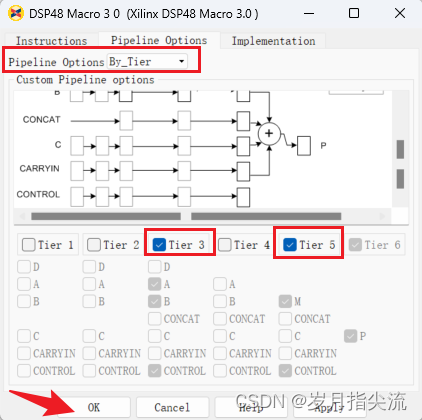

⑥、双击 DSP48 Macro 3.0 实例打开属性编辑器

- a. 在 “指令” 选项卡中,将现有的 “指令” 替换为 A*B+P,然后添加 A*B。当 sel 输入为假时,DSP48 将相乘并累加。当 sel 输入为真时,DSP48 将简单地相乘

- b. 在“管道选项”页签中,使用“管道选项”下拉菜单选择 By_Tier,选择分级 3 和分级 5。这将确保在 A 和 B 的输入处以及乘法和累加操作之间使用寄存器。单击 OK 退出属性编辑器

⑦、单击 Run simulation 按钮来模拟设计并查看结果,如下图所示

⑧、最后一步是将设计编译成硬件描述并进行综合

双击 System Generator 令牌以打开 Properties Editor,在 Compilation 选项卡中,确保编译目标是 IP Catalog

从时钟选项卡,在执行分析下选择后合成和分析器类型选择资源。此选项提供完成后的资源使用详细信息

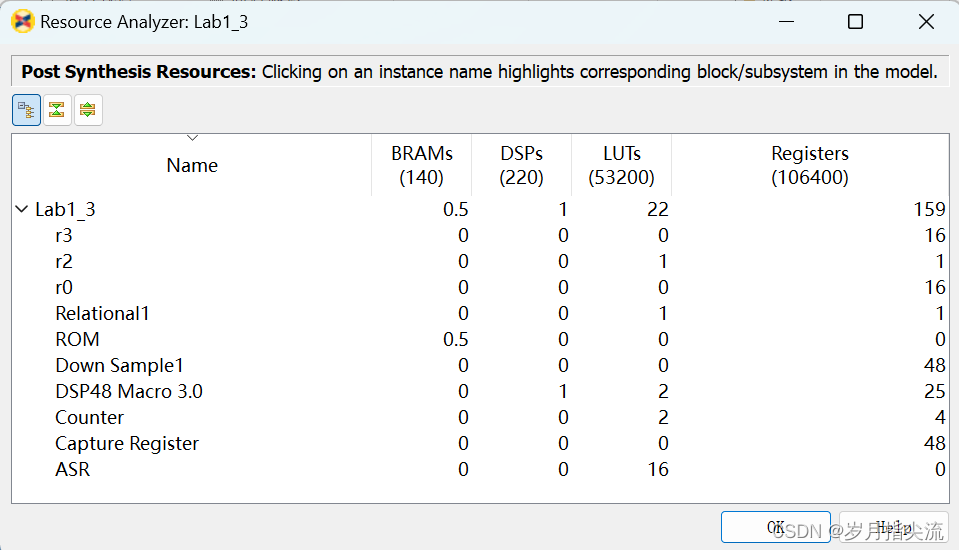

按 “生成” 将设计编译成硬件描述。生成完成后,在“资源分析器”窗口中显示资源利用率。

该设计现在使用的 FPGA 硬件资源比使用数字 FIR 滤波器宏设计的任何版本都少(Lab 1_1 资源分析仪 和Lab1_2资源分析仪 )。

单击 OK 以关闭 “资源分析器” 对话框

五、步骤 4:使用数据类型

在本步骤中,你将了解如何使用硬件高效的定点类型来创建满足所需规范但资源效率更高的设计,并了解如何使用 Xilinx Blocksets 来分析这些系统。这个练习有两个主要部分。

- 在第1部分中,将回顾并综合使用浮点数据类型的设计

- 在第2部分中,将使用作为定点实现捕获的相同设计,并细化数据类型,以创建满足相同需求的硬件高效设计

第 1 部分:使用浮点数据类型进行设计

<1>、打开 Lab1_4_1.slx 文件

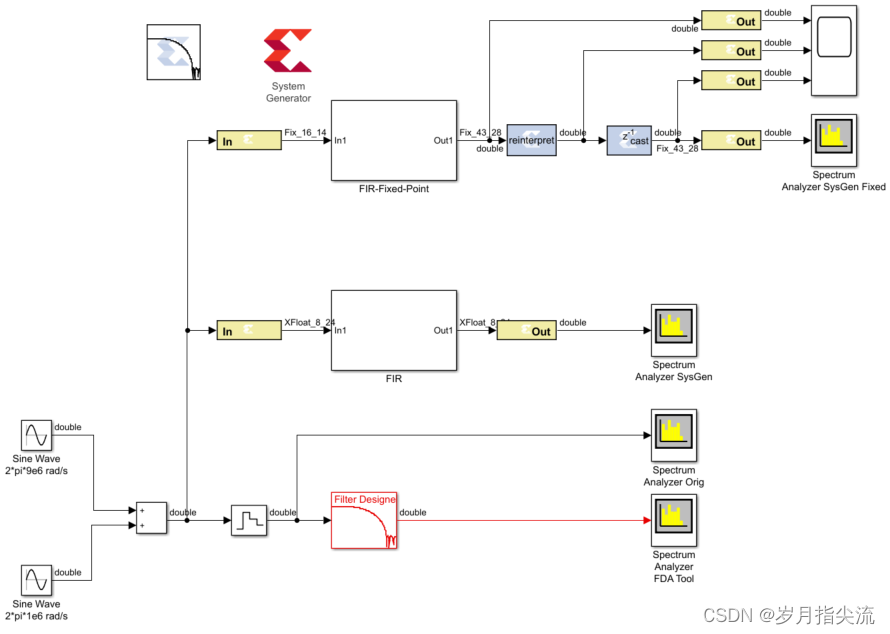

①、这将打开如下图所示的 Simulink 设计。该设计类似于 Lab 1_1 中使用的设计,但这次设计使用 float 数据类型,滤波器在子系统 FIR 中实现。首先,将审查设计的属性,然后模拟设计以审查性能,最后综合设计。

从上图可以看出,实例 FIR 的输入和输出都是 double 类型

<2>、配置及运行

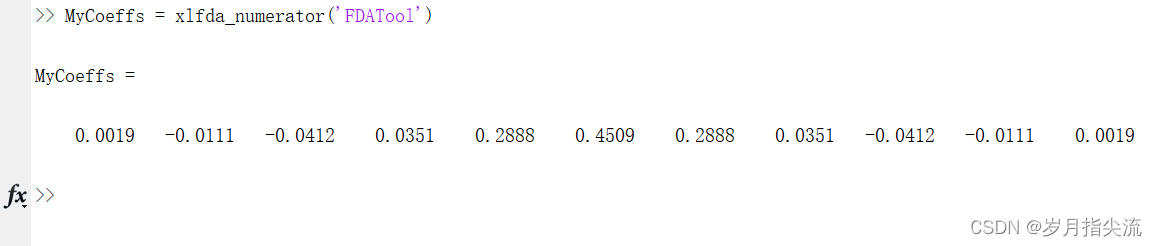

①、在 MATLAB 命令窗口中输入 MyCoeffs = xlfda_numerator(‘FDATool’)

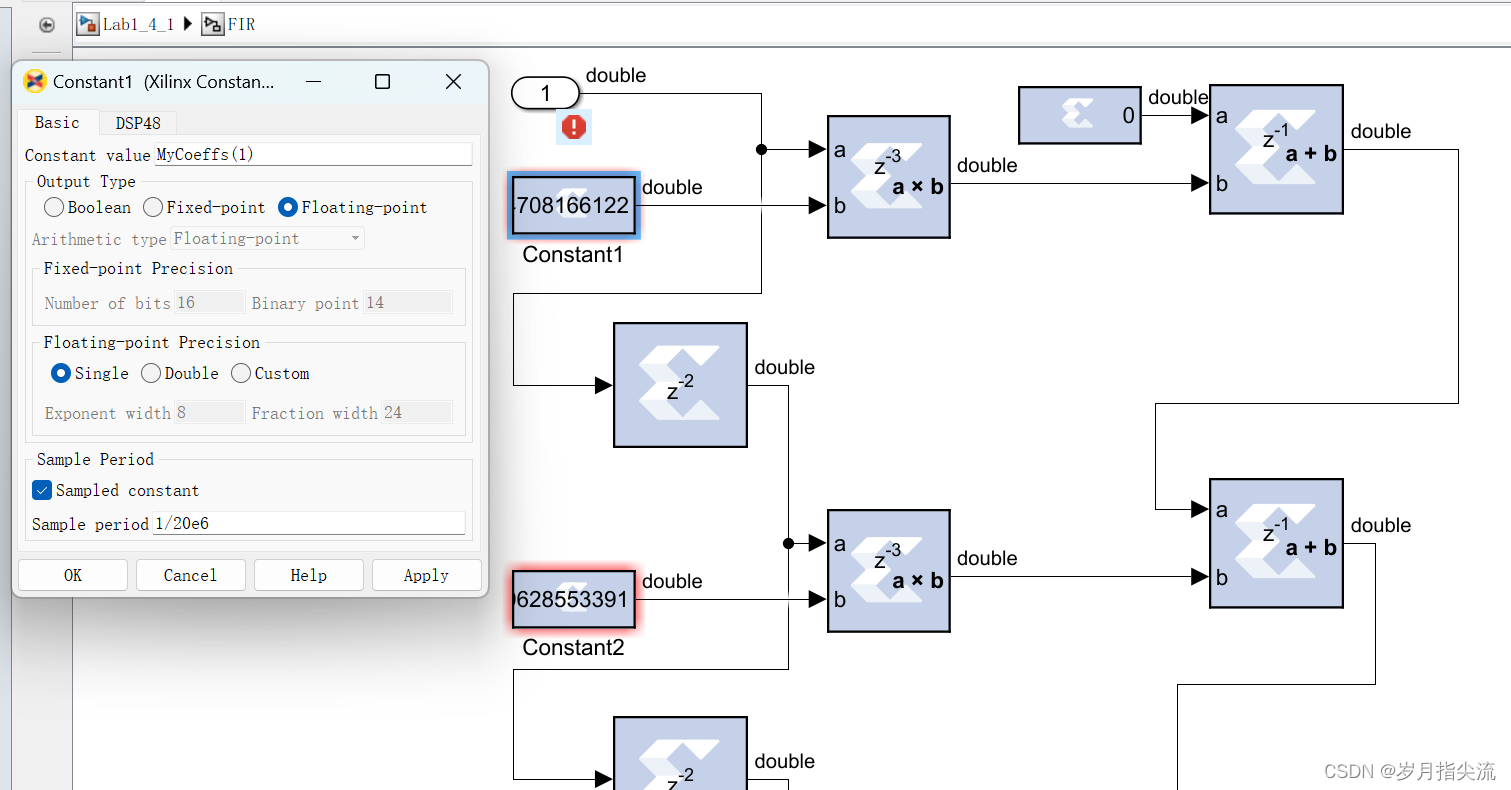

②、双击实例 FIR 打开子系统,双击实例 Constant1 以打开 Properties Editor。这表明常量值是由 MyCoeffs(1) 定义的。关闭 Constant1 Properties 编辑器

③、使用工具栏按钮 Up to Parent 返回到顶层设计。该设计将两个正弦波相加,都是 9 MHz。因此,系统发生器的输入网关必须以至少 18 MHz 的速率采样。双击 Gateway In1 实例打开属性编辑器,并确认输入以 20 MHz 的速率对数据进行采样(采样周期为 1/20e6)。关闭 Gateway In Properties 编辑器

④、按 Run simulation 按钮模拟设计。下面显示的结果显示,System Generator 块集产生的结果非常接近理想情况,如图所示。由于系统发生器设计必须将连续输入波形采样为离散时间值,因此结果并不相同。

最后一步是将这个设计合成为硬件

⑤、双击 System Generator 令牌以打开 Properties Editor,从编译菜单中,确保编译目标是 IP Catalog

从时钟菜单中,在执行分析下选择合成后,从分析器类型菜单中选择资源。此选项提供完成后的资源使用详细信息

⑥、按 “生成” 将设计编译成硬件描述。完成后,在 Resource Analyzer 窗口中生成资源利用率,如下所示

单击 OK 以关闭编译状态对话框

在 Lab 1 中使用定点数据类型实现了相同的过滤器。当与该实现的合成结果进行比较时,Lab 1 的初始结果如下图所示:Lab1_1 资源分析器结果

可以看到当前版本的设计使用了大量的寄存器(FF)、LUTs 和 DSP48(DSP)资源(Xilinx 专用乘法器/加法单元)

保持浮点类型的完全精度是一种理想的实现,但是实现完全的浮点精度需要大量的硬件。对于这种特殊的设计,不需要浮点类型的整个范围。该设计使用的资源远远超过所需的资源。在下一部分中,将学习如何在 Simulink 环境中比较具有不同数据类型的设计。

第 2 部分:定点数据类型设计

在本部分中,将使用定点数据类型重新实现第 1 部分:使用浮点数据类型进行设计中的设计,并将这个新设计与原始设计进行比较。本练习将演示使用定点类型的优点和缺点,以及System Generator如何允许你轻松比较设计,允许您在提交 FPGA 实现之前在 Simulink 环境中进行精度和资源之间的权衡

<1>、打开 Lab1_4_2.slx 文件

在此设计中,浮点实现与相同的定点设计一起被捕获。

<2>、配置及运行

①、在 MATLAB 命令窗口中输入 MyCoeffs = xlfda_numerator (‘FDATool’)

②、双击实例 Gateway In2 以确认将数据采样为 16 位定点值

③、点击运行仿真按钮模拟设计并确认实例 Spectrum Analyzer SysGen Fixed 显示过滤后的输出

如果检查实例 FIR-Fixed-Point 的输出,您将看到 System Generator 通过过滤器自动传播输入数据类型,并确定输出必须是 43 位(28 位二进制位)以保持信号的分辨率。这是基于通过过滤器的位增长和过滤器系数(实例 FIR-Fixed-Point 中的常量)为 16 位的事实。

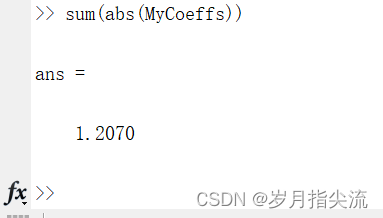

④、在 MATLAB 命令窗口中,输入sum(abs(MyCoeffs)) 以使用当前系数确定绝对最大增益

考虑到系数的正负值,最大增益可能是 1.2070,输出信号的幅度应该只比输入信号略小,输入信号是 16 位信号。不需要在二进制点以上有 15 位(43 - 28)的数据。现在,将使用 Reinterpret 和 Convert 块来操作定点数据,使其不大于精确结果所需的宽度,并产生最有效的硬件设计。

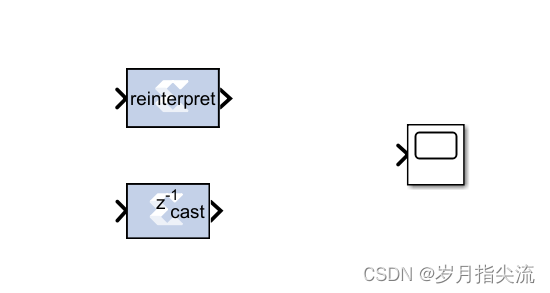

⑤、在画布的任意位置用鼠标右键单击并选择 Xilinx BlockAdd,在 “添加块” 输入框中,键入“Reinterpret”,双击 Reinterpret 组件,将其添加到设计中

对这些组件重复上述三个步骤:

- a. Convert

- b. Scope

⑥、在设计中,选择 Gateway Out2 实例

- a. 右键单击并使用 Copy and Paste 来创建 Gateway Out 块的新实例

- b. 再次粘贴两次,以创建 Gateway Out 的另外两个实例(总共三个新实例)

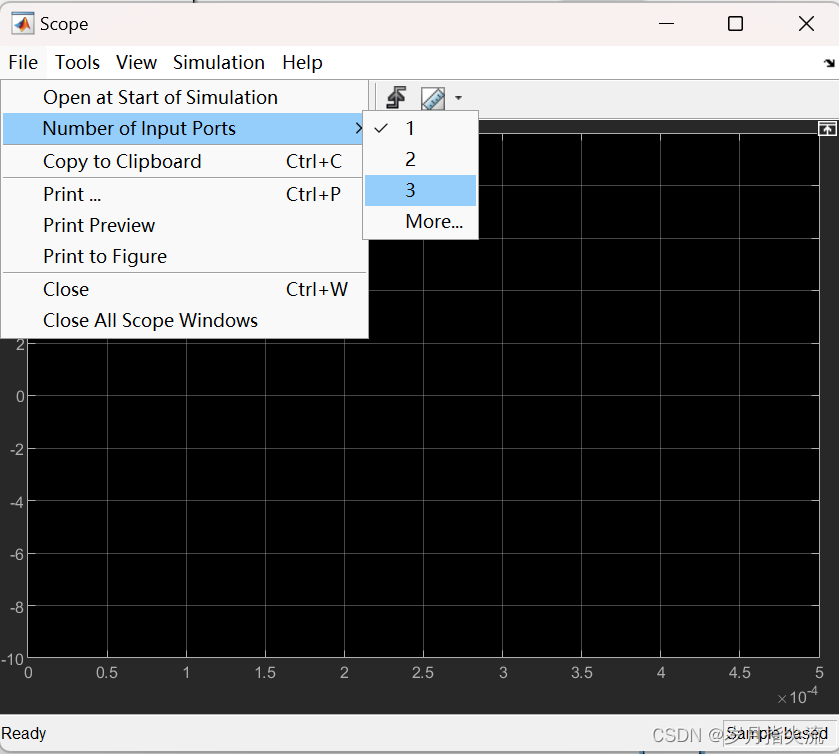

⑦、双击 Scope 组件,在“作用域属性”对话框中,选择文件 -> 输入端口数:3

⑧、连接块如下图所示

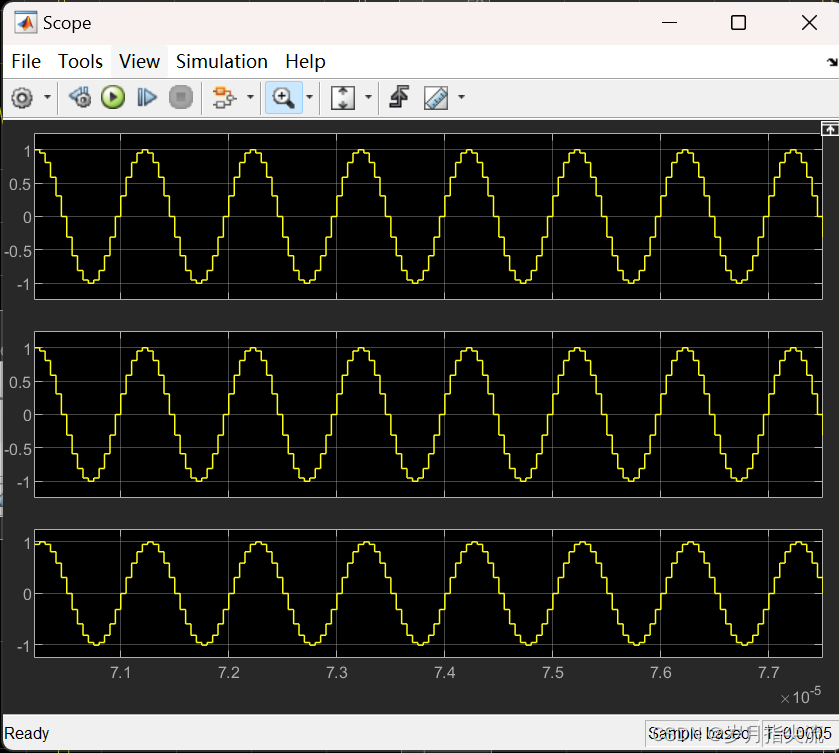

⑨、单击 Run simulation 按钮来模拟设计,双击 Scope 以检查信号

此时还没有配置 Reinterpret 和 Convert 块,因此所有三个信号都是相同的。Xilinx Reinterpret 块将其输出强制为新类型,而不考虑保留输入所表示的数值。该块允许将无符号数据重新解释为有符号数据,或者相反,将有符号数据重新解释为无符号数据。它还允许通过重新定位数据中的二进制点来重新解释数据的缩放。

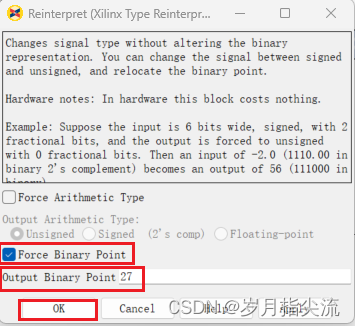

在本练习中,你将把数据按 2 倍缩放,以模拟可能在更大的系统中出现的额外设计处理。Reinterpret 块也可以用于缩小。

⑩、双击 Reinterpret 块打开属性编辑器,选择 Force Binary Point,在输入字段 Output Binary Point 中输入值 27,然后单击 OK

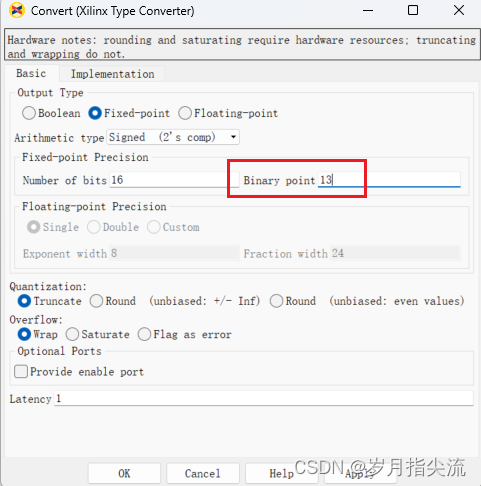

Xilinx Convert 块将每个输入样本转换为所需算术类型的数字。例如,可以将数字转换为有符号(2的补码)或无符号值。它还允许对信号量化进行截断或舍入,并对信号溢出进行包装、饱和或标记为错误。在本练习中,将使用Convert 块将 43 位字的大小减小到 16 位值。在这个练习中,Reinterpret 块被用来模拟一个更复杂的设计,并将数据按 2 倍缩放。因此,您必须确保输出在二进制点以上有足够的位来表示这种增加。

⑪、双击 Convert 块打开属性编辑器,在定点精度部分,输入13 作为二进制点,然后单击 OK

⑫、单击 Run simulation 按钮来模拟设计,双击 Scope 以检查信号

在上面的图中,您可以看到过滤器(Growth)的输出值在正负 1 之间。Reinterpret 块的输出将数据值移动到正负 2 之间。在这个波形的详细视图中,与重新解释结果相比,最终输出(Convert)显示保真度没有差异,但仅使用16位

最后一步是将这个设计合成为硬件

⑬、双击 System Generator 令牌以打开 Properties Editor,从编译菜单中,确保编译目标是 IP Catalog。

从时钟菜单中,在执行分析下选择合成后,从分析器类型菜单中选择资源。此选项提供完成后的资源使用详细信息

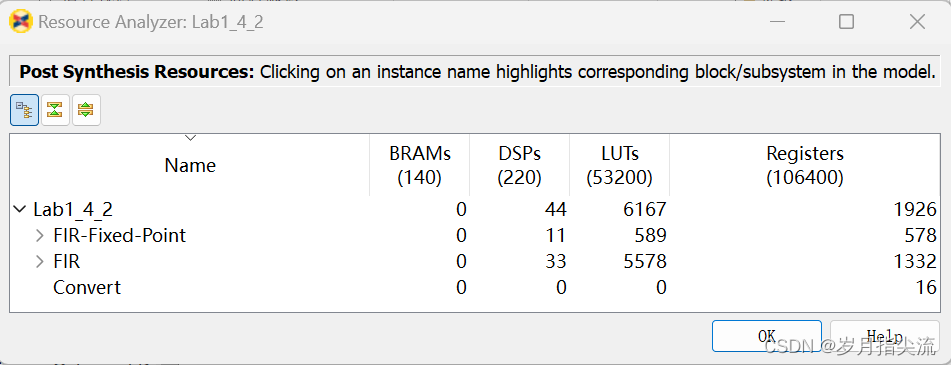

⑭、单击 Generate 将设计编译成硬件描述。完成后,在 Resource Analyzer 窗口中生成资源利用率,如下所示

注意,与步骤 1 中的结果相比(Lab1_1资源分析仪结果),这些结果显示近似:

- Flip-Flops 增加 45%

- LUTs 增加 20%

- DSP48s 增加 30%

⑮、单击 OK 以关闭编译状态对话框

总结

在本节,您学习了如何使用 System Generator 块集在 Simulink 环境中创建设计,并将设计综合到可以在 Xilinx FPGA 上实现的硬件中。你了解了使用 Xilinx 数字 FIR 滤波器块快速创建设计的好处,以及如何通过使用过采样来改进设计。

你还了解了浮点类型如何提供高度的准确性,但在 FPGA 中实现要花费更多的资源,以及如何使用 System Generator 块集来实现使用更有效的定点数据类型的设计,并补偿使用定点类型造成的任何准确性损失。

Reinterpret 和 Convert 块是功能强大的工具,允许您优化设计,而无需执行详细的位级优化。您可以简单地使用这些块在不同的数据类型之间进行转换,并快速分析结果。最后,您了解了如何通过使用离散原语完全控制硬件实现。

我的qq:2442391036,欢迎交流!