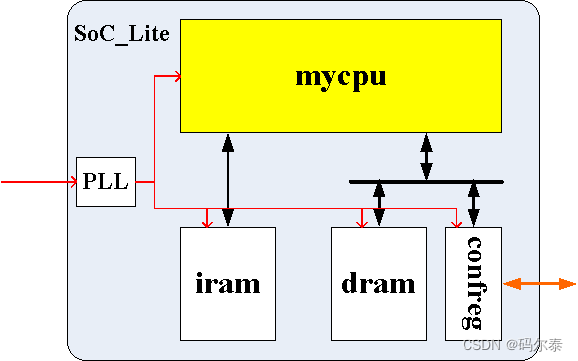

1 SoC_Lite片上系统结构

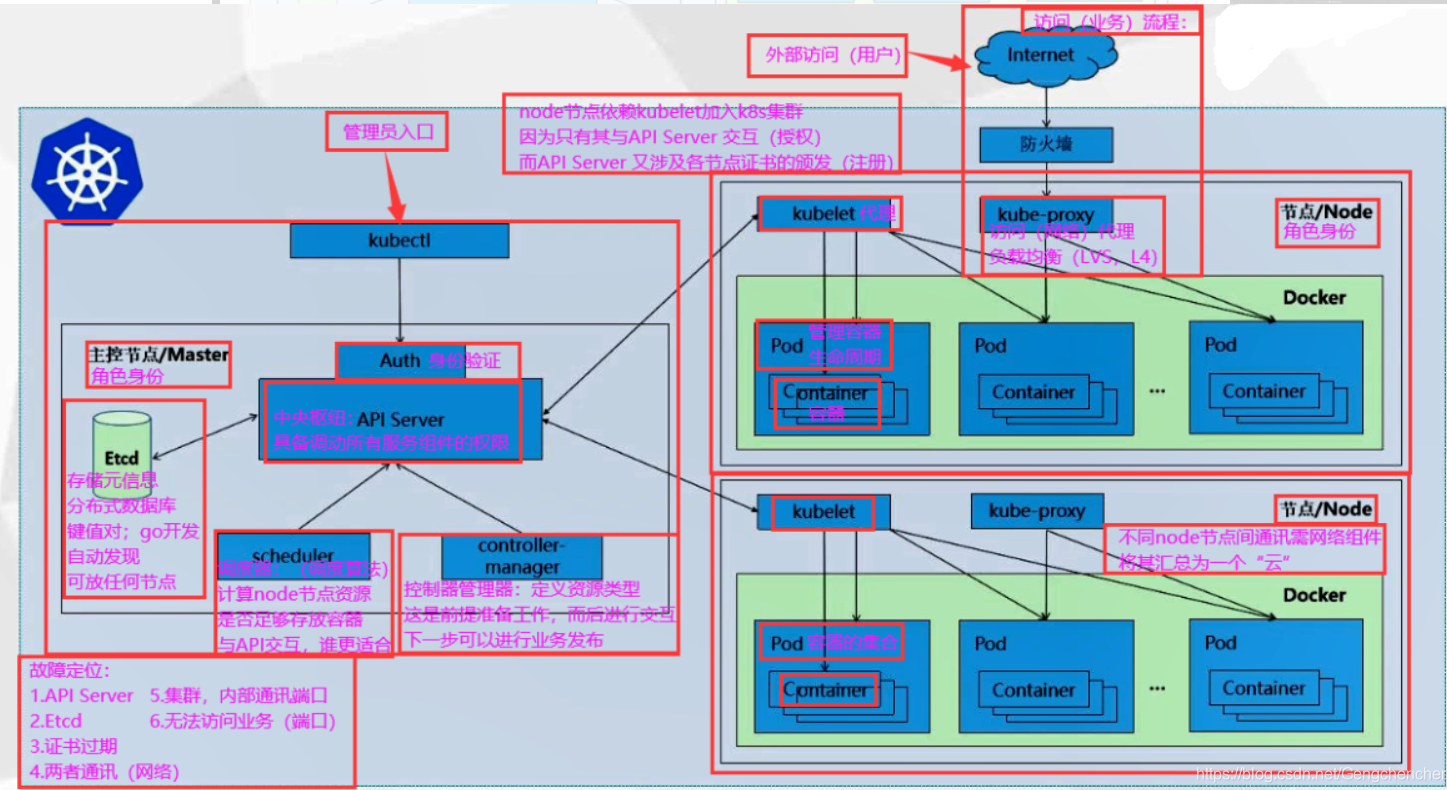

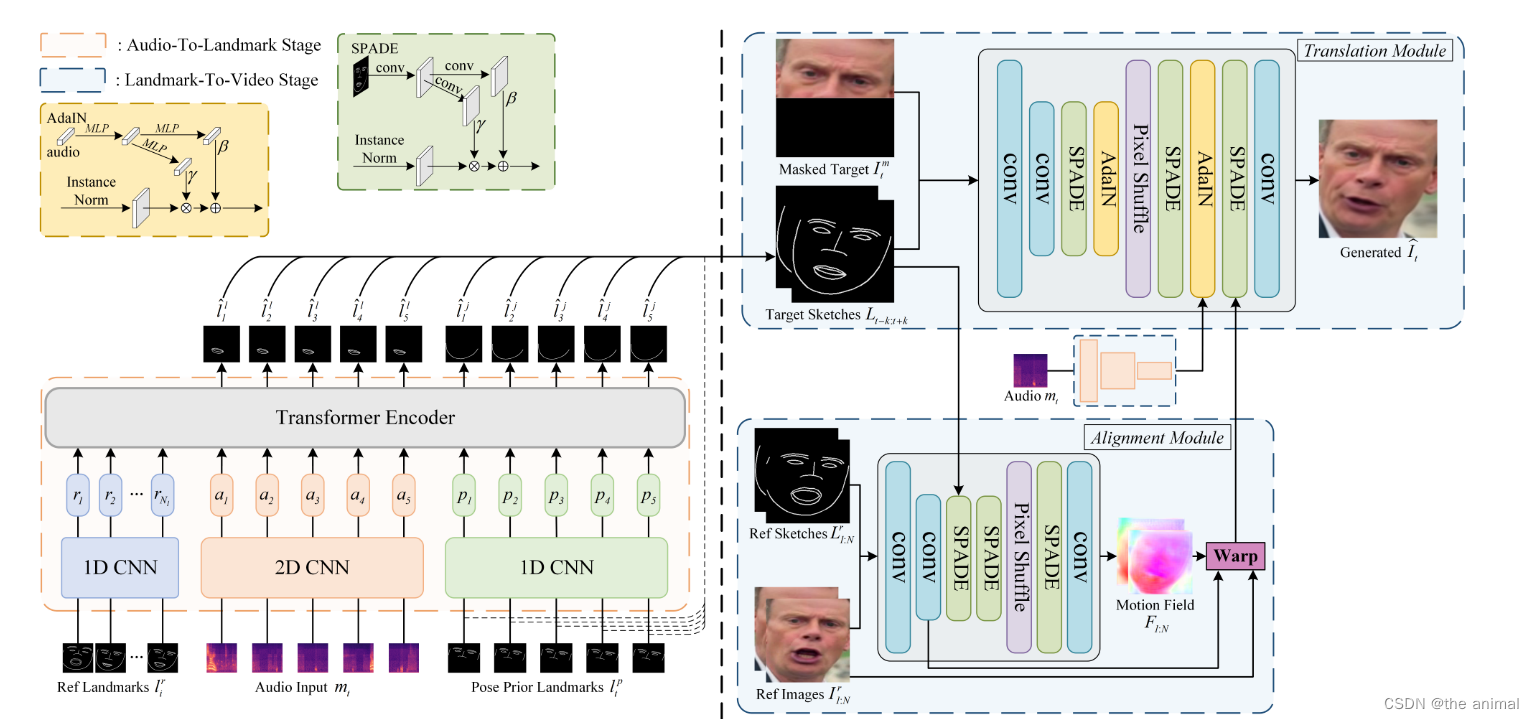

mycpu和dram、confreg之间有一个“一分二”部件。这是因为在LoongArch指令系统架构下,所有I/O设备的寄存器都是采用memory mapped方式访问的。我们这里实现的confreg也不例外。Memory mapped的访问方式意味I/O设备中的寄存器各自都有一个唯一内存编址,所以CPU可以通过load、store指令对其进行访问。不过dram作为内存也是通过load、store指令进行访问的。那么对于一条load或store指令来说,如何知晓它访问的是confreg还是dram?我们在设计SoC的时候用地址对其进行区分。因此在设计SoC的数据通路时就需要在这里引入一个“一分二”部件,它的选择控制信号生成是通过对访存的地址范围进行判断而得到的。

实验6-exp6共有20条指令

wire inst_add_w;

wire inst_sub_w;

wire inst_slt;

wire inst_sltu;

wire inst_nor;

wire inst_and;

wire inst_or;

wire inst_xor;

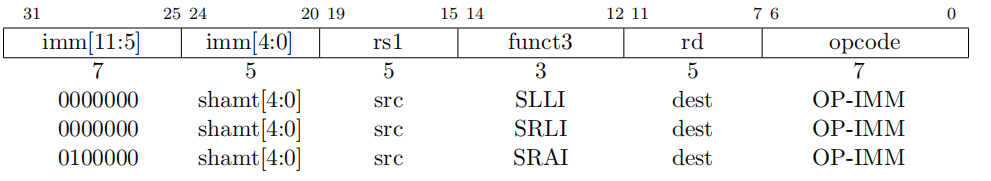

wire inst_slli_w;

wire inst_srli_w;

wire inst_srai_w;

wire inst_addi_w;

wire inst_ld_w;

wire inst_st_w;

wire inst_jirl;

wire inst_b;

wire inst_bl;

wire inst_beq;

wire inst_bne;

wire inst_lu12i_w;

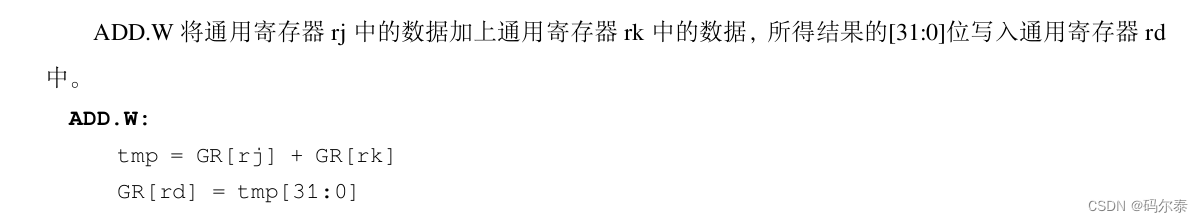

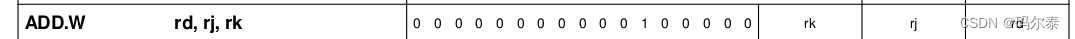

1. add.w

- 指令格式

- 指令码

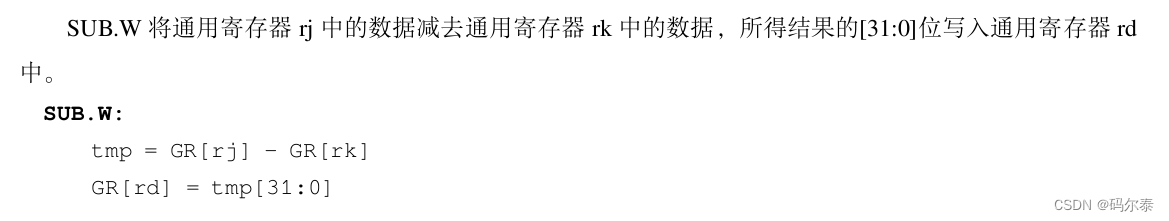

2. sub.w

-

指令格式

-

指令码

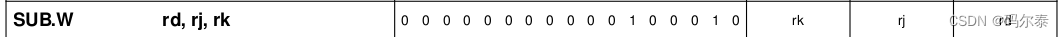

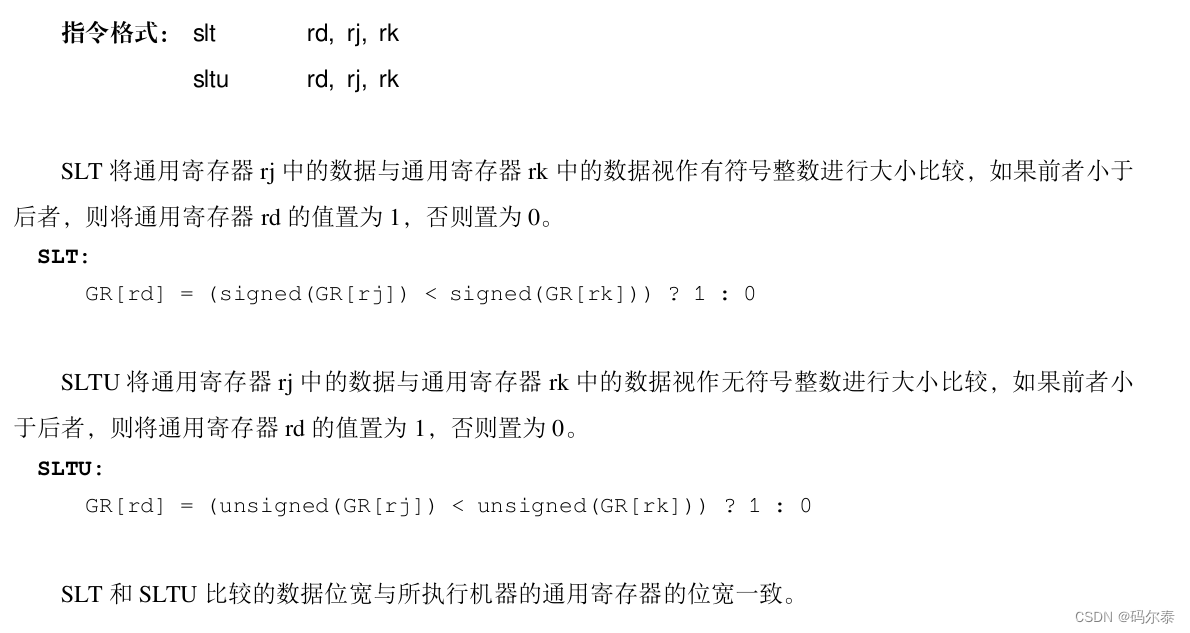

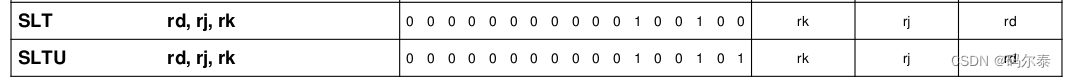

3. slt、sltu

- 指令格式

- 指令码

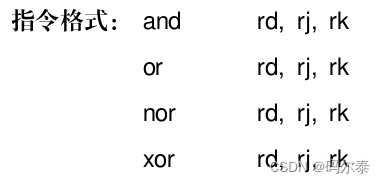

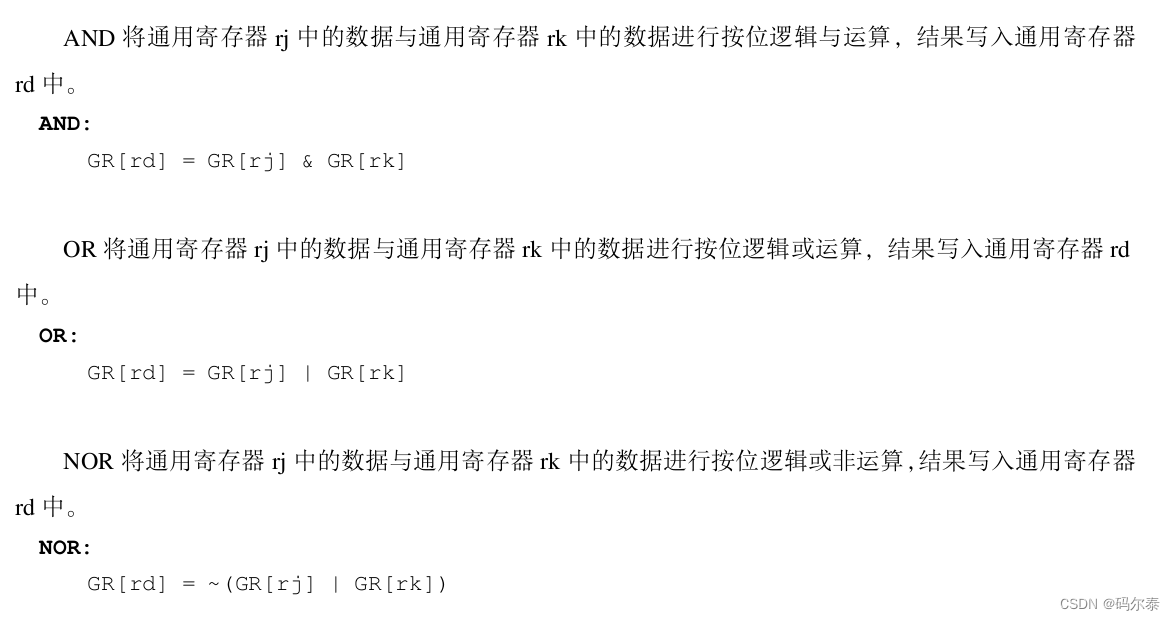

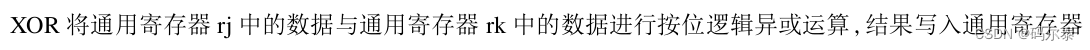

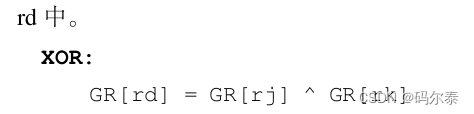

4. inst_nor, inst_and, inst_or,inst_xor

- 指令格式

- 指令码

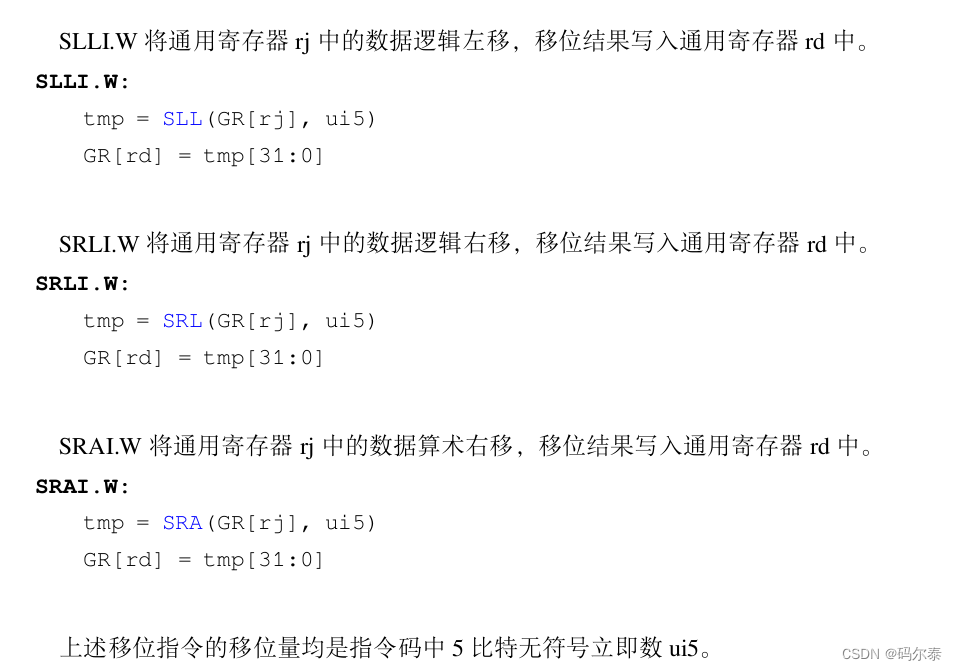

上述移位指令的移位量均是指令码中 5 比特无符号立即数 ui5 - 指令码

该指令执行时不对溢出情况做任何特殊处理 - 指令码

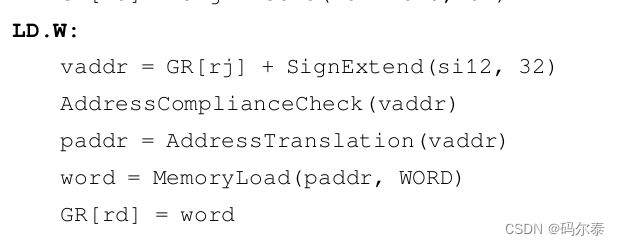

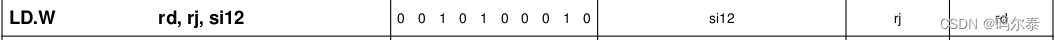

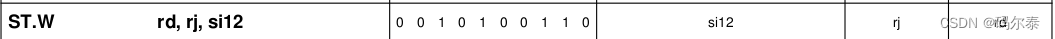

上述指令的访存地址计算方式是将通用寄存器 rj 中的值与符号扩展后的 12 比特立即数 si12 相加求和。

对于 LD.{H[U]/W}和 ST.{B/H/W}指令,只要其访存地址是自然对齐的,都不会触发非对齐例外;否则

的话将触发非对齐例外。 - 指令码

wire inst_jirl;

wire inst_b;

wire inst_bl;

wire inst_beq;

wire inst_bne;

wire inst_lu12i_w;