AD7792/AD7793 是一款 ∑-Δ ADC,3 通道、低噪声,内部集成仪表放大器和参考源。AD7792 为 16 位,AD7793为 24 位。

- 供电电压:2.7 ~ 5.25 V,并不支持负电压。

- 转换速率:4.17 Hz ~ 470 Hz

- 内置参考基准:1.17 V

- 内置运放增益:1 ~ 128

- 内置温度传感器

- 输出电流源:10 uA、210 uA 和 1000 uA

- SPI 通讯接口,使用 最大通讯速率 5 MHz

- 封装:TSSOP-16

功能框图

模拟输入

在设计原理图之前,必须确认输入信号的约束条件。

差分输入电压范围

增益为1 ~ 128范围内,差分输入电压范围为:±VREF/Gain,单位是 V

这个式子表明:选择的增益越大,差分输入电压范围越小。换句话说,内部 ∑-Δ ADC 的输入电压不能超过 VREF 。

无缓冲模式

ADC 内部有缓冲放大器(BUF),当增益为 1~2 时,可以选择旁路缓冲放大器。

- 先说好处,绝对模拟输入电压限值范围最大,可以达到:(GND-30) mV ≤ VAIN ≤ (AVDD+30) mV;然后,它可以检测相对于 GND 的小的双极性信号(- 30mV)。

- 然后是缺点,由于旁路掉了缓冲放大器,输入模拟电流变大;其次,ADC 的输入阻抗变低,所以被测信号的内阻和电容会导致增益误差,这取决于被测信号的内阻和电容的大小。如果想在 20 位分辨率下不引入增益误差,可被允许的被测信号链路的阻抗和电容如下图所示:

从图中可以看出,这对被测信号的要求相当高,因此,缓冲放大器需要尽可能开启。

缓冲模式

当 ADC 的内部缓冲放大器被激活后,其输入阻抗显著提升,可以视为高阻抗输入。因此,ADC 的输入能够接纳具有显著高内阻的被测信号。适合直接连接到外部电阻型传感器,比如应变计或者 RTD 测温。

代价就是绝对模拟输入电压限值范围变小了,为:(GND + 100) mV ≤ VAIN ≤ (AVDD - 100) mV。

这是因为缓冲放大器的输入输出并不能达到轨到轨,当输入信号电压接近电源轨时,会有显著的失真。

仪表放大器模式

当增益 ≥4 时,ADC 自动启用内部 缓冲放大器和仪表放大器。使用这种模式时,允许测量非常小的输入信号,但也带来了新的问题,绝对模拟输入电压限值范围更小了,为:(GND + 300) mV ≤ VAIN ≤ (AVDD - 1.1) V

同时,因为引入了仪表放大器,仪表放大器要求的共模电压条件同样也引入了:VCM ≥ 0.5V

共模电压 VCM = (AIN(+) + AIN(-)) / 2

输出噪声差

对于ADC 器件,输出均方根噪声(RMS Noise)可以表征 ADC 的精度和性能。输出均方根噪声越小,表明 ADC 的输出信号中的噪声和干扰越低,因此 ADC 的转换结果更接近理想的模拟输入信号,即精度更高。

理想的 ADC 是没有输出噪声的,当输入接地,无论转换多少次,得到的 输出码(output code) 总是 0 。但实际上, ADC 内部有热噪声,转换过程中还会有量化噪声,实际转换的输出码并不总是为 0,而是如下图所示:

这个图一般称为 噪声直方图,该图提供了有关直流噪声性能的重要图形信息。噪声直方图具有高斯分布特性,ADC 的数据手册中通常会给出输出 均方根噪声 数据,这里均方根噪声定义为噪声直方图中 1 个标准差范围内的噪声,如下图所示,红色部分为均方根噪声:

标准差是一种衡量数据分布散度的度量值,用于描述数据相对于平均值的波动程度。它以符号σ表示。

具体来说,标准差的计算方法是求每个数据点与平均值的差的平方的平均数,然后取平方根。这个计算方法反映了数据相对于平均值的差异程度,即数据分布的离散程度。

标准差越小,数据相对比较紧凑,波动程度越小;标准差越大,数据相对比较分散,波动程度越大。

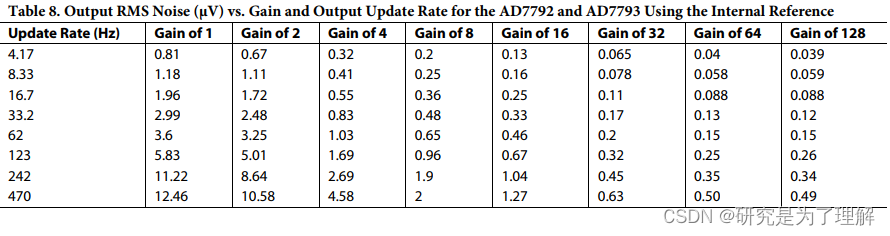

下面给出输入为 0V 差分电压、不同的增益和转换速率条件下,AD7792/AD7793 典型的输出均方根噪声(单位 uV)。

使用外部参考源

使用 2.5V 的外部参考源。

从图中可以看出:

- 增益越大,均方根噪声越小,低增益(1~4)均方根较大,增益达到 64 时,均方根噪声趋于稳定。

- 转换速率越高,均方根噪声越大。在使用时,尽可能的使用低转换速率。

使用内部参考源

使用 1.17V 的内部参考源。

从图中可以看出:

- 均方根噪声与增益和转换速率的关系同上(使用外部参考源)

- 增益和转换速率相同的条件下,使用内部参考源的均方根噪声稍稍变大,特别是增益为 1 时,比如转换速率为 4.17Hz 时,使用内部参考源的均方根噪声比使用外部参考源高出 26.5% 。但在增益大于等于 4 时,区别就没有那么明显,比如增益为 4 时,同样转换速率为 4.17Hz,使用内部参考源的均方根噪声比使用外部参考源只高出 10.3%。

有效分辨率和峰峰分辨率

上节介绍了 输出噪声,知道噪声不可避免,给出了各种条件下的 均方根噪声 数据。

峰峰噪声 (peak-to-peak noise)是另一种衡量输出噪声大小的方法,对很多应用来说,这种衡量方法更加有效,因为落在峰峰噪声范围内的有效模拟信号可能会被 ADC 的底噪所掩盖,导致输出码非常快速的抖动,称为 输出代码闪动(code flicker)。峰峰噪声是用均方根噪声计算而来的,即:

峰峰噪声 = 6.6 ∗ 均方根噪声 峰峰噪声 = 6.6 * 均方根噪声 峰峰噪声=6.6∗均方根噪声

这是因为噪声直方图具有高斯分布特性,高斯曲线的分布是从负无穷大到正无穷大。然而,99.99%的码字出现在 6.6 倍均方根噪声范围内。因此,峰峰值噪声为均方根噪声的 6.6 倍,等效于所有码字,如下图所示,蓝色部分为峰峰噪声:

额外的过采样将有助于降低峰峰噪声,但代价是采样时间更长。

这与有效分辨率和峰峰分辨率有什么关系呢?

有效分辨率(effective resolution)是通过均方根噪声计算出的;峰峰分辨率(peak-to-peak resolution)是通过峰峰噪声计算出来的。

因此,评估ADC时,应当认识到有效分辨率与峰峰分辨率的计算方法不同,与有效分辨率相比,峰峰分辨率更加严苛,不存在输出代码闪动。

有效分辨率和峰峰分辨率是如何计算的,这里给出过程。

首先,信噪比为:

S N R = 20 l o g ( n o i s e f u l l s c a l e i n p u t ) = 6.02 N + 1.76 SNR = 20log(\frac{noise}{full \, scale \, input}) = 6.02N + 1.76 SNR=20log(fullscaleinputnoise)=6.02N+1.76

其中,N为 ADC 的分辨率位数

下面给出不同的增益和转换速率条件下,AD7792 和 AD7793 的有效分辨率和峰峰分辨率(在括号内显示)。

使用外部参考源

从图中可以看出:

- 增益越大,有效分辨率和峰峰分辨率越差

- 转换速率越高,有效分辨率和峰峰分辨率越差

- 使用 16 位的 AD7792 时,增益和转换速率对分辨率的影响不明显

- 使用 24 位的 AD7793 时,要注意增益和转换速率的选择,以便获取所需的分辨率。

- 当使用 24 位的 AD7793 时,有效分辨率并不能达到 24 位,峰峰分辨率就更低了。

使用内部参考源

单极/双极配置

AD7792/AD7793 的模拟输入端可接受单极或双极的输入电压范围。然而,需要注意的是,双极输入范围的接纳并不意味着该部件可以承受相对于系统 GND 的负电压。在 AIN(+) 输入端上的信号,无论是单极还是双极,都是以 AIN(-) 输入端的电压为基准的。举个例子,假设 AIN(-) 的电压为 2.5 V,当 ADC 配置为单极模式且增益设为 1 时,AIN(+) 引脚上的输入电压范围就会是 2.5 V 至 5 V。如果 ADC 配置为双极模式,那么 AIN(+) 输入上的模拟输入范围则会变为 0 V 至 5 V。

这种灵活性是通过编程配置寄存器中的 U/B 位来实现的,从而轻松选择在双极或单极模式下运行。

数据输出编码

单极配置

当 ADC 配置为单极模式时,输出代码是直接二进制代码,零差分输入电压的输出代码为 0000…00、中间输入电压输出代码为 1000…00、满量程输入电压输出代码为 1111…11。模拟输入电压与输出代码满足:

C o d e = 2 N ∗ A I N ∗ G A I N V R E F Code = \frac{2^{N} * AIN * GAIN}{V_{REF}} Code=VREF2N∗AIN∗GAIN

其中

- N 为分辨率,对于 AD7792 ,N = 16, 对于AD7793,N = 24。

- AIN 为模拟输入电压

- GAIN 为仪表放大器增益

双极配置

当 ADC 配置为双极模式时,输出代码是偏移二进制代码,负满量程输入电压的输出代码为 0000…000,零差分输入电压的输出代码为 1000…000,正满量程输入电压的输出代码为 1111…111。模拟输入电压与输出代码满足:

C o d e = 2 N − 1 ∗ ( A I N ∗ G A I N V R E F + 1 ) Code = 2^{N-1} *(\frac{AIN * GAIN}{V_{REF}} + 1) Code=2N−1∗(VREFAIN∗GAIN+1)

其中

- N 为分辨率,对于 AD7792 ,N = 16, 对于AD7793,N = 24。

- AIN 为模拟输入电压

- GAIN 为仪表放大器增益

寄存器

通讯寄存器

与设备的所有通讯 必须 以写通讯寄存器开始。写入通讯寄存器的数据决定下一次操作是读操作还是写操作,以及此操作发生在哪个寄存器。当后续读写操作完成后,通讯接口自动返回默认状态(等待对通讯寄存的写入操作),以便进行下一次与设备通讯。

如果在这个过程中出错,需要将 DIN 置高 至少 32 个串行时钟周期,以便将通讯接口返回默认状态。

bit7:写使能位。必须写入 0,设备将忽略非零值,直到第一个 0 出现,然后接下来的 7 位数据也会被写入通讯寄存器。

bit6:读写标志。0 表示下一个操作是 写操作,1 表示下一个操作是 读操作。

bit2:数据寄存器 连续读,1 有效。bit2 = 1 且选中数据寄存器,则可以连续读取数据寄存器。退出连续读取数据寄存器需要向通讯寄存器的 bit2 写入 0。

连续读取模式时,ADC 会检测 DIN 脚信号,以便接收退出连续读取数据寄存器指令。但是通讯接口的复位条件是至少连续 32 个串行时钟周期内,DIN 为高电平,因此连续读模式期间,DIN 应保持为低电平。