有不少小伙伴说还想要更多模拟IC方向的面试题目,这不就来了!(文末可领全部面试题目)

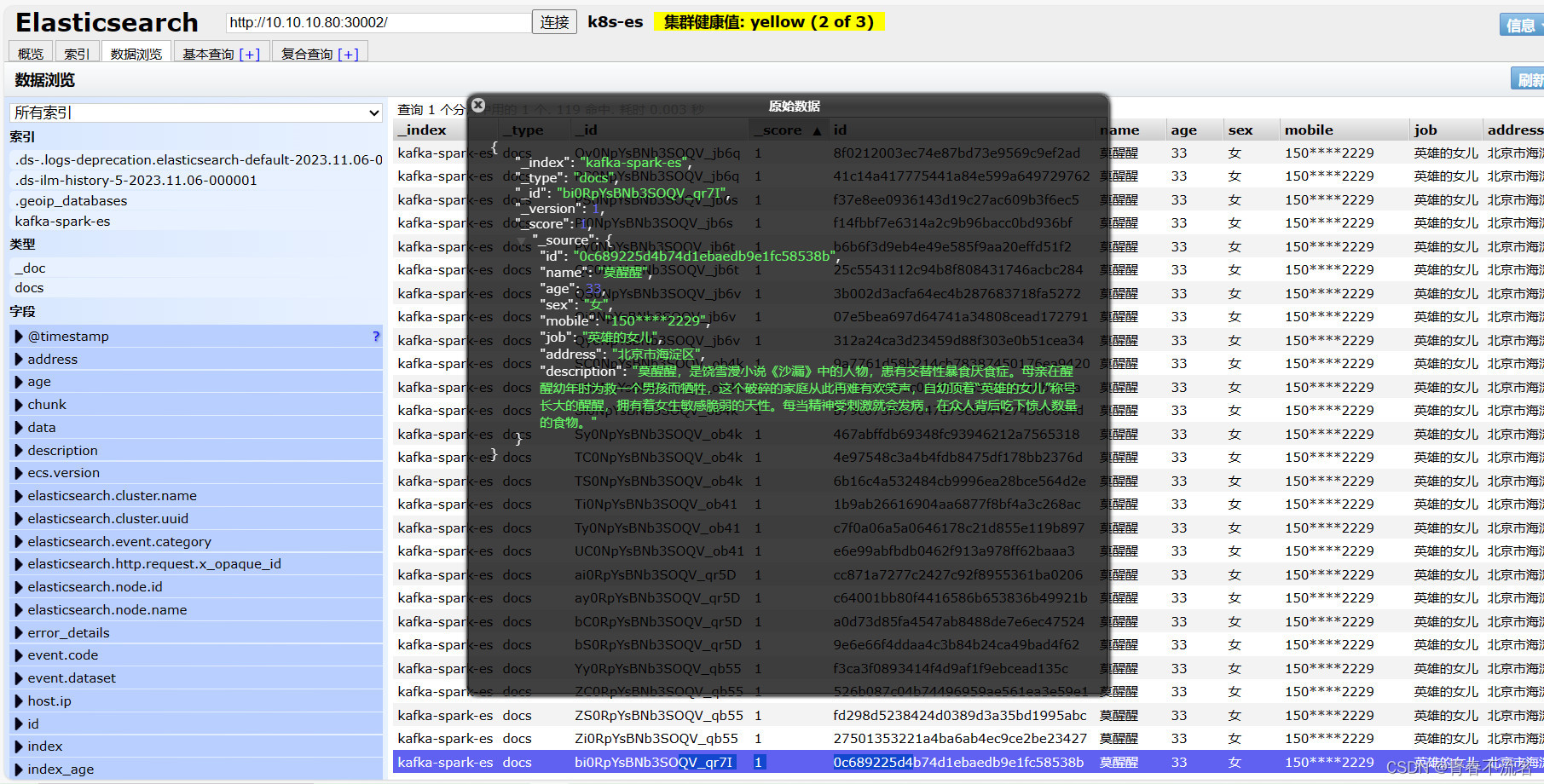

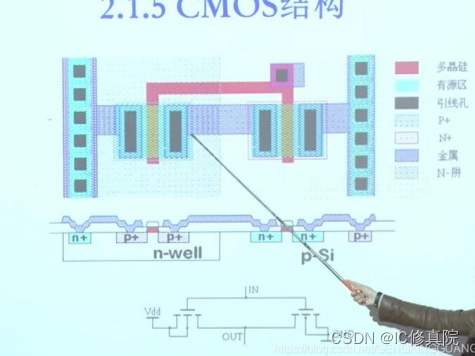

请描述一下 CMOS 的工艺流程

1)光刻形成 well 阱区:在 p 型硅衬底上生长一层氧化层,涂光刻胶,用掩膜版曝光、显影、刻蚀进行 N 离子注入。

2)光刻有源区:使用掩膜版确定场氧区,和 p.nmos 的有源区,再去掉氮化硅,再生长场氧

(隔离 pnmos),以及重新生长高质量的薄氧化层。

3)淀积和光刻多晶硅栅。使用三号掩膜版进行光刻,形成栅极。

4)p+注入,形成 pmos 有源区和 nmos 衬底接触。

5)n+注入,形成 nmos 有源区和 pmos 衬底接触。

6)光刻接触孔:光刻出接触孔位置。

7)光刻金属掩膜版。

描述 CMOS 电路中闩锁效应产生的过程及最后的结果?

Latch-up 闩锁效应,又称寄生 PNPN 效应或可控硅整流器(SCR, Silicon Controlled Rectifier)效应。在整体硅的 CMOS 管下,不同极性搀杂的区域间都会构成 P-N 结,而两个靠近的反方向的 P-N 结就构成了一个双极型的晶体三极管。因此 CMOS 管的下面会构成多个三极管,这些三极管自身就可能构成一个电路。这就是 MOS 管的寄生三极管效应。

如果电路偶尔中出现了能够使三极管开通的条件,这个寄生的电路就会极大的影响正常电路

的运作,会使原本的 MOS 电路承受比正常工作大得多的电流,可能使电路迅速的烧毁。Latch-up 状态下器件在电源与地之间形成短路,造成大电流、EOS(电过载)和器件损坏。

什么是电压放大?什么是电流放大?什么是功率放大?

电压放大:就是只考虑输出电压和输入电压的关系。比如说有的信号电压低,需要放大后才

能被模数转换电路识别,这时就只需做电压放大。

电流放大:就是只考虑输出电流于输入电流的关系。比如说,对于一个 uA 级的信号,就需

要放大后才能驱动一些仪器进行识别(如生物电子),就需要做电流放大。

功率放大:就是考虑输出功率和输入功率的关系。

其实实际上,对于任何以上放大,最后电路中都还是有电压、电流、功率放大的指标在,叫

什么放大,只是重点突出电路的作用而已。

什么是阈值电压?影响因素有哪些?

阈值电压Vt 是指当背栅与源极连接在一起时使能栅介质下面恰好产生沟道所需要的栅源电

压。MOS 管的阈值电压与以下因素有关:栅极电材料,背栅掺杂,栅氧化层厚度,表面态

电荷密度,氧化层中的电荷密度(固定点荷和可用电荷)。

画电流偏置的产生电路,并解释。

偏置电路:以常用的共射放大电路说吧,主流是从发射极到集电极的 IC,偏流就是从发射极

到基极的 IB。相对与主电路而言,为基极提供电流的电路就是所谓的偏置电路。偏置电路往

往有若干元件,其中有一重要电阻,往往要调整阻值,以使集电极电流在设计规范内。这要

调整的电阻就是偏置电阻。

有源滤波器和无源滤波器的区别

无源滤波器:这种电路主要有无源元件 R、L 和 C 组成。

有源滤波器:集成运放和 R、C 组成,具有不用电感、体积小、重量轻等优点。

集成运放的开环电压增益和输入阻抗均很高,输出电阻小,构成有源滤波电路后还具有一定

的电压放大和缓冲作用。但集成运放带宽有限,所以目前的有源滤波电路的工作频率难以做

得很高。

说一下天线效应和解决办法

在工艺生产中,暴露的一根根长长的 poly 或者 metal 等导体,就像是一根根天线一样,

当周围有游离电荷时候,这些“天线”就会将电荷收集起来。天线越长收集电荷的效果就越强。收集的电荷也就越多。当电荷足够多,电压相对也就越高。

一定程度会发生击穿使电路失效;而且如果这片导体恰巧只接了 Mos 的栅,那么高电压可能会将薄衫氧化层击穿使电

路失效。

1)向上跳线或向下跳线,通过通孔将产生天线效应的金属层连接到上一层(下一层)金属

层,最后再回到当前层;因为用到当前层的时候上一层金属还不存在,更加方便合理;

2)通过给直接连接到栅的存在天线效应的金属层接上反偏二极管,形成一个电荷泄放回路,累积电荷就对栅氧构不成威胁,从而消除了天线效应。

画出反相器的剖面图。

什么叫 MOS 晶体管热点安全工作区?

MOS 晶体管可用作开关或大功率调节。为了与低功率或者小信号器件加以区分,

专门为这类应用而设计的器件称为功率晶体管。一般把安全工作区(SOA)边界

的这两部分称为电学 SOA 与热电 SOA。

由于篇幅限制,就不一一更新了,需要上述面试题目的同学可按需领,可以直接分享给大家~

这里放个口:模拟IC笔面试题目