使用modport可以将interface中的信号分组并指定方向,方向是从modport连接的模块看过来的。简单示例如下:

interface cnt_if (input bit clk);logic rstn;logic load_en;logic [3:0] load;logic [7:0] count;modport TEST (input clk, count,output rstn,load_en,load);modport DUT (input clk,rstn,load_en,load,output count);endinterfacemodule Design(clk,rstn,load_en,load,count );input clk,rstn,load_en,load;

output reg [7:0] count;always @(posedge clk or negedge rstn)if(!rstn)count<=0;else count<=count+1;endmoduleclass AA;virtual cnt_if.DUT this_s;function new(virtual cnt_if.DUT if_inst);this_s=if_inst;

endfunctiontask assig();this_s.rstn=0;repeat(100) @(posedge this_s.clk);this_s.rstn=1;this_s.load_en=0; this_s.load=1; this_s.count='d56;repeat(100) @(posedge this_s.clk);this_s.rstn=0; this_s.load_en=1; this_s.load=0; this_s.count='d34;endtaskendclass module tb;logic clk;initial begin clk=0; endalways #5 clk=~clk;//cnt_if.DUT if_instance (clk);cnt_if if_instance (clk);AA ainstance=new(if_instance.DUT);//Design(clk,rstn,load_en,load,count );Design design_inst(.clk(if_instance.DUT.clk), .rstn(if_instance.DUT.rstn) ,.load_en(if_instance.DUT.load_en ), .load(if_instance.DUT.load) ,.count(if_instance.DUT.count) );initial beginainstance.assig;endendmodule注意:

(1)在interface中使用modport将信号分组后,在tb中例化时,直接例化interface的实例,不能例化interface中modport的实例;

(2)在calss中直接例化interface中modport的实例;

(3)在tb中实例化interface的实例后,将interface的实例的modport通过点运算符传递给DUT。

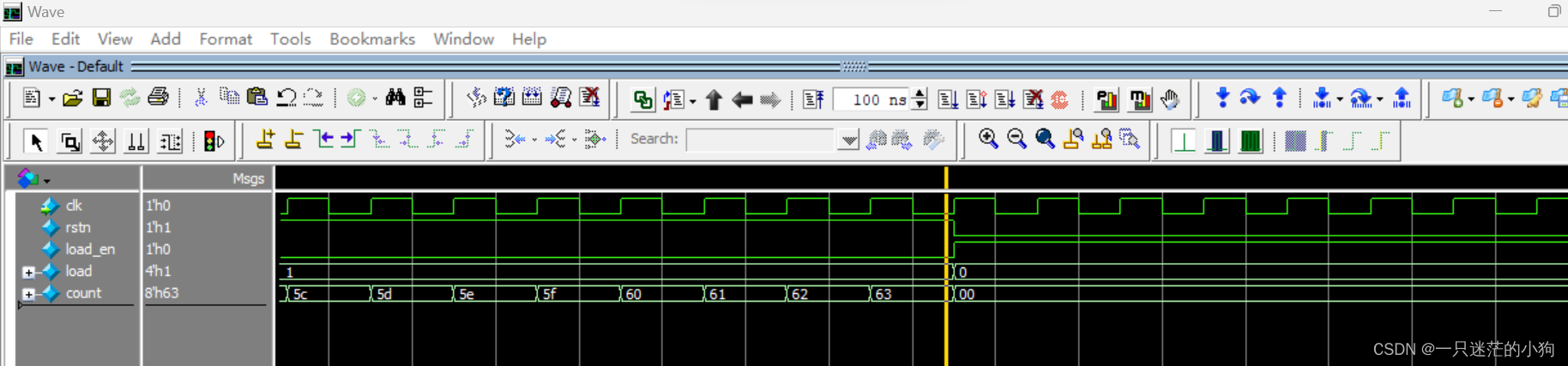

仿真波形如下: