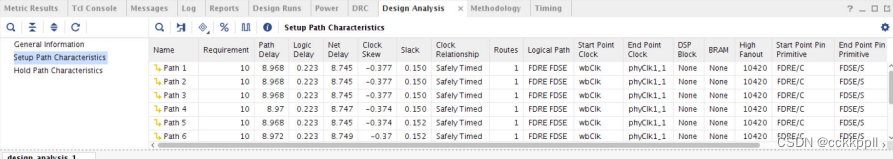

时序路径特性报告

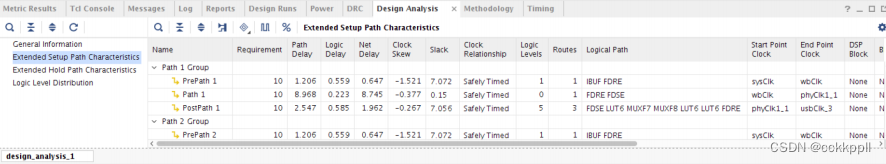

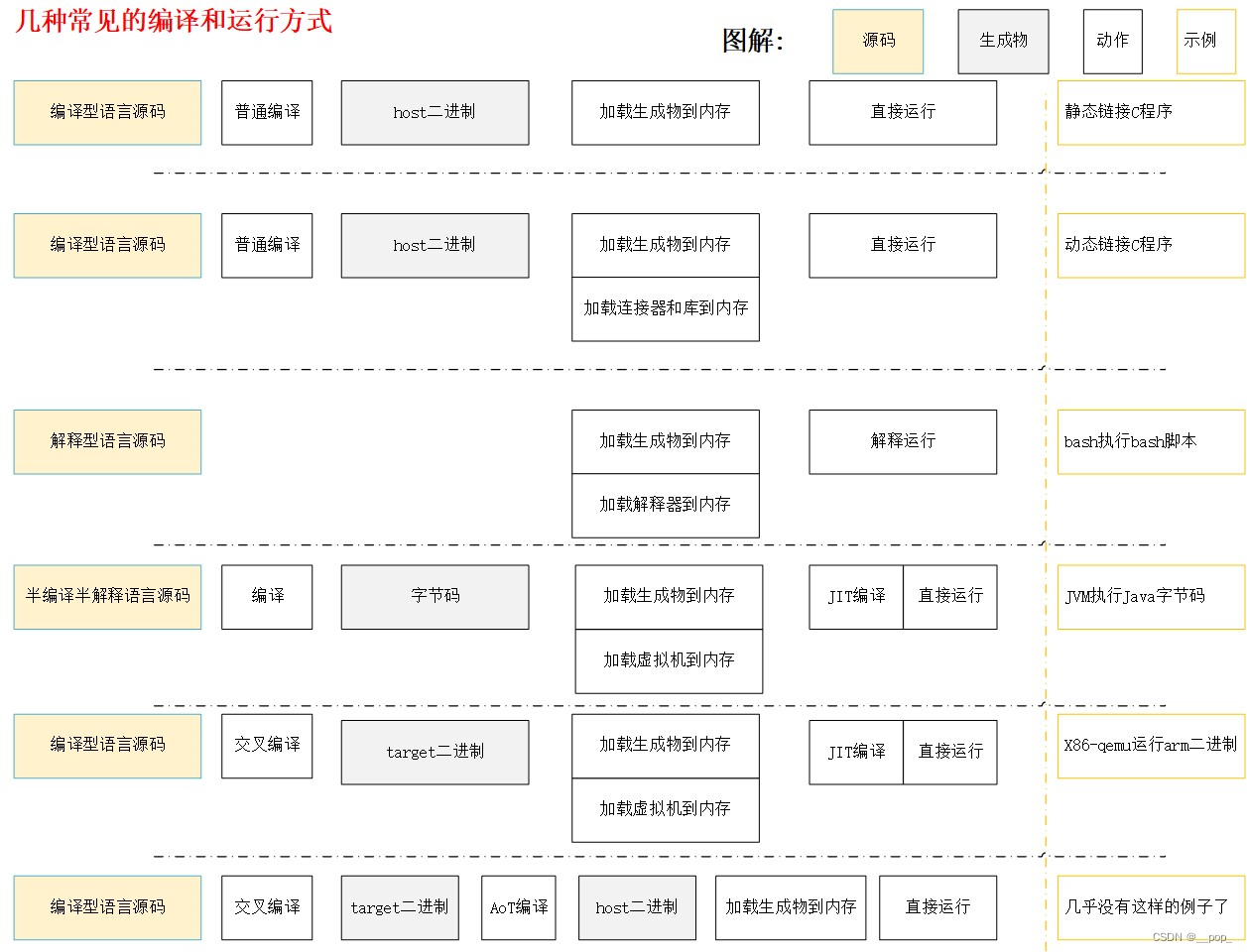

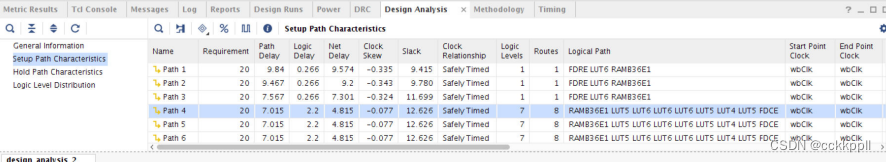

下图显示了在“ Timing Mode ” ( 时序模式 ) 下运行“ Report Design Analysis ” ( 设计分析报告 ) 的输出示例 , 其中显示了设计中 10 条最差建立路径的路径特性。在 Vivado IDE 中选中“ Reports ” → “ Report Design Analysis ” ( 报告 > 设计分析报告) 或者使用以下 Tcl 命令来生成报告 :

report_design_analysis -name <arg>

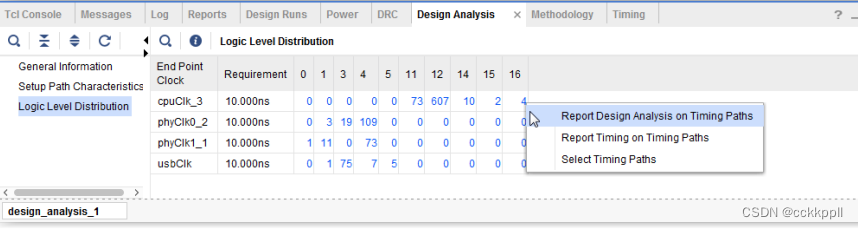

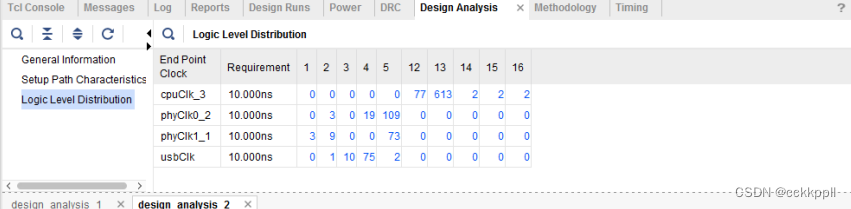

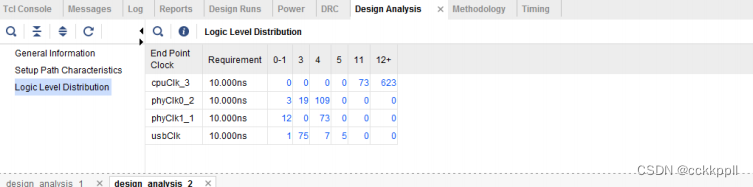

此外 , “ Report Design Analysis ”还提供了最差时序路径的“ Logic Level Distribution ” ( 逻辑层次分布 ) 表。针对 “Logic Level Distribution ”表分析的默认路径数量为 1,000 条 , 可在“ Report Design Analysis ”对话框中更改此数量。默认情况下, 不生成“ Logic Level Distribution ”表 , 生成该表需选择“ Report Design Analysis ”对话框 “Options ”选项卡中的“ Include logic level distribution ” ( 包含逻辑层次分布 ) 。“ Logic Level Distribution ”表的示例如下图所示。

Logic Level Distribution GUI 已实现功能增强 , 包含对应各 bin 文件的独立超链接。单击这些超链接即可在路径上运行 report_design_analysis 或 report_timing , 或者选择时序路径 , 如下图所示。

命令行选项 -routes 可与 -logic_level_distribution 搭配使用 , 以便基于布线数量而不是逻辑层次数量来生成报告。

命令行选项 -min_level 和 -max_level 可与 -logic_level_distribution 搭配使用以控制 bin 文件。

逻辑级数小于 -min_level 的所有路径都置于单个 bin 文件内 , 逻辑级数大于 -max_level 的所有路径也都置于单个 bin 文件内。

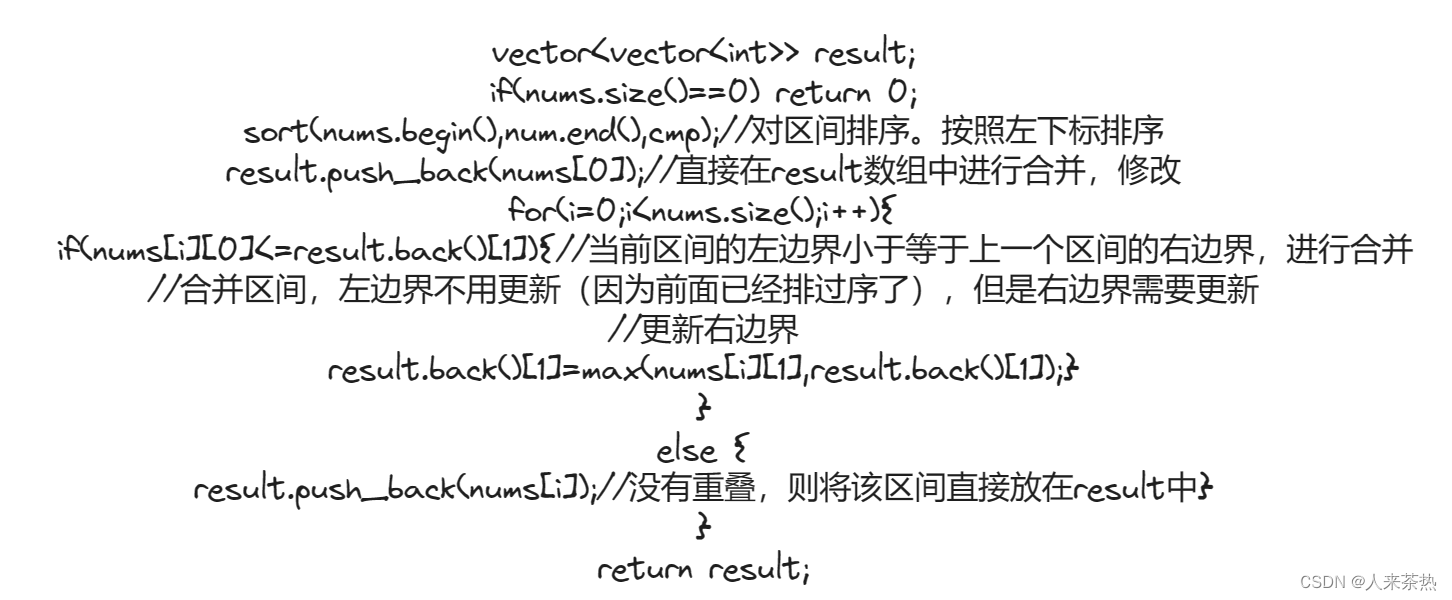

为每个逻辑层次创建一个独立 bin 文件 , 使逻辑层次间存在至少 1 条路径。例如 , 如果设计包含的路径的逻辑级数为0、 1 、 3 、 4 、 5 、 11 、 12 、 14 、 15 、 16 并使用 -min_level 3 和 -max_level 11 ,

那么 report_design_analysis 会分别使用以下 bin 文件生成报告 : 0-2 、 3 、 4 、 5 、 11 和 12+ 。

分析特定路径

分析特定路径 显示了来自“ Report Design Analysis ” ( 设计分析报告 ) 的报告示例 , 此示例采用“ Timing Mode ”(时序模式 ) 并选定特定路径。

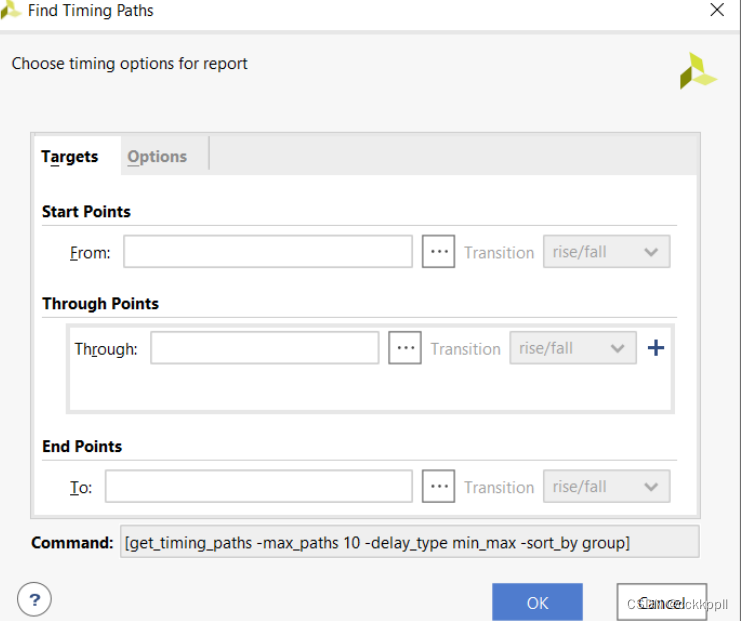

在本例中 , “ Path Characteristics ” ( 路径特性 ) 和“ Logic Level Distribution ” ( 逻辑层次分布 ) 表 ( 如果已选中 ) 已限制为指定路径。要指定路径, 在“ Report Design Analysis ”对话框“ Specific paths ” ( 指定路径 ) 选择部分单击 右侧的“Browse ” ( 浏览 ) 按钮。这样会打开“ Find Timing Paths ” ( 查找时序路径 ) 对话框 ( 如下图所示 ) 。

结合前后最差路径执行最差路径分析

下图显示了“ Timing Mode ” ( 时序模式 ) 下已选中“ Extend analysis ” ( 扩展分析 ) 选项情况下的“ Report Design Analysis” ( 设计分析报告 ) 的报告示例。

“ Path Characteristics ” ( 报告特性 ) 报告中包括最差建立路径、止于起点单元的最差建立路径 ( PrePath ) 和始于端 点单元的最差建立路径 ( PostPath ) 。 -extend 选项产生的运行时间更长 , 因为需执行多项时序分析以收集所有已报 告路径的特性。

等效的 Tcl 命令 : report_design_analysis -extend