Constraining Async Clock Domain Crossing

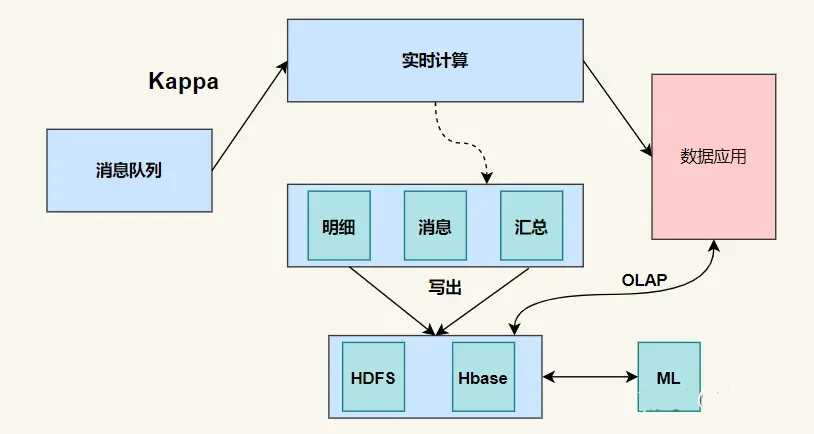

我们在normal STA中只会去check 同步clock之间的timing,但是design中往往会存在很多CDC paths,这些paths需要被正确约束才能保证design function正确,那么怎么去约束这些CDC paths呢?

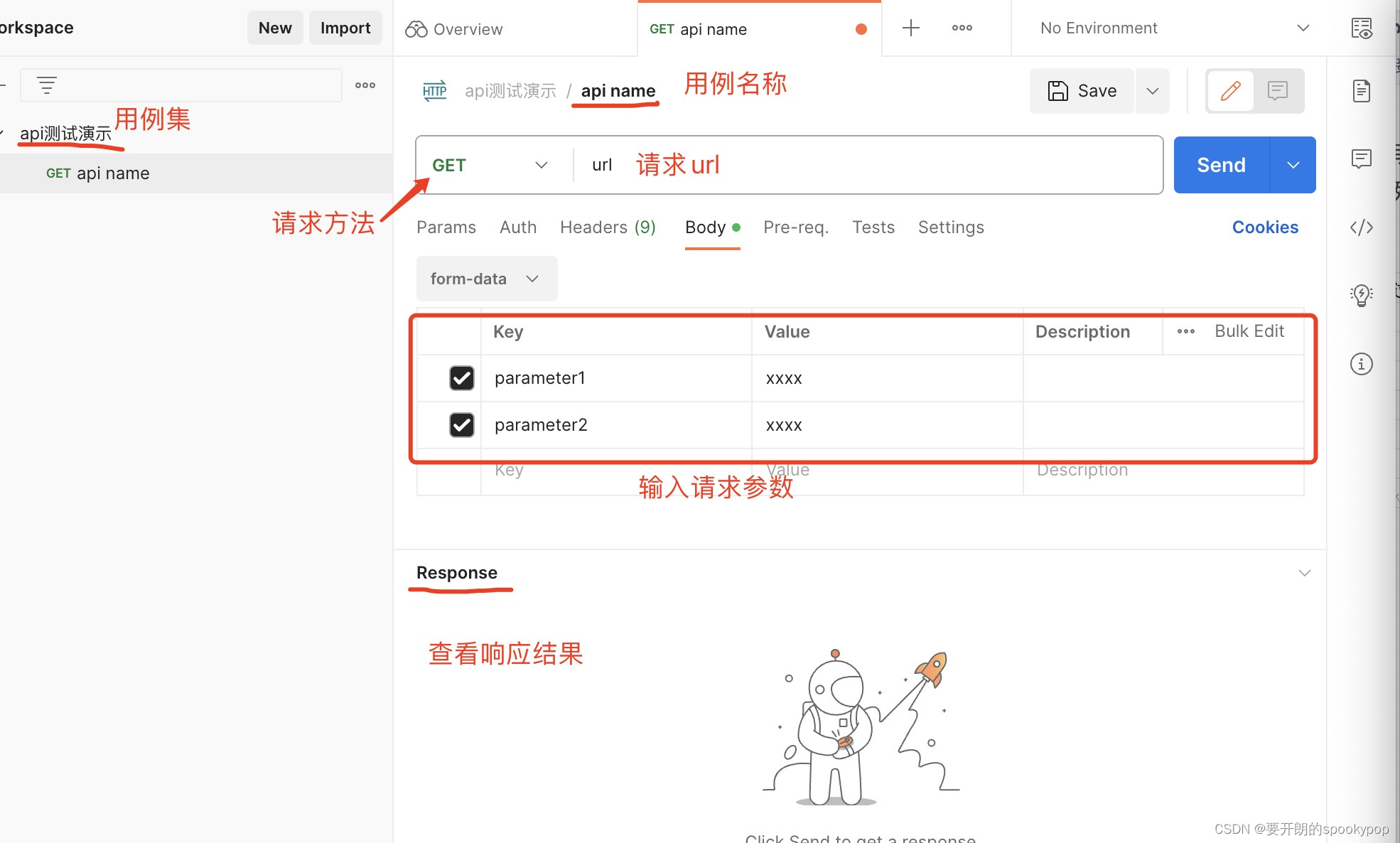

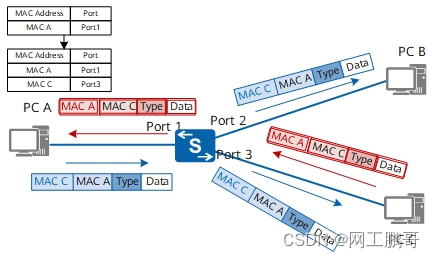

以下面的design为例,如下图所示

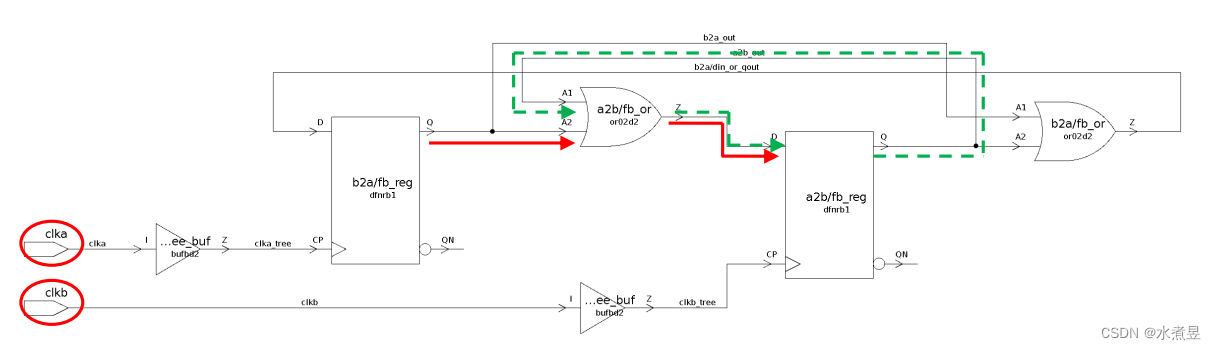

这里clka和clkb是异步关系,上图中的绿色虚线部分为clkb的internal path,属于同步path,而红色部分则属于CDC Path,怎么去约束这个path呢?

Create CDC clock

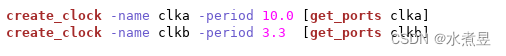

首先,我们创建normal func clock如下:

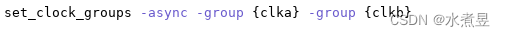

然后声明他们为async关系,如下:

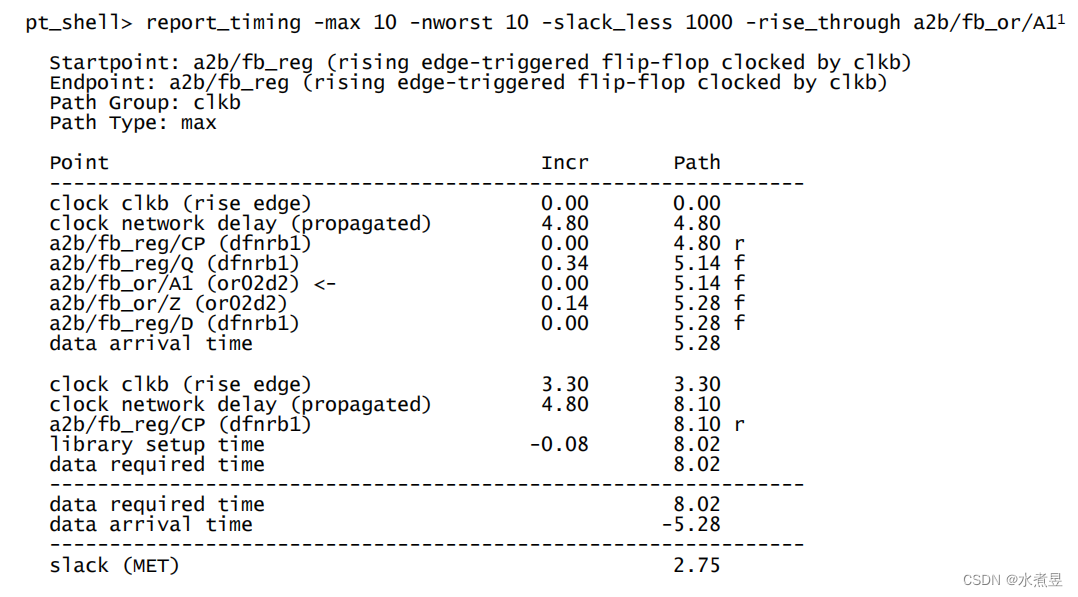

这时我们去report timing,结果如下

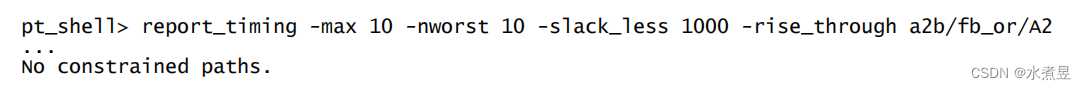

我们只能看到这个clkb的同步path,要在normal STA中report 红色CDC path则会显示No Constrained paths:

注意:

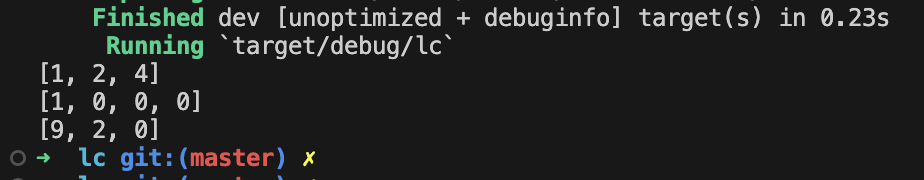

The -max, -nworst are to make sure I don’t miss any paths, the -rise_through is so that I don’t see 2 paths where I only want