Makefile从零基础到入门到熟练使用

一、了解Makefile作用

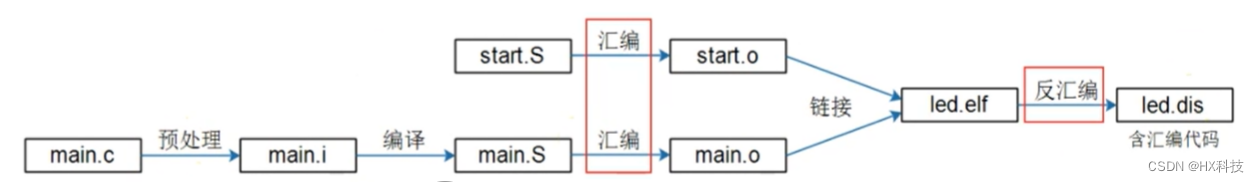

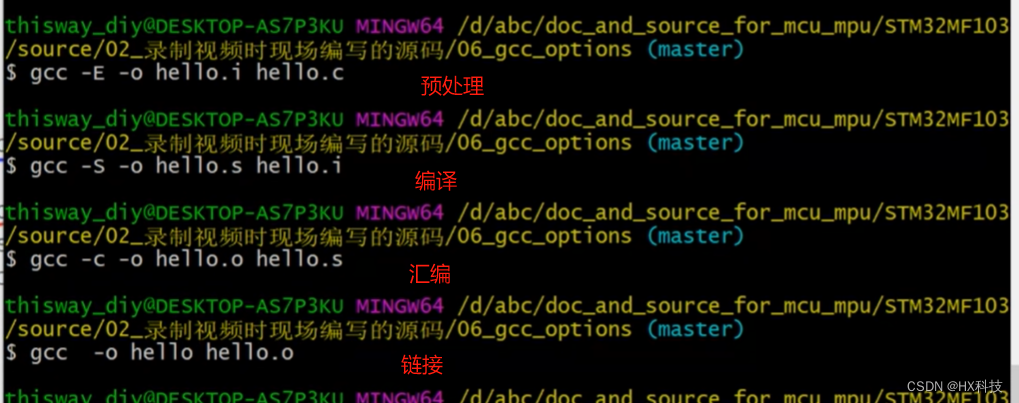

1、一个文件从源码到可执行文件的过程:预处理-编译-汇编-链接

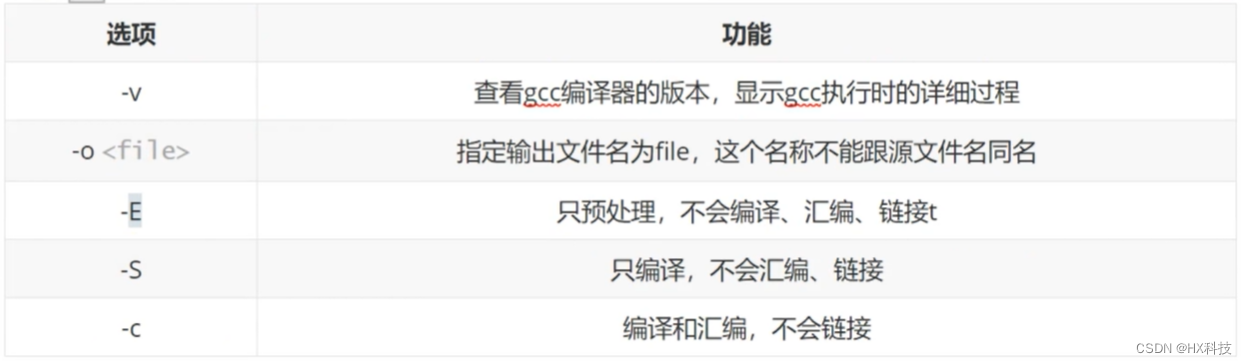

2、每个步骤都可以单独执行

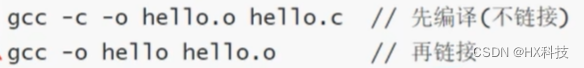

3、使用过程中会压缩成两步

4、一步执行并且打印详细日志信息

gcc -o hello hello.c -v

5、有多个源码文件需要生成一个可执行文件

//分步执行

gcc -o a.o a.c

gcc -o b.o b.c

gcc -o c.o c.c

gcc -o hello a.o b.o c.o//一步执行

gcc -o hello a.c b.c c.c

二、引入Makefile规则

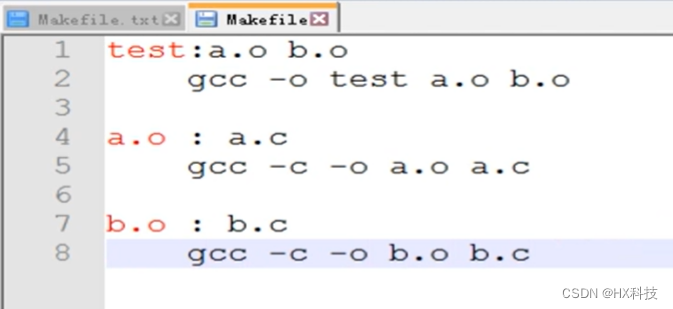

1、目标文件test依赖a.o和b.o两个文件,a.o依赖a.c文件,b.o依赖b.c文件

三、Makefile语法

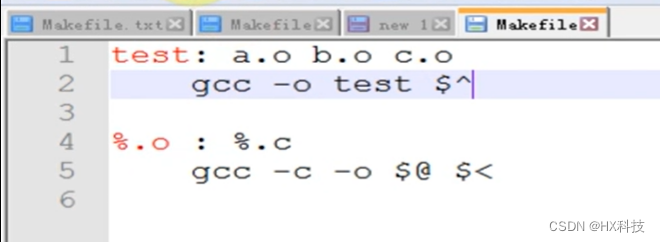

1、通配符用法

(%:表示任意),($@:目标),($<:第一个依赖),($^:所有依赖)

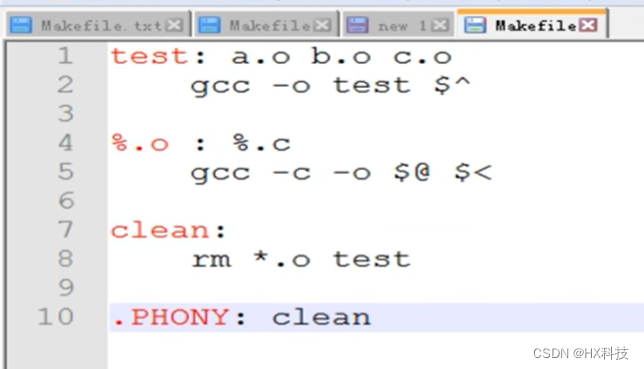

2、假想目标

正常情况下执行make clean是没有问题的,若文件目录下本来就有了clean文件,make clean就无法正常执行,所以要将Makefile中的clean设置成一个假想目标

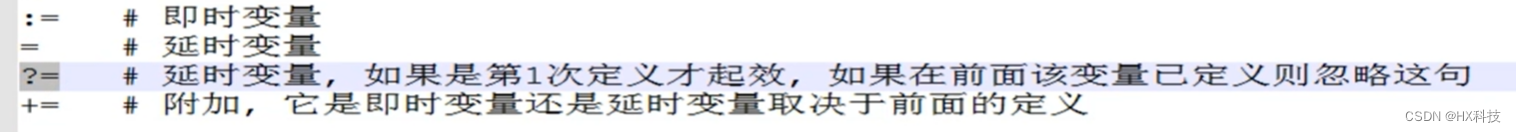

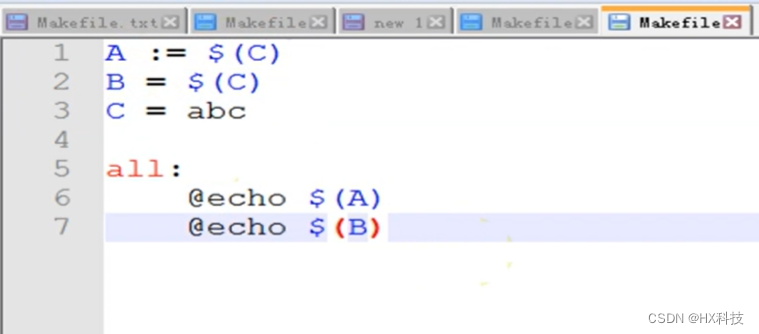

3、延时变量(B = xxxx)、即时变量(A := xxxx)

注意:引用变量是用$(变量名),使用echo打印变量时,不想看到指令就在echo前加一个@符号

说明:打印结果是变量A打印为空,变量B打印为ABC

原因:变量A在定义的时候变量C还没定义所以是空,变量B是延时变量只要在用到的时候才会看变量C的值是多少

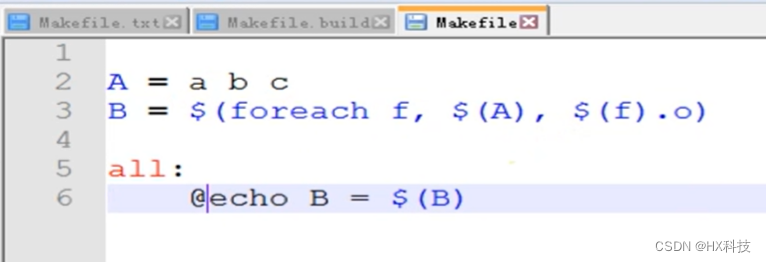

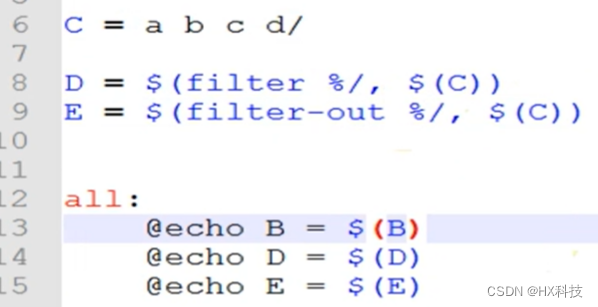

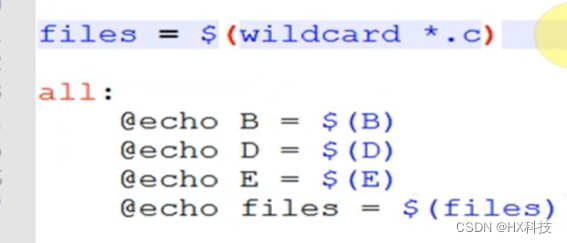

4、Makefile函数

说明:变量B会打印a.o b.o c.o

解释:foreach函数操作变量A中被空格隔开的字符都加上.o

说明:变量D会打印d/,变量E会打印a b c

解释:filter函数操作变量C中符合%/这种类型的字符,filter-out函数操作变量C中符合%/这种类型剩下的所有字符

说明:变量files会打印当前文件夹下所有的.c文件

解释:wildcard函数会查找当前文件夹下所有的.c文件,获取到所有的文件名

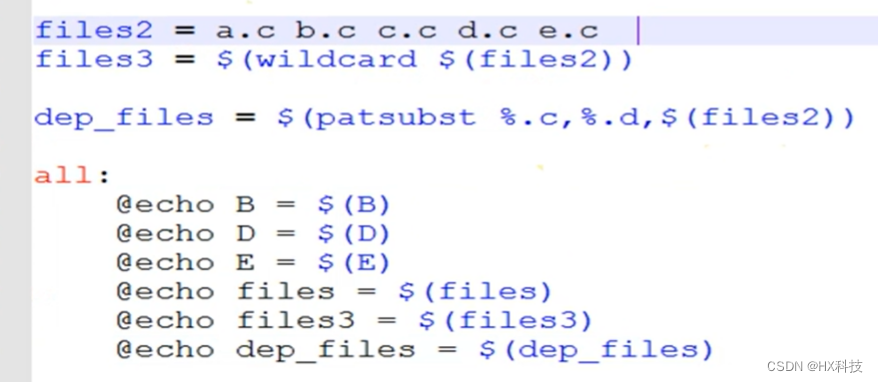

说明:变量dep_files会打印a.d b.d c.d e.d

解释:patsubst函数会操作files2中的所有文件名替换成a.d b.d c.d e.d

四、使用Makefile

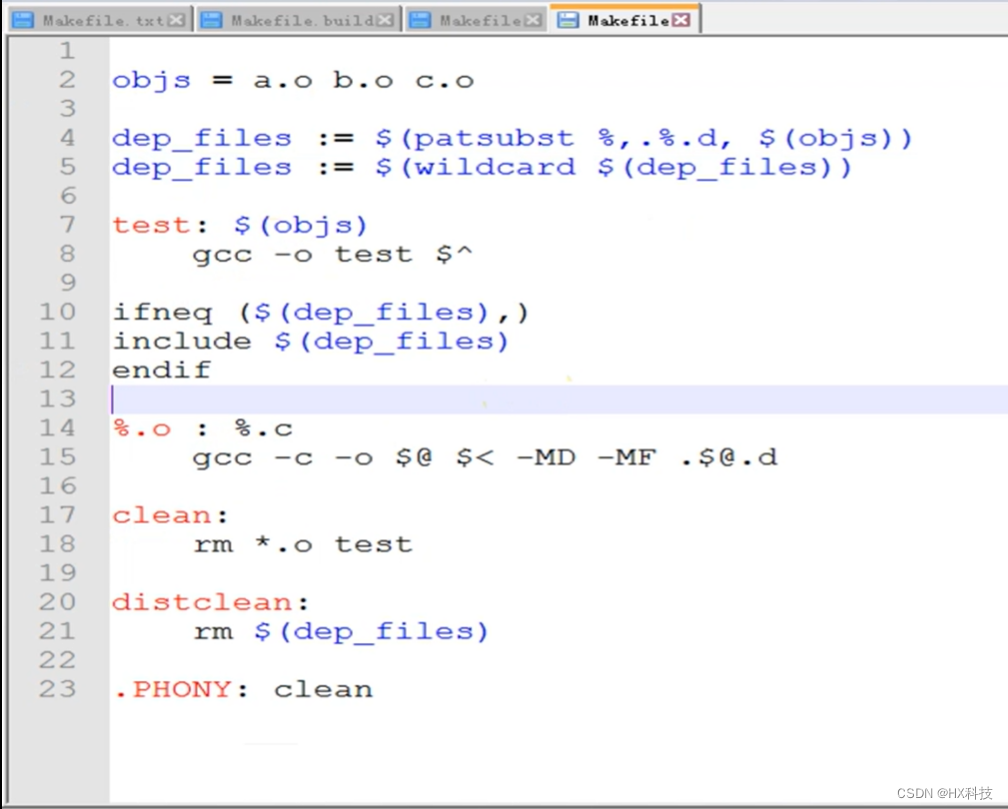

1、一个基础的自动包含依赖的Makefile文件的规范写法

说明:

2行:变量objs中包含所有的依赖文件

4行:变量dep_files是获取到所有的依赖文件名字

5行:变量dep_files是获取到所有的真实存在的依赖文件的名字

7行:目标以及生成目标的所有依赖

8行:生成目标的指令

10行:判断依赖文件是否是空

11行:依赖文件不为空的话就包含进来

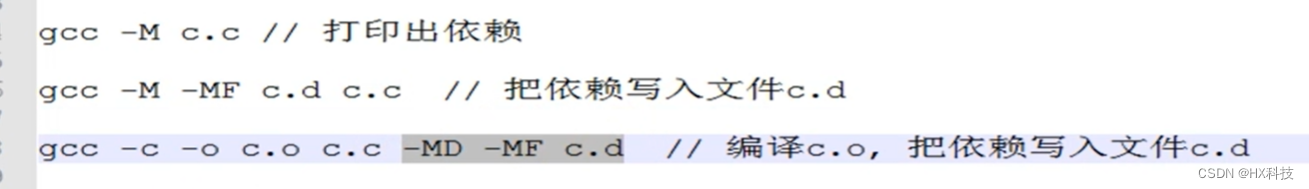

14行:所有的.c生成.o

15行:生成所有的.o文件并且生成所有的依赖文件

18行:清除编译文件

21行:清除依赖文件

objs = a.o b.o c.odep_files := $(patsubst %,.%.d, $(obis))

dep_files := $(wildcard $(dep_files))test: $(objs)gcc -o test $^ifneq ($(dep_files),)

include $(dep_files)

endif%.o:%.cgcc -c -o $@ $< -MD -MF .$@.dclean:rm *.o test

distclean:rm $(dep_files)

PHONY: clean

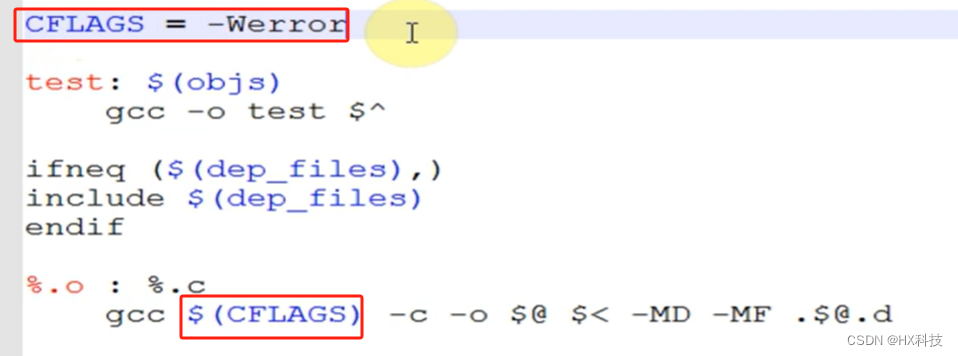

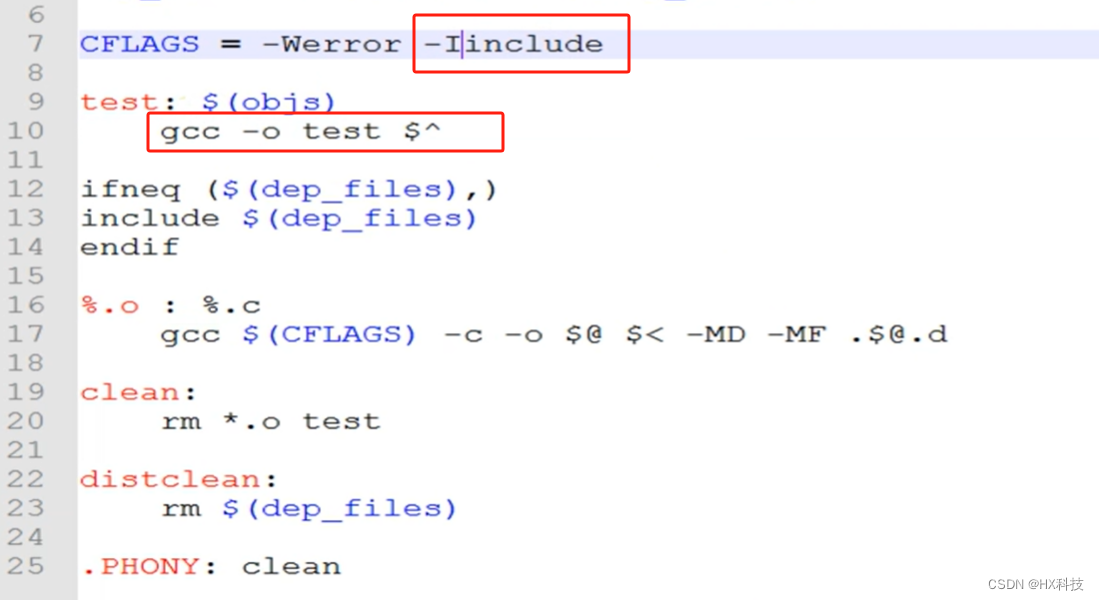

2、CFLAGS用法

说明:作为编译参数给gcc指令使用(把所有的警告当做错处处理)

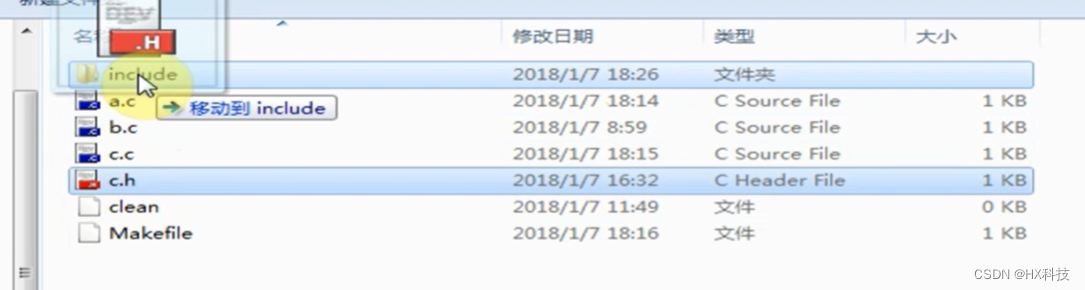

设置默认头文件目录,这样在编译的时候会直接去include文件夹找头文件

说明:设置当前目录为头文件路径,这样的在使用头文件就可以写成#include<b.h>