集成VCO-Cadence ADE相位噪声分析

- 简介

- 环境

- 软件

- 工艺

- 参考

- 振荡器原理图

- 相位噪声

- 说明

- pss设置

- 1

- 2

- 3

- 4

- pnoise设置

- 1

- 2

- 3

- 4

- 5

- 结果

简介

本文主要是使用Cadence ADE仿真1GHz交叉耦合振荡器,得到相位噪声曲线,主要记录仿真设置过程,仅供参考,如有问题,欢迎讨论。

环境

软件

IC 618

工艺

TSMC-65nm(OA)

参考

《CMOS模拟集成电路设计与仿真实例——基于Cadence ADE》

[资料] 基于Cadence的IC设计

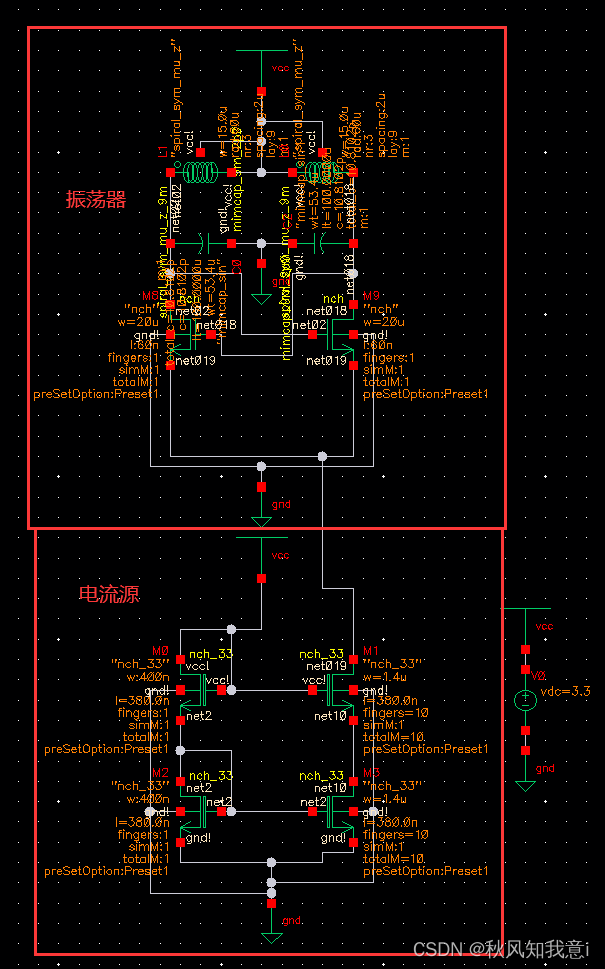

振荡器原理图

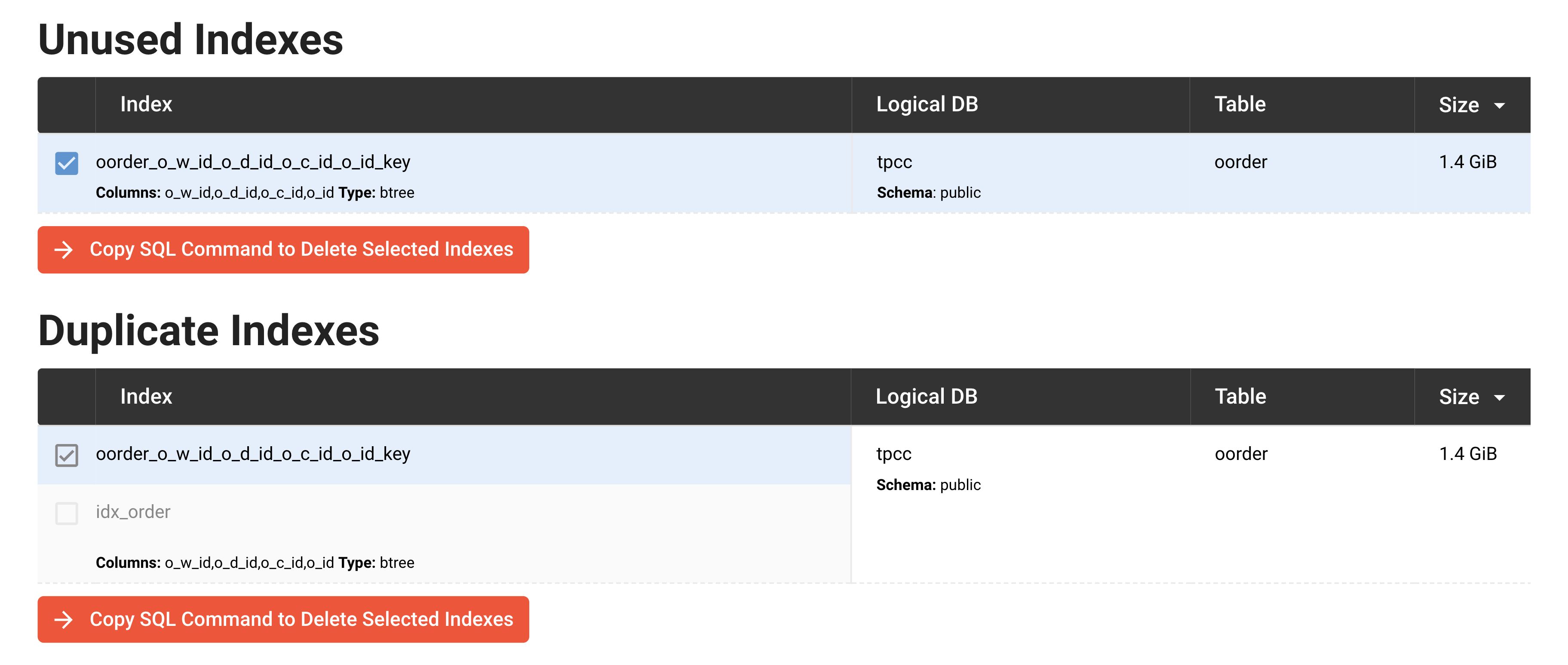

如图所示,上框框表示的是振荡频率在1GHz交叉耦合振荡器,而下框框表示的是2mA电流源,整体供电为3.3V。

#trans

相位噪声

说明

周期性的噪声分析主要使用“Pnoise analysis”,即“Periodic Noise Analysis”。“Pnoise analysis”和传统的噪声分析类似,只是它还包含了频率的变换效应。所以,用它来模拟例如混频器、开关电容滤波器以及其他一些周期性的电路的噪声行为很有用。它特别在模拟自激电路,例如振荡器的相位噪声时很有用。

在进行“Pnoise analysis”仿真之前,必须先做“PSS analysis”的仿真。“PSS analysis”是在一个指定的基波频率下计算电路的周期性稳态响应,而且仿真时间与电路的时间常数无关。“PSS analysis”决定了电路的周期性工作点,而这恰恰给**“PAC”,“PSP”,“PXF”和“Pnoise”这些仿真提供了起点**。“PSS analysis”在自激电路和非自激电路中都可以工作。然后,“Pnoise analysis”以在之前做的“PSS analysis”中的找到的工作点进行线性化,而正是由于被线性化后的电路的周期性随时间变化才产生了频率的变换。此外,电路中各种元件由于工作点周期性随时间变化而产生的噪声也被包含在内。这样,在电路输出端的时间平均噪声就以频谱的形式计算和表现,同时,在指定电路的输出时可以是一对接点或者一个探测点。

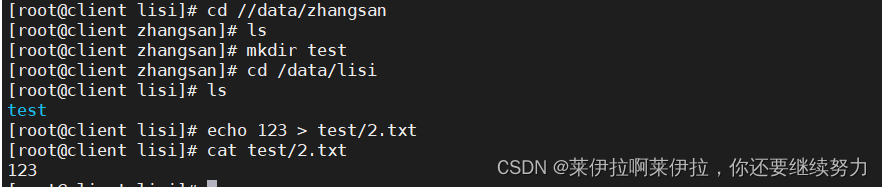

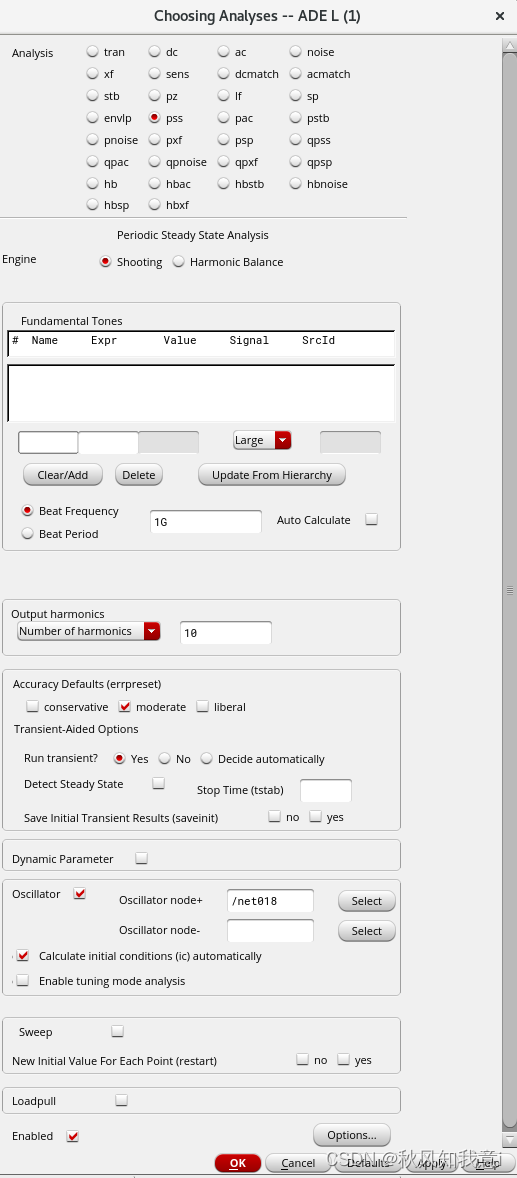

pss设置

1

在“Fundamental Tones”栏中设置“Beat Frequency”或者“Beat Period”,两者互为倒

数关系,这个“Beat Frequency”应该设为接近振荡电路的振荡频率。

2

在“Output harmonics”中有四个选项“Number of harmonics”,“Select from range”,“Array

of coefficients”,和“Array of indices”。选择“Number of harmonics”,然后在旁边的栏

中输入一个合适的数字。

3

在“Accuracy Defaults”中选择“moderate”。

4

选择“Oscillator”,表示我们仿真的是一个震荡器电路。在“Oscillator node”中点击

“Select”,在电路原理图中选择震荡电路的输出端口。“Reference node”可以不选择,

表示默认的“gnd”端。

“PSS analysis”的设置就完成了。

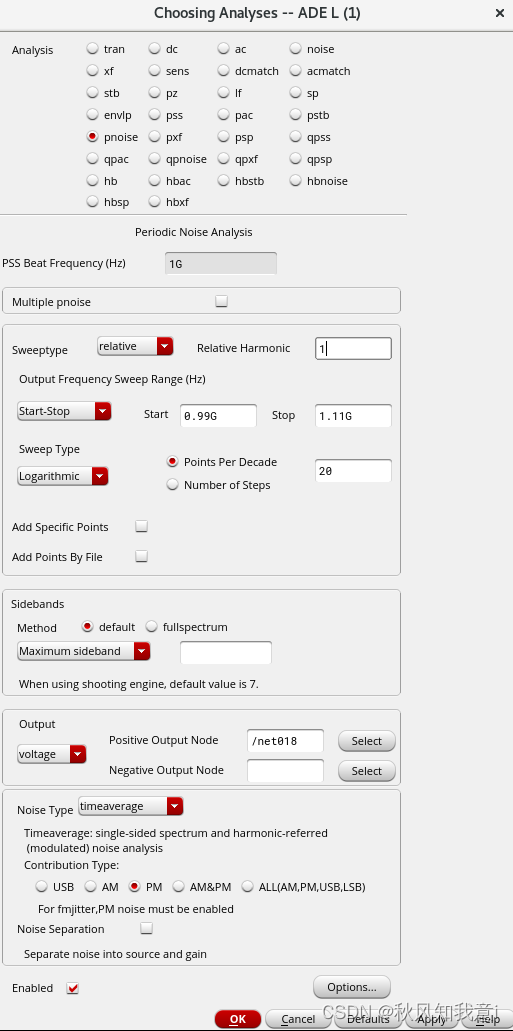

pnoise设置

1

下面对“Pnoise analysis”进行设置在“Sweep type”中选择“Relative”,然后再右边的“Relative Harmonic”中填入1,它表示相对于基波频率的偏离范围。

2

在“Frequency Sweep Range”中选择“Start-Stop”,填入起始和终止的频率。

3

在“Sweep Type”中选择“Logarithmic”,在其右边选择“Points Per Decade”,填入合适的数字。

4

在“Sidebands”中选择“Maximum sideband”,填入合适的数字,它的默认数字为 7。

5

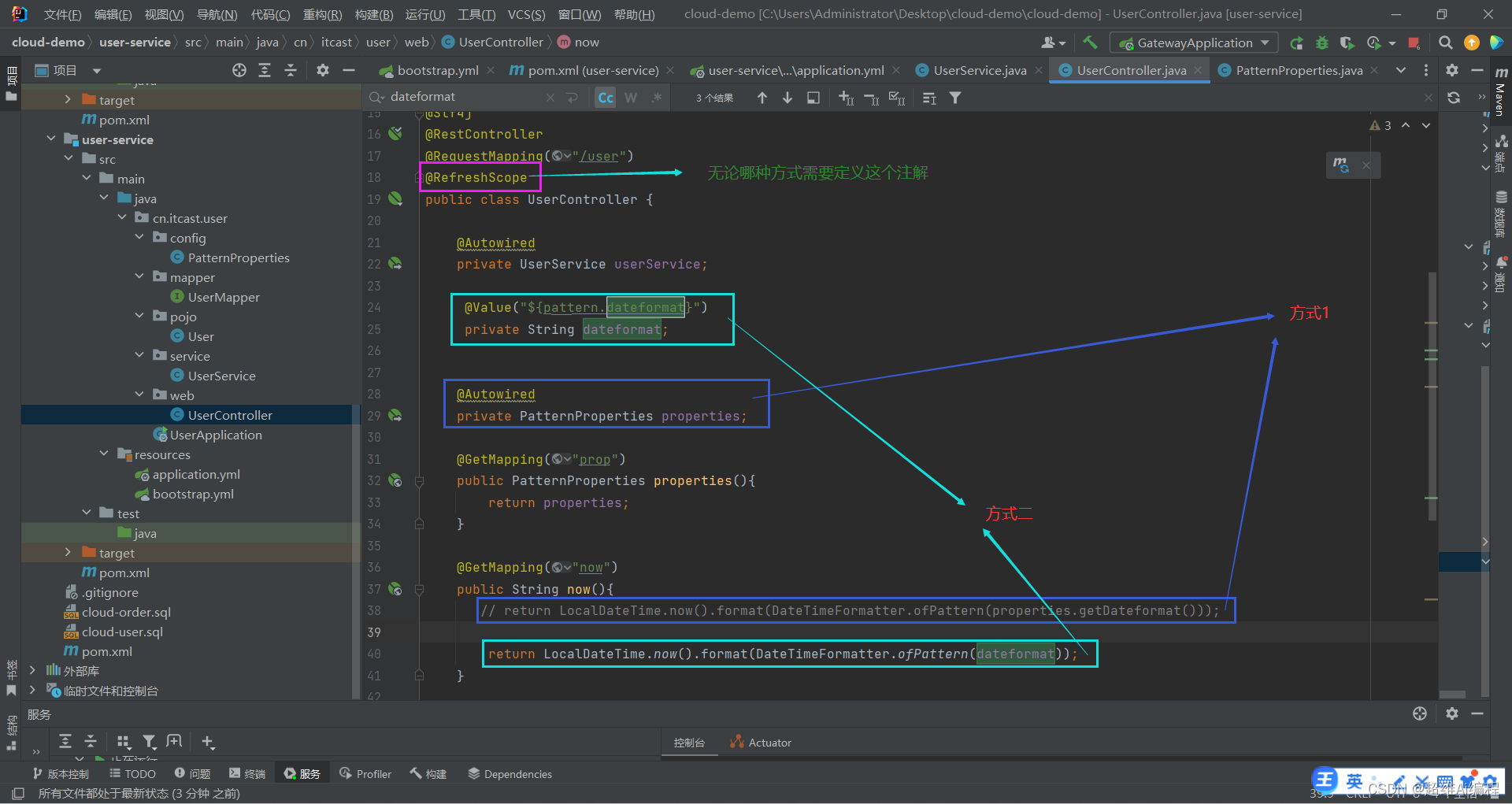

在“Output”中选择“voltage”,在右边的“Positive Output Node”选项中点击“Select”,在电路原理图中选择震荡电路的输出端。“Negative Output Node”选项可以不选择,表示默认的“gnd“端。

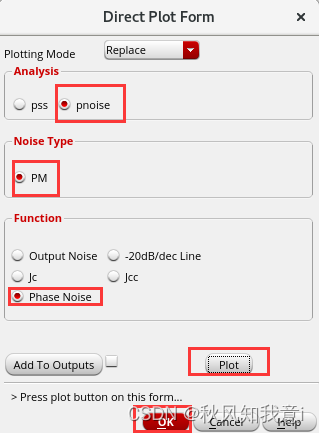

点击仿真,仿真完后,点击Results=>Direct Plot=>Main Form,完成如下设置,

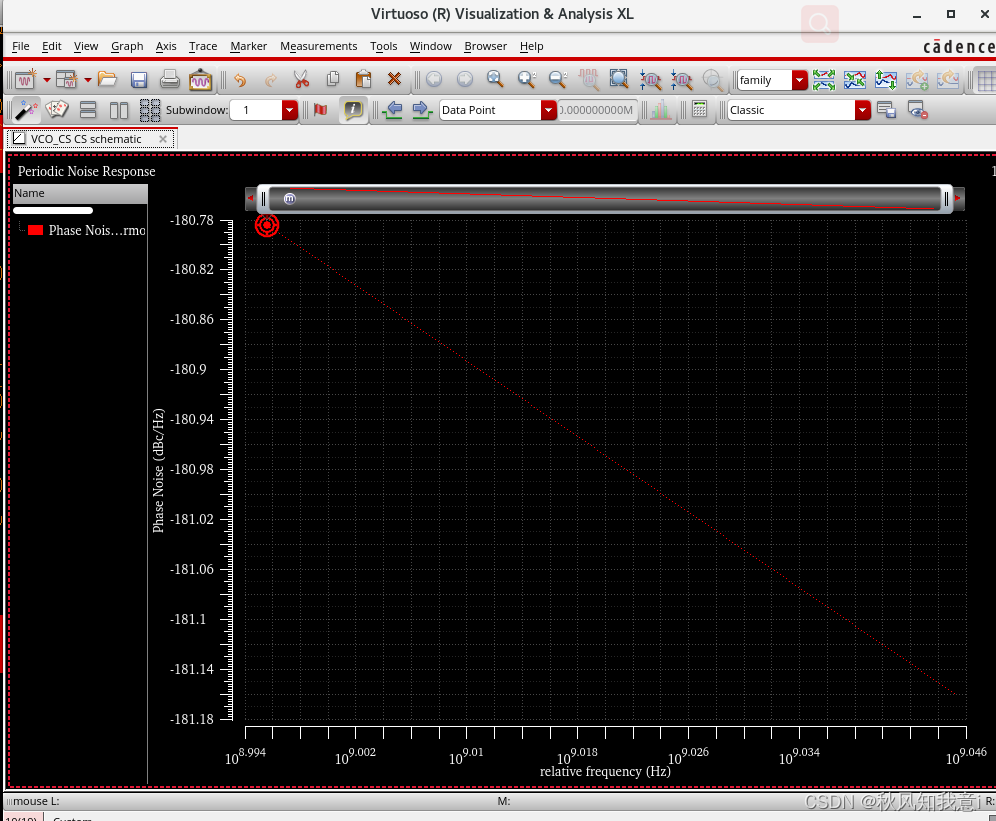

结果

相位噪声的如上图所示,在1MHz的偏移处明显小于-180dBc/Hz。

](https://img-blog.csdnimg.cn/440eab19c0854984a1499a97d26db947.png#pic_center)