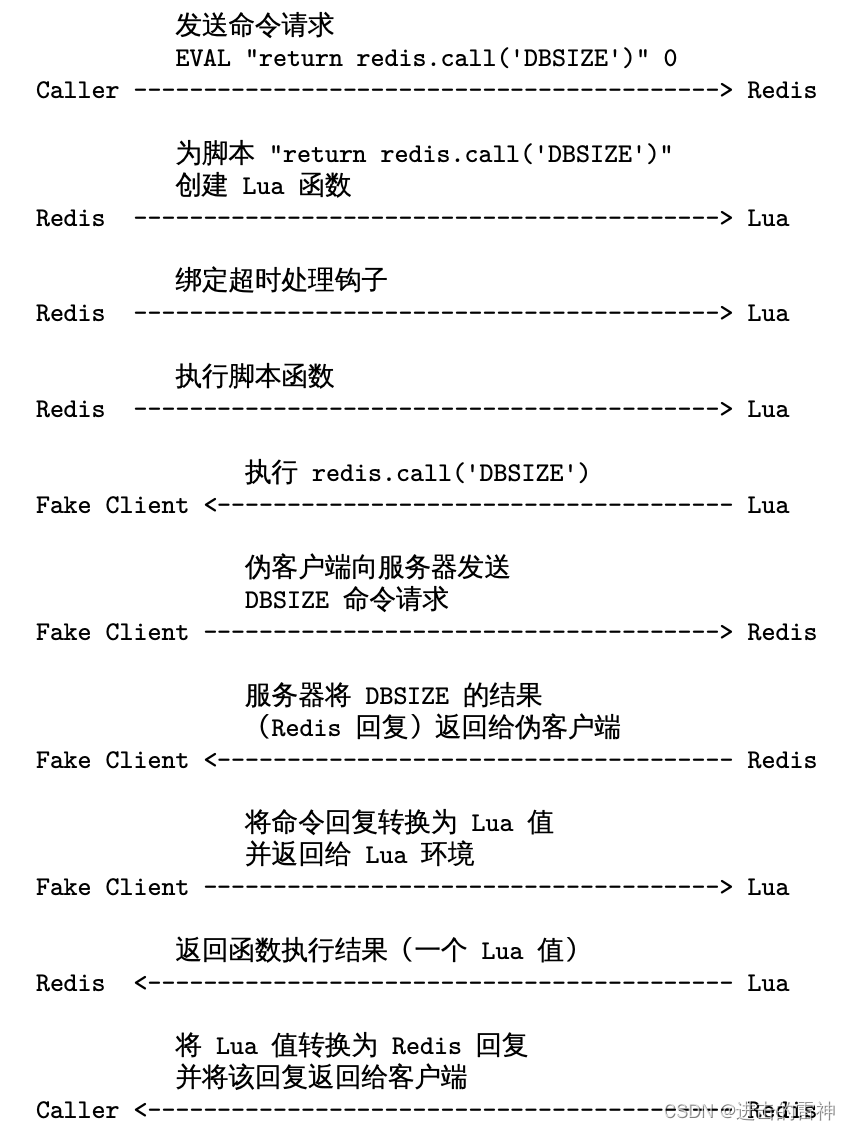

3.3 VREF+/VREF-引脚

VREF+和VREF-是STM32中用于提供参考电压的引脚。如下图:

VREF+引脚可以连接一个单独的外部参考电压,范围在2.0V~VDDA,但不能超过VDDA,否则就超过了模拟器件的最大供电电压。在100引脚的封装中,VREF-是A/D的参考,当需要使用时,必须绑定到VSSA(使得所有模拟器件的参考都相对于VSSA)。

VREF-引脚是参考电压输入引脚负极。在64及更少的引脚中,VREF-和VREF+是不可用的,在内部被接到一个ADC电压提供源(VDDA)并接地(VSSA),此时参考电压就是AD的工作电压了。

3.4 VBAT引脚

VBAT在电路中代表电池工作模式专用引脚。它主要用作给内部RTC(实时时钟)供电,在主要电源(VDD)掉电的情况下,可以确保RTC的内部工作,通常采用钮扣式电池。在不需要使用RTC的情况下,VBAT引脚可以和VDD引脚接在一起。

3.5 NRST引脚

NRST引脚是STM32F的异步复位脚。当NRST输入低电平的时候,MCU处于复位状态,重设所有的内部寄存器,及片内几十KB的SRAM。当NRST从低电平变高时,PC指针从0地址开始。但是复位的回时候不会将STM32F片内RTC的寄存器以及后备存储器重置,因为它们是用电池通过专门的VBAT脚供电。

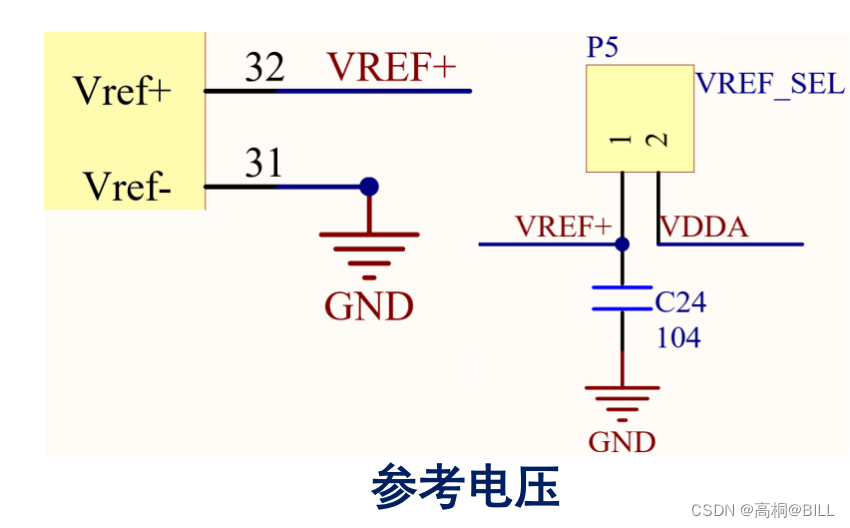

3.6 BOOT0/BOOT1引脚

BOOT0和BOOT1是STM32微控制器的两个重要引脚,它们在芯片复位时的电平状态决定了芯片复位后从哪个区域开始执行程序。

- BOOT0:这是一个普通输入/输出引脚,用于配置芯片的启动模式。当BOOT0引脚为低电平时,芯片将从Flash存储器中启动;当BOOT0引脚为高电平时,芯片将从系统引导加载器(System Bootloader)或其他外部存储器(如ROM或RAM)中启动(取决于芯片的配置)。

- BOOT1:这也是一个普通输入/输出引脚,用于定义额外的启动模式。

需要注意的是,一般不使用内置SRAM启动(BOOT1=1 BOOT0=1),因为SRAM掉电后数据就丢失。多数情况下,SRAM只是在调试时使用,也可以做其他一些用途。在ISP下载的情况下,BOOT0=1,BOOT1=0 ,下载完成后,把BOOT0的跳线接回0,也即BOOT0=0,BOOT1=0 。

3.7晶振引脚

说到晶振引脚之前,我们先聊聊什么是晶振。

通常情况下,对于一些成熟的STM32开发板,在其电路原理图的设计中,MCU外接了两个晶振。一个是低速晶振 ,另一个是高速晶振。

而晶振是一种用于产生稳定时钟信号的电子元件,通常由石英晶体制成。晶振的作用是提供一个基准时钟信号,用于同步和控制微控制器、计算机、通信设备等数字系统的操作。晶振的稳定性、精度和频率范围对于数字系统的性能和稳定性至关重要。晶振广泛应用于各种电子设备中,如计算机主板、嵌入式系统、通信设备、计时器、电子钟表等。

晶振的基本工作原理是利用石英晶体的压电效应来产生高频振动。当在石英晶体上施加交变电场时,晶体将会产生机械变形,这种变形会导致晶体内部离子的移动并形成一个稳定的振荡。这个振荡的频率取决于晶体的物理特性,如尺寸、形状和材料等。通过控制交变电场的频率和幅度,可以精确地控制晶体的振荡频率,从而得到所需的时钟信号。

上面说到MCU会外接晶振,为什么是外接呢?

晶振通常是外接而不是封装到IC内部,这主要是因为实用性和成本的问题。早些年,芯片的生产制作工艺也许还不能够将晶振做进芯片内部,但现在已经可以实现。然而,将晶振集成到芯片内部会增加成本,并且一旦晶振封装进芯片内部,其频率也就固定了,无法再更换。相比之下,将晶振作为外部元件,可以根据需要自由地更换晶振来给芯片提供不同的频率。此外,晶振和芯片的材料是不同的,芯片(集成电路)的材料是硅,而晶体则是石英(二氧化硅),无法直接做在一起,但可以封装在一起,只是成本会比较高。因此,从实用性和成本的角度考虑,晶振通常是作为外部元件连接在芯片上,而不是封装到IC内部。

那么mcu又为什么需要外接两个晶振呢?

MCU需要一个高速晶振和一个低速晶振的原因在于它们各自的作用和优势。

首先,外部高速晶振是一种用于提供高精度时钟信号的晶振,它通常用于微处理器和微控制器的时钟输入。由于外部高速晶振的精度较高,因此可以保证系统时序的准确性,从而提高系统的稳定性和可靠性。与此同时,外部高速晶振还能够提供更高的时钟频率,使处理器的工作速度更快。因此,外部高速晶振是很多电子设备中必不可少的一个组成部分。

其次,低速晶振则是一种用于提供低精度时钟信号的晶振,它通常用于计时器、时钟、闹钟等电路中。虽然低速晶振的精度较低,不能用于要求高精度时序的电路,但在一些要求低功耗的电路中,低速晶振是一个比较好的选择。因为低速晶振的频率较低,所以在工作时需要的能量也相应较少,从而能够实现更低的功耗。

综上所述,MCU需要一个高速晶振和一个低速晶振是因为高速晶振可以提供高精度、高频率的时钟信号,提高系统性能和稳定性;而低速晶振则可以在低功耗电路中发挥作用,减少能量消耗。

3.7.1 高速晶振电路(OSC_IN/OSC_OUT)

OSC_IN和OSC_OUT是STM32单片机上的外部时钟输入和输出引脚。它们主要用于接入外部晶振,为系统提供时钟源。

- OSC_IN引脚:通常用来连接外部振荡器或晶振的输入端,以获取稳定的时钟信号。这个信号可以是任何频率的时钟源,但需要与单片机的工作频率相匹配。

- OSC_OUT引脚:是单片机内部的时钟输出引脚,它可以将单片机内部产生的时钟信号输出到其他器件或系统中。这个时钟信号的频率和相位可以根据需要进行调整。

总之,OSC_IN和OSC_OUT引脚是STM32单片机中非常重要的时钟引脚,它们为单片机提供了稳定的时钟信号,从而保证了系统的正常运行。

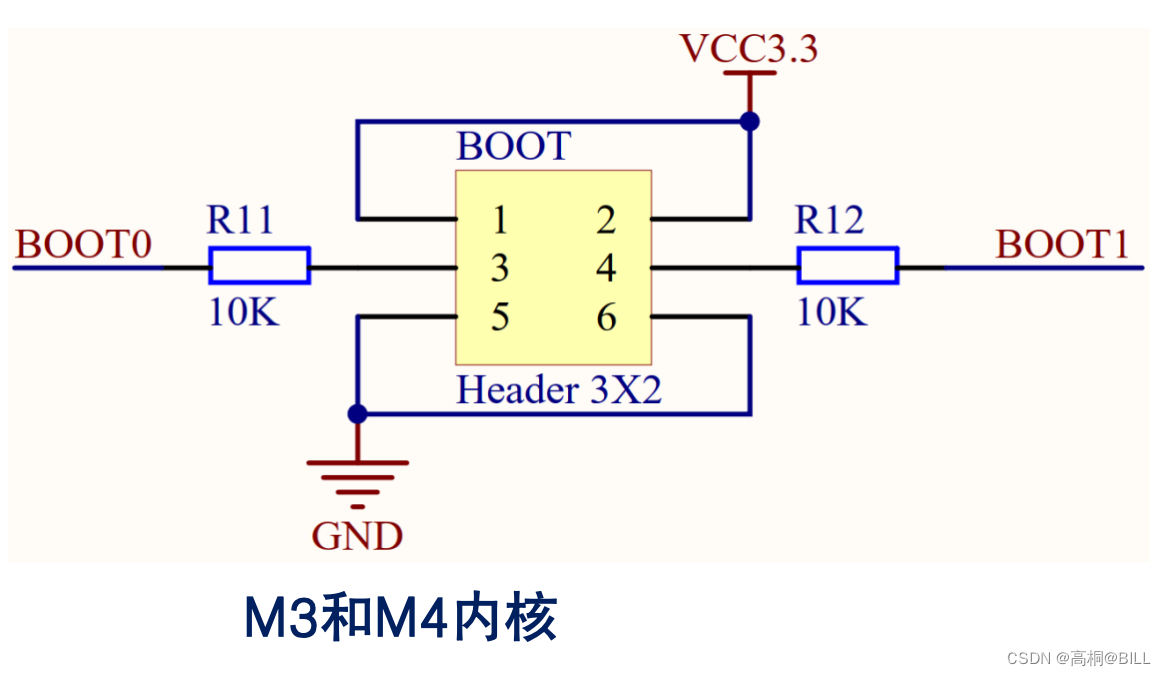

3.7.2 低速晶振电路(OSC_IN32/SOC_OUT32)

OSC_IN32和OSC_OUT32引脚是微控制器或处理器上的时钟输入和输出引脚,用于与外部时钟源连接。

OSC_IN32是外部时钟输入引脚,用于接收来自外部时钟源的时钟信号。这个外部时钟源可以是一个晶体振荡器、陶瓷振荡器或其他类型的时钟发生器。通过连接外部时钟源到OSC_IN32引脚,微控制器可以从外部源获取时钟信号,并基于该信号进行工作。

OSC_OUT32是外部时钟输出引脚,用于将微控制器的内部时钟信号输出到外部设备。通过这个引脚,可以将微控制器的时钟信号传递给其他需要同步的电路或设备。例如,如果有一个外部模块需要与微控制器的时钟同步工作,可以通过连接OSC_OUT32引脚到该模块的时钟输入引脚来实现同步。

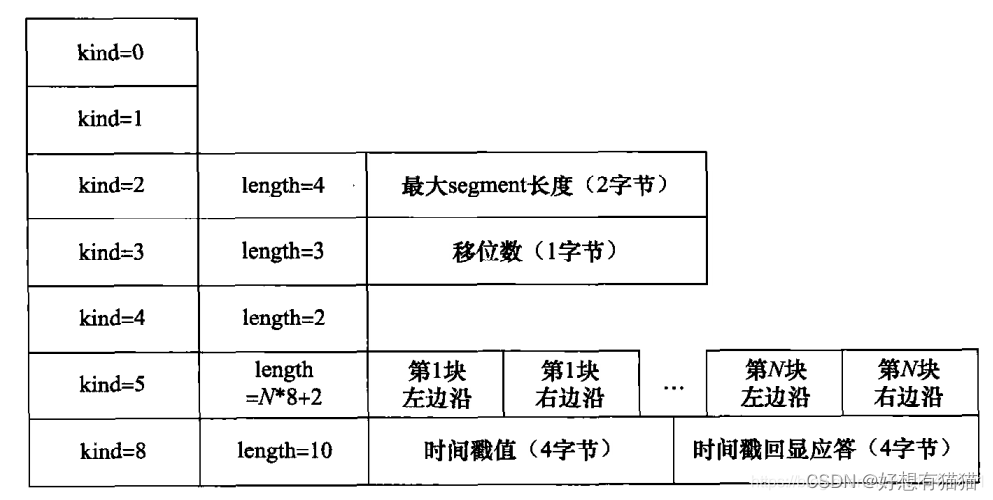

3.9 SWCLK/SWDIO引脚

SWCLK/SWDIO引脚是串行线调试(Serial Wire Debug,SWD)接口的两个引脚。SWD是一种用于微控制器调试和编程的串行通信协议。

- SWCLK(Serial Wire Clock):串行时钟线。它用于向目标设备发送时钟信号,控制数据传输的速度。SWCLK信号由调试器或编程器生成,用于同步与微控制器之间的通信。

- SWDIO(Serial Wire Data Input/Output):串行数据输入/输出线。它用于向目标设备发送或接收数据。当调试器或编程器需要与微控制器进行通信时,它通过SWDIO线发送命令和数据,并从SWDIO线接收响应和数据。

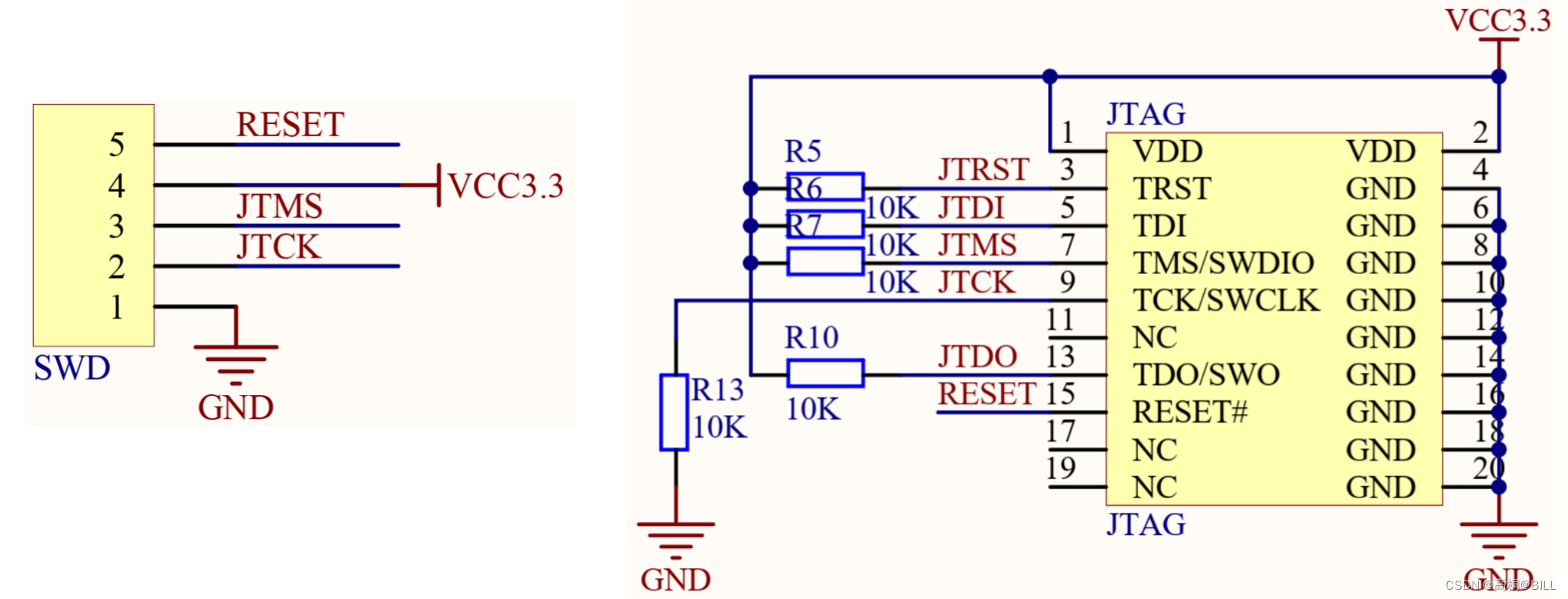

下载调试电路,具体如下

SWD接口的主要优势是它仅需要两个引脚(SWCLK和SWDIO),与使用传统的JTAG接口相比,可以节省引脚资源。此外,SWD接口还具有高速、可靠和低成本的特点,因此在许多微控制器应用中得到了广泛应用。

四,附录

前文中的电路图中出现了一些专有名词,这里简单介绍下:

- 10K

10K电阻是一种电子元件,其电阻值为10000欧姆(Ω),也可以表示为10KΩ。它通常用于控制电流在电路中的流动,以调节电路中电流的大小和方向。该电阻可以采用硬质材料制成,以吸收热量并防止电路过热。

此外,10K电阻也常用于限制不同电路部件的电流,如电容器、变压器和电池等。它还可以用来抑制电路中的空载损耗,减少电路中的干扰。在电力系统和电子电路中,10K电阻的应用非常广泛。

- GND

GND是电线接地端的简写,代表地线或0线。这个地并不是真正意义上的地,是出于应用而假设的一个地,对于电源来说,它就是一个电源的负极。电路图上和电路板上的GND(Ground)代表地线或0线,GND就是公共端的意思

- D1、D2

D1和D2可能是二极管或LED等电子元件的标识符。这些元件在电路中通常用于控制电流的方向或作为指示灯。

- C7

C7是一个电容器的标识符。电容器在电路中用于储存电荷,并在需要时释放电荷,以平滑电路中的电压波动或滤除噪声。

- R5、R6、R7

R5、R6和R7的标识符表示在电路图中存在三个不同的电阻器。每个电阻器都可能有特定的阻值和其他参数,这些参数会影响电路的性能和功能。