本教程仅以compactRIO(FPGA-RT)举例

1.系统配置

1.1软件安装

FPGA-RT

1. LabVIEW Development System (Full or Professional)

2. LabVIEW Real-Time Module

3. LabVIEW FPGA Module

4. NI-RIO drivers

1.2硬件配置

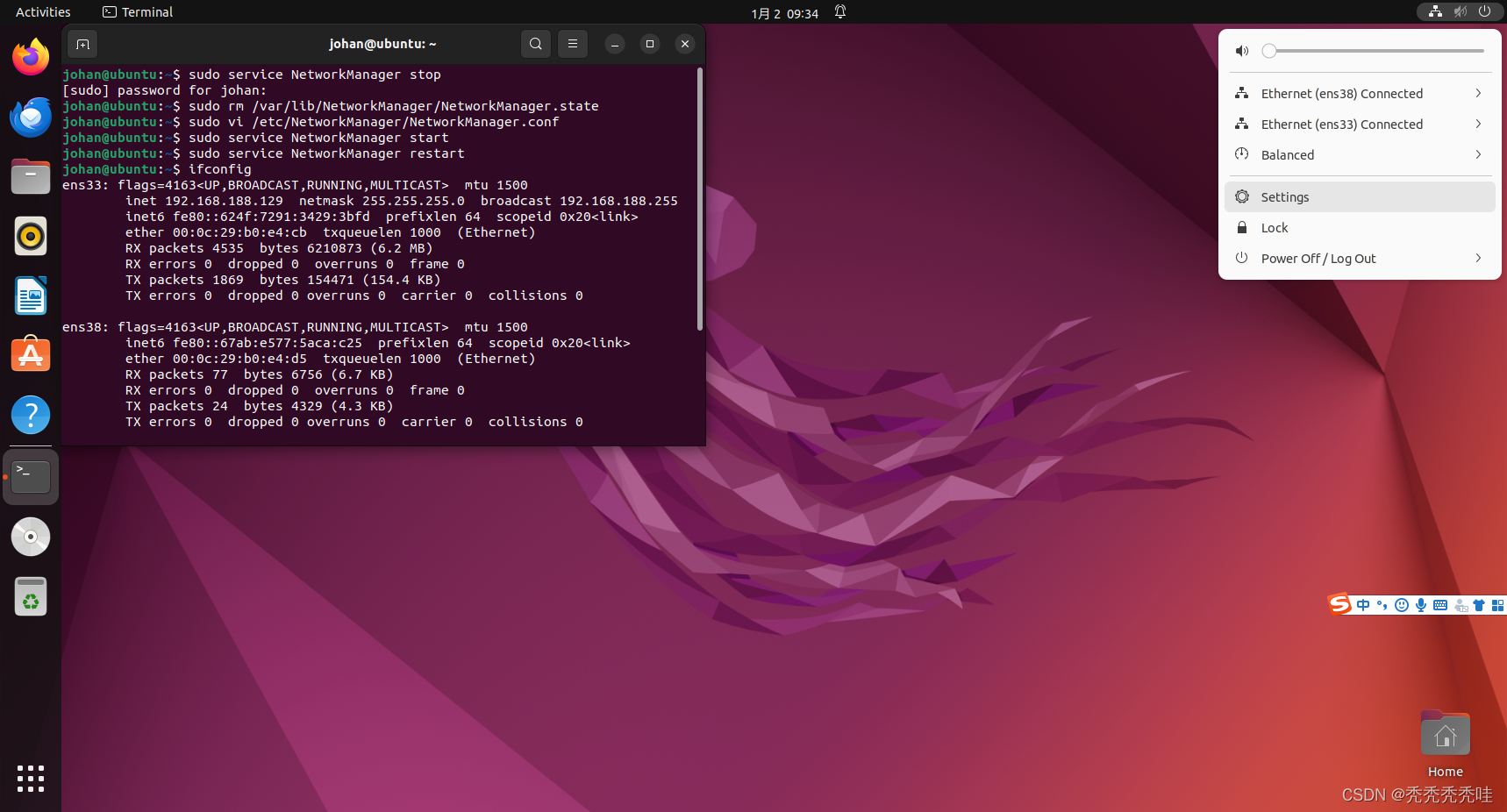

1.使用线缆连接CompactRIO至主机,并给CompactRIO供电。(如果已经被cRIO已经被配置为静态IP,则同样的需要设置一下电脑的IP)

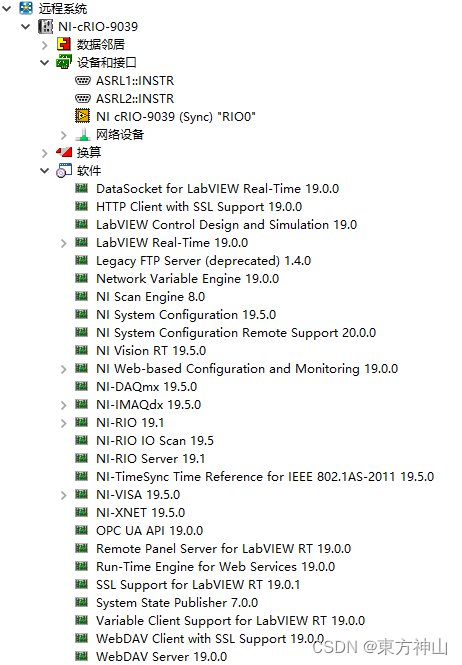

2.打开NI MAX软件,展开远程系统,RIO设备都在远程系统下面发现与配置。

3.展开cRIO的资源,检查设备和接口下面是否存在RIO Device,以及检查需要使用的软件都已经安装。如未安装则需要添加/删除NI RIO设备上的软件。

4.查看或cRIO网络状态。 cRIO的ip皆可在系统设置里查到(当前ip状态为上位机自动ip、cRIO自动ip,即为本地网络状态)。

如果需要修改网络设置,则需要在下面的网络设置里面将以太网适配器eth0的ip地址设置为静态IP,这样环境网络变化时也可以轻易搜索到cRIO机箱。

2.创建LabVIEW FPGA 项目

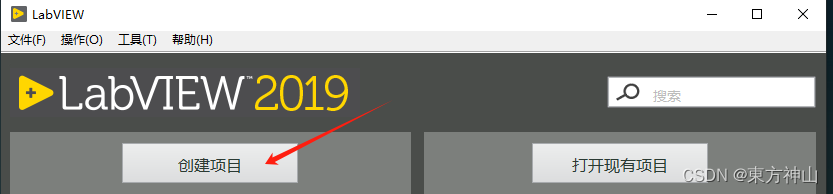

1.创建一个空项目。

2.添加cRIO终端。

搜索现有终端或设备,选择设备对应的类型 并选中搜索出来的设备,点击确定。

RIO编程模式选择 LabVIEW FPGA接口。

使用快捷键Ctrl+S保存项目改动。

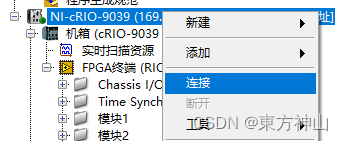

3.连接cRIO终端。如果连接成功则说明cRIO与主机通信正常,且RT终端旁边会出现一个绿色的点,此步骤非必须,直接部署程序的时候LabVIEW会自动连接RT终端。

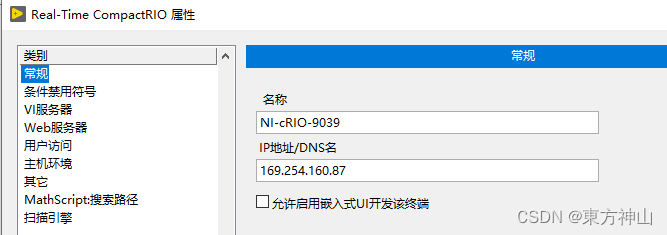

如果连接失败,则说明项目RT终端IP不匹配,则需要在NI MAX中查看RT设备的IP并检查当前主机的网口设置,同时在项目里修改IP(具体步骤为右击RT终端,属性,IP地址里修改)。

3.LabVIEW FPGA项目资源介绍

| 组件 | 说明 | |

|---|---|---|

|

| LabVIEW项目 | LabVIEW项目允许用户在开发计算机上开发应用时,管理VI和终端。LabVIEW项目文件包含对项目中文件的引用、配置信息、部署信息、生成信息等。 |

|

| 我的电脑 | 我的电脑(通常称为开发计算机)是开发LabVIEW项目的计算机。开发计算机是指运行支持的Windows平台的计算机,该计算机已安装LabVIEW和LabVIEW FPGA模块。 |

|

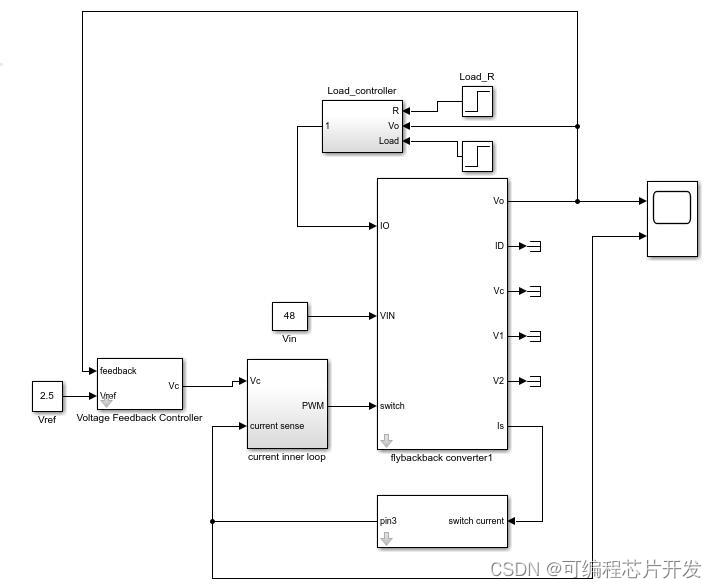

| RIO机箱 | RIO机箱放置并直接连接FPGA终端的I/O块至可互换的I/O模块,以实现高性能定时、触发和同步。 |

|

| 控制器 | 控制器直接连接RIO机箱,直接或通过网络与开发计算机通信。控制器包含一个嵌入式处理器,它运行实时操作系统(RTOS)或Windows。 |

|

| FPGA终端 | FPGA终端是一个可编程芯片,由逻辑块、I/O块和可编程互连资源组成,这些资源用于实现通过LabVIEW FPGA模块设计的数字电路。 |

|

| FPGA VI | FPGA VI是加载至FPGA终端并运行的VI。LabVIEW编译工具将FPGA VI转换为电路机制,以重新配置FPGA终端块和互连资源。 |

|

| 主控VI | 主控VI在控制器上运行,通过编程与FPGA VI通信。通过主控VI可记录数据、控制数据传输定时及创建一个带FPGA终端的系统,并将其用作组件。 |

|

| 用户界面VI | 用户界面VI在开发计算机上运行,并与主控VI通信。用户界面VI允许用户通过编程,与主控VI的输入控件和显示控件交互。在没有控制器的情况下,用户界面VI用作主控VI,并直接与FPGA VI通信。 |

|

| I/O | I/O是指FPGA系统的模拟和数字输入/输出。例如,热电偶、RTD、桥传感器、计数器和发生器等。关于支持的I/O的详细信息见指定硬件文档。 |

|

| 时钟 | 时钟通过指定FPGA系统的定时需求,控制FPGA VI的执行频率。如未包含额外的用于控制定时的代码,操作的执行频率由VI数据流确定。多数FPGA终端的默认时钟速率为40 MHz。 |

|

| 程序生成规范 | FPGA终端的程序生成规范指定用户编译FPGA VI时,LabVIEW创建哪个选项:

|