- 用二进制代码表示的计算机语言称为(机器语言 ),用助记符编写的语言称为(汇编语言)。

- 计算机硬件由(控制单元)(运算器)(存储器)、输入系统和输出系统五大部件组成。

- 十六进制数CB8转换为二进制数为(110010111000)。

- 某数x的真-0.1011B,其原码表示为(1.1011)。

- 在浮点加减法运算过程中,在需要(对阶)或(右规)时,尾数需要右移。

- 指令通常由(操作码)和(地址码)两部分组成。

- 要组成容量4K

8位的存储器,需要(8)片1K

1位的芯片并联,或者需要(4)片1K

8位的芯片串联。

- 中断处理过程包括(关中断)、(保护现场)、(执行中断服务程序)、(恢复现场)和(开中断)阶段。

- 操作数寻址方式包括(直接寻址),(间接寻址)、(立即寻址)、(隐含寻址)、(寄存器寻址)、(寄存器间接寻址)、(基址寻址)等。

- 动态RAM的刷新包括(分散刷新)、(集中刷新)和(异步刷新)三种方式。

- 高速缓冲存储器的替换算法有(先进先出)、(近期最少使用)。

- 影响流水线性能的因素有(数据相关)、(控制相关)和(资源相关)。

- 主存储器容量通常以KB为单位,其中1K=(1024B),硬盘的容量以GB为单位,其中1GB=()。

- 主存储器一般采用(动态RAM)存储器,CACHE采用(静态RAM)存储器。

- 世界上第一台计算机产生于(1946)年,称为(ENIAC)。

- I/O的编制可分为(不统一编址)和(统一编址),前者需要单独的I/O指令,后者可通过(访存)指令和设备交换信息

- CPU从主存取出一条指令并执行该指令的全部时间叫做(指令周期),它通常包含若干个(机器周期),而后者又包含若干个(时钟周期)。

- 计算机中各个功能部件是通过(总线)连接的,它是各部件之间进行信息传输的公共线路。

- 浮点数由(阶码)和(尾数)两部分组成。

- 禁止中断的功能可以由(中断允许触发器)来完成。

- 指令的编码中,操作码用来表明(所要完成的动作),N位操作码最多表示(

)中操作。

- 静态RAM采用(稳态触发器)原理存储信息,动态RAM采用(电容)原理存储信息。

- 典型的冯诺依曼计算机是以(运算器)为核心的。

- 系统总线按系统传输信息的不同,可分为三类:(地址总线)、(控制总线)、(数据总线)。

- Cache称为(双高速缓冲)存储器,是为了解决CPU和主存之间(速度)不匹配而采用的一项重要的硬件技术。

- 计算机系统中的存储器分为:(主存)和(辅存)。在CPU执行程序时,必须将指令存放在(主存)中,即(辅存)不能够直接同CPU交换信息。

- 在补码加减法运算中,采用双符号位的方法(变形补码)进行判断溢出时,若运算结果中两个符号位(不同),则表明发生了溢出。若结果的符号位为(01),表明发生正溢出,若为(10),表示发生了负溢出。

- 使用虚拟存储器的目的是为了解决(内存空间不足)问题。

- Cache介于主存与CPU之间,其速度比主存(快),容量比主存(小)很多。它的作用是弥补CPU与主存在(速度)上的差异。

- 一台计算机所具有的各种机器指令的集合称为该计算机的(指令集)。

- 选择器DMA控制器在物理上可以连接(多)个设备,而在逻辑上只允许连接(1)个设备,它适合于连接(高速)设备。

- DMA控制器中的字计数器用于记录要传送数据块的(长度),每传输一个字后计数器(加1)。

- 总线通信控制方式可分为(同步)式和(异步)式两种。

- DMA的含义是(直接存储器存取),主要用于连接(高速)外设,信息传送以(数据块)为单位传送。

- CPU的基本功能是(指令控制)、(操作控制)、(时间控制)、(数据加工)和(中断处理)。

- 由若干一位全加器构成多位加法器时,进位可采用(串行进位链)和(并行进位链)。

- 真值(超过)机器字长称为溢出。

- 时序控制方式有(同步控制)方式,(异步控制)和(联合控制)方式。

- DMA数据传送过程可以分为(预处理)、(数据传送)、(后处理)三个阶段。

- 主存芯片的地址译码驱动主要有两种方式,即(单译码)和(译码)。

- 流水线中常见的多发技术包括:(超标量技术)、(超流水线技术)和(超长指令字技术)。

- RISC称为(精简指令集)而CISC称为(复杂指令集)。

- 控制存储器是微程序控制器的核心部件,它存储着与全部机器指令对应的(微程序),它的每个单元中存储着一条(微指令)。

- 微指令中操作控制字段的编码方式有:(直接编码格式)、(字段直接编码格式)、(字段间接编码格式)和其它方式。

- 按照存储器的读写功能分类,存储器可分为RAM和ROM,RAM称为(随机存取存储器),ROM称为(只读存储器)。

- 计算机软件一般分为两大类:一类叫(系统软件),另一类叫(应用软件),操作系统属于(系统软件)。

- CRC码称为(循环冗余码),它具有(纠错)能力。

- 程序设计语言一般可分为三类:(机器语言)、(汇编语言)、(高级语言)

- 计算机系统的层次结构中,位于硬件之外的所有层次统称为(双虚拟机)。

- 浮点数中尾数用补码表示时,其规格化特征是(符号位与最高位数值相反)。

- N+1位二进制补码表示的取值范围是(

,

)。

- N+1位二进制无符号整数的取值范围是(0,

)。

- 一个定点数由(符号位)和(数值位)两部分组成。根据小数点的位置不同,定点数有(整数定点)和(小数定点)两种表示方法。

- 8位二进制补码所能表示的十进制整数范围是(-128)至(127),前者的二进制补码表示为(10000000),后者的二进制补码表示为(01111111)。

- 在浮点补码加减运算中,当运算结果的尾数不是(00.1····)和(11.0···)形式时,需要进行规格化操作(左归或右归)。

-

生成多项式G(X)=X*4+X"1+X0对应的二进制数为(10011),以此多项式进行CRC编码,其校验位的位数是(4)。

- 补码加减法中,(符号)连同数值位一同参加运算,(符号位进位)要丢掉。

- 在浮点加法运算中,主要的操作步骤是(对阶)、(尾数相加)、(结果规格化)、(舍入)、(溢出检查)。

- RAM的访问时间与存储单元的物理位置(无关),任何存储单元的内容都能被(随机访问)。

- 内存储器容量为256K时,若首地址为00000H,那么末地址的十六进制表示是(3FFFFH)。

- CPU是按照(地址)访问存储器中的信息。

- 寄存器(直接)寻址方式中,指令的地址码部分给出(寄存器编号),而操作数在(寄存器)中。

- 寄存器间接寻址方式中,指令的地址码部分给出的是(有效地址)所在的寄存器编号。

- 变址寻址方式中操作数的地址由(变址寄存器)与(地址码字段)的和产生。

- 直接寻址方式中,指令的地址码部分直接给出(有效地址),只需(一次)访存即可获得操作数。

- CPU中,保存当前正在执行的指令的寄存器为(IR),保存下一条指令地址的寄存器为(PC)。

- 控制单元由于设计方法的不同可分为(硬连线)控制器和(微程序)控制器

计算机组成原理复习题

本文来自互联网用户投稿,该文观点仅代表作者本人,不代表本站立场。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如若转载,请注明出处:http://www.hqwc.cn/news/323741.html

如若内容造成侵权/违法违规/事实不符,请联系编程知识网进行投诉反馈email:809451989@qq.com,一经查实,立即删除!相关文章

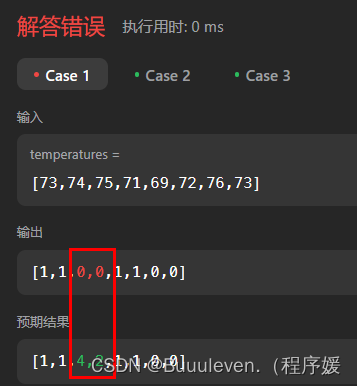

代码随想录算法训练营第五十八天|739. 每日温度、496.下一个更大元素I

代码随想录 (programmercarl.com) 739. 每日温度

栈里面存放的是元素的下标,确保栈里面的下标对应的元素是单调递增的。

如果栈里面存放的是元素的话,就没有办法定位到下标值,无法计算出距离,所以直接就存入下标。

class Solut…

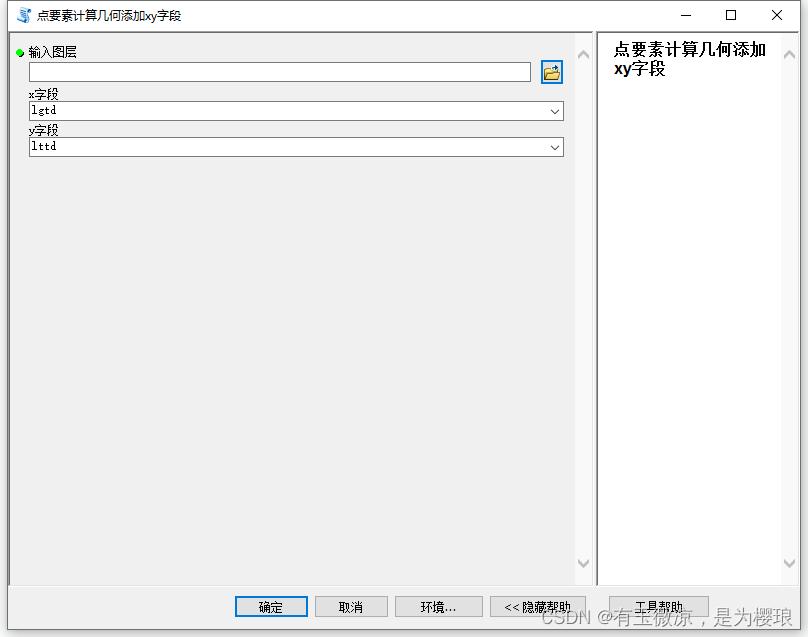

arcpy点要素生成经纬度字段脚本

说明

本脚本是用来简化操作的,正常情况下要生成经纬度字段,需要添加字段→填写字段名→写字段类型→字段计算器→计算几何。。。 而且经纬度都需要,要循环两遍。 本脚本就是为了简化以上操作的,安装后,打开脚本直接输…

助力各设备厂家矿鸿方案快速落地-触觉智能多款产品通过矿鸿认证

近日,触觉智能自主研发的多款产品:矿鸿核心板、本安矿鸿工业主板、矿鸿标准开发板、RK3568矿鸿控制器、本安矿鸿控制器、7寸矿鸿工控屏、10.4寸矿鸿工控屏、12.1寸矿鸿工控屏、15.6寸组态屏,10.1寸组态屏灯,通过矿鸿资质认证。

触…

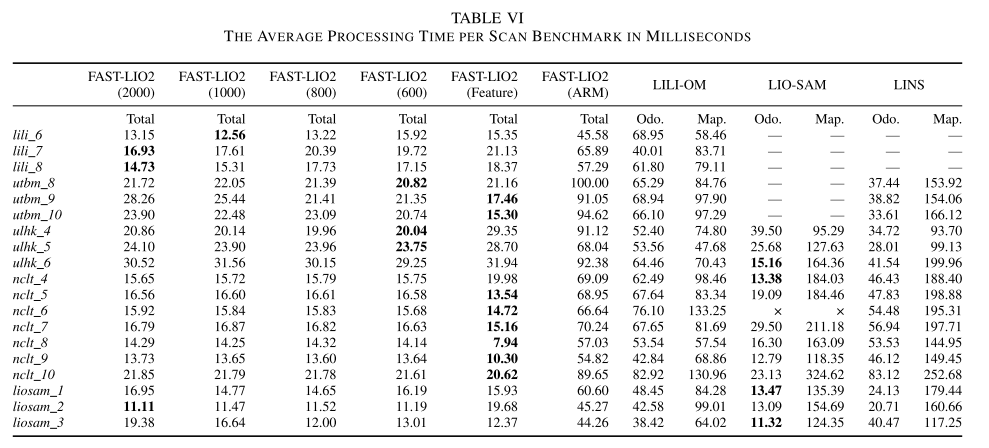

FAST-LIO2:论文和算法解析

文章目录 摘要一、简介二、相关工作2.1雷达惯导里程计2.2 建图过程中的动态数据结构 三、系统架构四、状态估计A. 卡尔曼模型1.状态转换模型2.测量模型 B.迭代卡尔曼滤波1. 预测过程2. 残差计算3.迭代更新 五、建图A.地图管理B.树的结构与创建1.数据结构2.ikd树的创建 C.地图的…

【C++期末编程题题库】代码+详解18道

适合期末复习c看,或者刚入门c的小白看,有的题会补充知识点,期末复习题的代码一般比较简单,所以语法上没那么严谨。本文所有题目要求全在代码块的最上面。

目录

1、设计复数类 2、设计Computer类

3、实现相加的函数模板

4、圆类…

【愚公系列】2023年12月 HarmonyOS应用开发者基础认证(完美答案)

🏆 作者简介,愚公搬代码 🏆《头衔》:华为云特约编辑,华为云云享专家,华为开发者专家,华为产品云测专家,CSDN博客专家,CSDN商业化专家,阿里云专家博主…

龙芯loongarch64服务器编译安装clang

前言 Clang 是一款开源的 C、C++、Objective-C 和 Objective-C++ 编程语言的编译器前端。它是 LLVM 编译器基础设施项目的一部分,具有优秀的性能、可扩展性和模块化设计。

Clang 提供了一系列主要功能,包括但不限于: 作为编译器前端,负责将源代码转换为中间表示形式(IR)…

VR与数字孪生:共同构筑未来的虚拟世界

随着科技的不断发展,数字孪生和VR已经成为当今热门的科技话题。作为山海鲸可视化软件的开发者,我们对这两者都有深入的了解。在此,我们将详细探讨数字孪生与VR的区别和联系。

首先,数字孪生(Digital Twin)…

Midas NFX 各版本安装指南

Midas NFX下载链接

https://pan.baidu.com/s/1cOifluBBobRgJZHZxuODvw?pwd0531

1.鼠标右击【Midas NFX 2023(64bit)】压缩包(win11及以上系统需先点击“显示更多选项”)【解压到 Midas NFX 2023(64bit)】。 2.打开解压后的文件夹,双击打开…

已知输入图像大小为n、卷积核大小为f、卷积步长s,填充大小为p,求解输出图像大小。

问题描述:已知输入图像大小为n、卷积核大小为f、卷积步长s,填充大小为p,求解输出图像大小。

问题解答:

输出图像的大小可以使用以下的计算公式确定: 为了举例说明,假设有以下参数:

输入图像大…

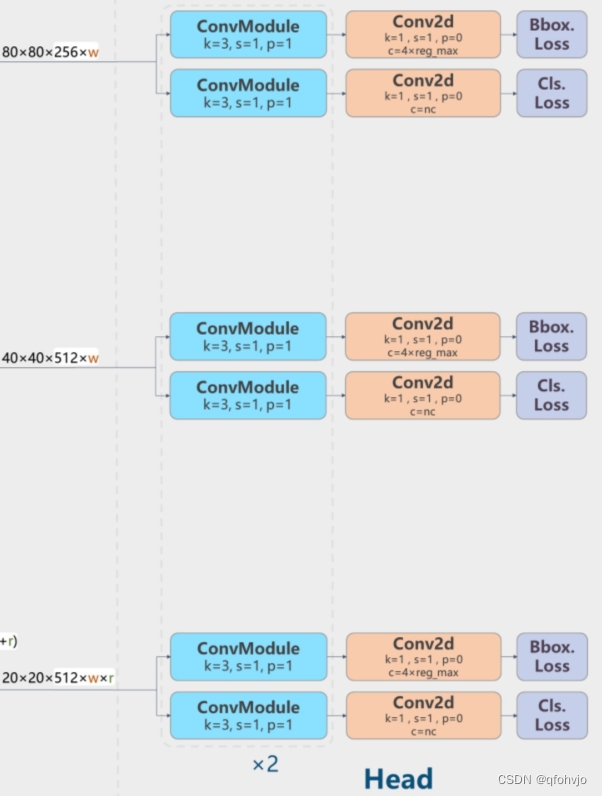

YOLOv8模型yaml结构图理解(逐层分析)

前言 YOLO-V8(官网地址):https://github.com/ultralytics/ultralytics 一、yolov8配置yaml文件

YOLOv8的配置文件定义了模型的关键参数和结构,包括类别数、模型尺寸、骨架(backbone)和头部(hea…