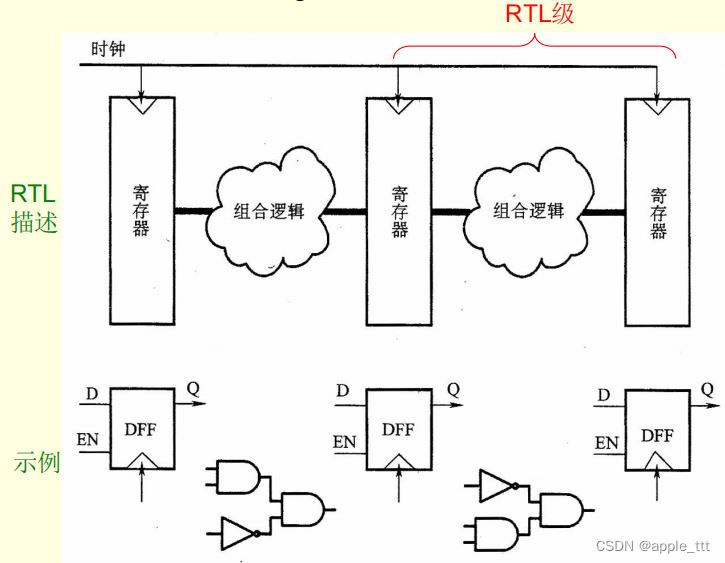

一、RTL级描述

二、Verilog与VHDL

- VHDL:源于Pasical和ADI语言,系统级描述较强,相对复杂、抽象,FPGA 代码设计用得较多

- Verilog:源于C语言,门级描述较强,相对简单、灵活、易于掌握,ASIC设计用得较多(其实FPGA用的也不少,国内大部分还是用Verliog)

三、不同层次的电路描述示例

我们以一个全加器为例,看其在不同的层次下的电路描述方式

3.1 布尔描述

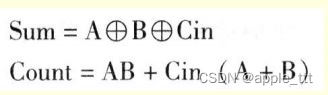

布尔描述一种逻辑表达形式,直接简洁地描述了电路逻辑:

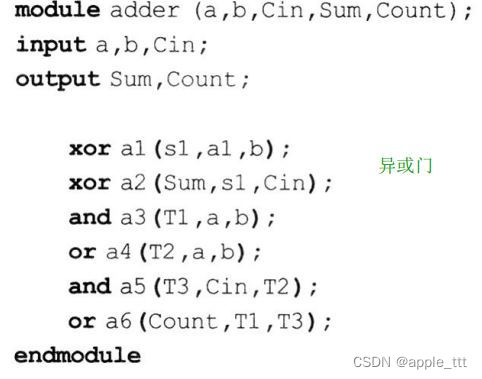

3.2 门级描述

门级建模比较接近电路底层,设计时主要考虑使用到了哪些门,然后按照一定的顺序连接线组成一个大的电路,所以注重的是门的使用,关键的语法在于门的实例化引用。一个完整的门级描述实例一般包含模块定义、端口声明,内部连线声明,门级调用等几个部分。

3.3 RTL级描述

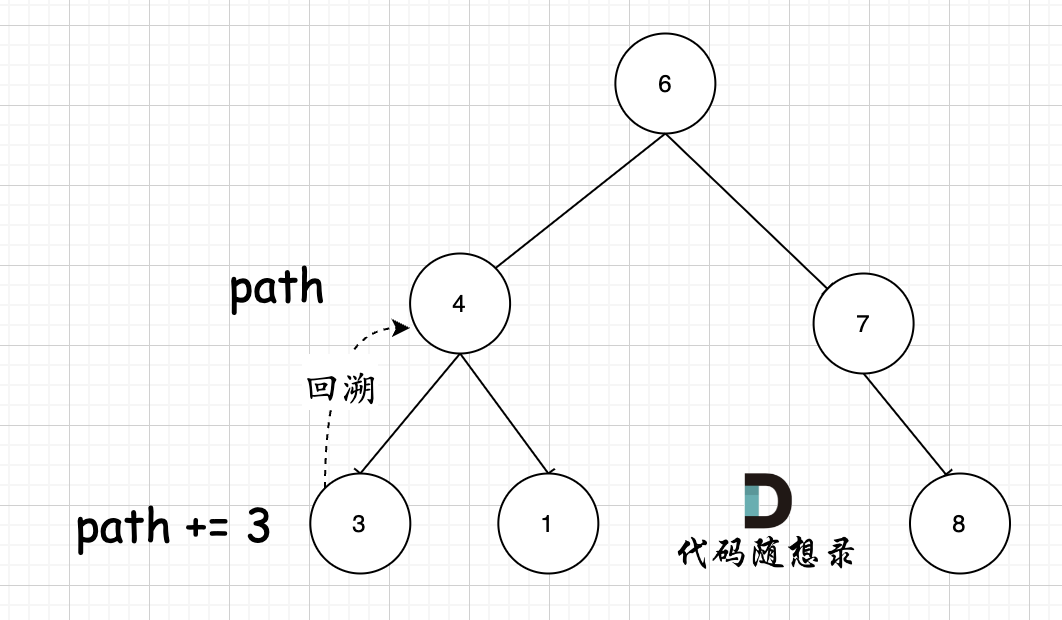

RTL,Register Transfer Level,直译为寄存器转换级,顾名思义,也就是在这个级别下,要描述各级寄存器(时序逻辑中的寄存器),以及寄存器之间的信号的是如何转换的(时序逻辑中的组合逻辑)。

通俗来讲,RTL代码不是在“写代码”,是在画电路结构。RTL代码需要“画”出输入输出端口,各级寄存器,寄存器之间的组合逻辑和前三者之间的连接。对于组合逻辑,只需要软件级描述,将其功能包装在“黑匣子”中即可,无需考虑其门级结构。这也是在进行数字IC过程中最常用的方式。

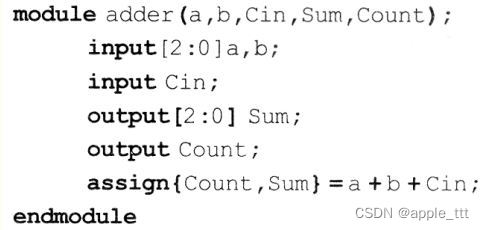

3.4 行为级描述

行为级是RTL的上一层,行为级是最符合人类逻辑思维方式的描述角度,一般基于算法,用C/C++来描述。从行为级到RTL级的转换,一般都是由IC设计人员手工翻译。行为级的描述更多的是采取直接赋值的形式,只能看出结果,看不出数据流的实际处理过程。其中又大量采用算术运算,延迟等一些无法综合的语句。常常只用于验证仿真。但是在FPGA的开发过程中,使用可综合的行为级描述还是很常见的。

四、不可综合的Verilog语法示例

- 不支持内嵌的时间控制,如#<delay>、wait等,因为综合工具会以延时最小为目标,而不予理会你设定的延时

- 不支持initial语句(0时刻起执行),多用复位机制来实现电路信号的初始化

- 不支持repeat、forever等循环次数不确定(无法综合成硬件)的循环语句;while、for循环语句不要用条件表达式的真假来中止循环,而是用@(posedge clk)或@(negedge clk)来中止循环

- 不使用锁存器(latch),特别注意排除组合逻辑中隐含的锁存器,这是RTL结构及DFT测试所要求的

- 不使用与不确定数x和高阻态z有关的操作运算符和语句,如===(全等)、!==(不全等)、casex和casez语句,与此相对应的是尽量不使用三态门

- 作为测试向量(Testbenchs)的HDL约束与综合代码的HDL约束不同,会更为宽松,因此往往是不可综合的

- 在Verilog代码中不使用VHDL保留字,在VHDL不使用Verilog的保留字,这是为了便于二者的共享或相互转换

五、Verilog RTL编码规范

- 命名:使用简短但有意义的信号、变量和端口的名称,如用clk表示时钟、用rst表示复位信号、用rst_n表示低电平有效的复位信号,以便代码自身就具有清晰的注释信息,改善可读性。

- 注释:不能忽略注释,一般注释行占总行数的20%~40%(行内//、跨行/**/)

- 端口声明:习惯上按逻辑顺序声明端口 。输入:时钟、复位、使能、其他控制信号、输入数据 输出:时钟、复位、使能、其他控制信号、输出数据

- 变量声明:一位的wire型变量无需声明,对多位总线信号的声明却是必须的。对于所有的信号进行声明是一种好的编程习惯

- 大小写:建议信号名、变量名和端口名小写,参数和用户定义类型大写

- 代码长度:每个HDL代码占用一行,每行代码长度最好不要超过72个字符

- 下划线:Verilog对下划线的使用没有明确规定,建议在文件名、模块名、信号名中使用下划线而非空白符作为符号间隔

- 缩进:适当地利用空白符进行缩进,有助于理解大型设计;使用缩进格式书写条件或循环部分代码,增强代码的可读性;每个缩进占两个空格为宜;避免使用Tab键录入空白符

对于FPGA设计,还需要注意:

- 文件名与module名要一致,一个文件一个module

- 统一的复位方式,异步复位上升沿有效(无论软复位或硬复位)

- 尽量避免用低电平有效的信号,尽量高电平有效

- 状态机一定要采用三段式

- 端口声明输入输出要分开,最好要有区分输入输出的标示

- 条件分支要写全。Case及if else等

- 信号名不要过长,不要超过32个字母

- 所有寄存器都要复位且有初始值

- 不允许使用门控时钟或门控的复位

- 组合逻辑阻塞赋值,时序逻辑非阻塞赋值

- 内部信号避免出现三态

- 避免出现latch

- 多使用parameter,增加修改的便利性

- 连接同一端口的同一组信号尽量有公共的符号表示,如dav\sop\eop等

- 不允许将多个寄存器写到一个always里面;

- 要为每一个寄存器单独写一个always,哪怕两个信号很相关;

- 要有写电路的意识,不能是写软件的风格(代码短);

- 按照横向思维,每个信号都要仔细考虑,考虑全。刚开始时尽量避免同一个寄存器在多个模块里面都赋值(Multi Driver);

- 代码->电路,写的时候一定明白什么样的代码产生什么样的电路;

- 设计流程:设计目标分析->功能模块划分->确定关键电路时序和模块间时序->具体电路设计设计电路尤其是数字电路,最关键的一环是:设计各模块间的接口时序。这个工作必须在具体电路设计之前确定下来。综合的TOP_DOWN流程是对整个芯片加约束;而综合的BOTTOM_UP流程是先把小模块做综合,然后把综合好的模块用一个顶层的模块包进去,再综合一次。电路较大时,用BOTTOM_UP流程。时序是事先设计出来的,而不是事后测出来的,更不是凑出来的!