1:打开软件建立工程

2:使用vivado创建设计模块并生成bit文件

3:导出硬件平台,使用vitis建立工程

4:使用vitis创建应用程序项目

5:硬件设置与调试

1:打开软件建立工程

打开VIVADO2023.1

创建一个新的工程

输入项目名称和地址,下面那个选项为是否使用项目名称新建一个文件夹,我这里已经建了一个hello_world文件夹,所以不勾选

选择RTL工程,勾选不添加文件

搜索15eg,选择xqzu15eg-ffrb1156-2-i。这一步选择芯片型号,一定要选择和自己开发板相匹配的型号(本实验使用的开发平台是 XCZU15EG对应 的芯片型号xqzu15eg-ffrb1156-2-i)

完成创建工程

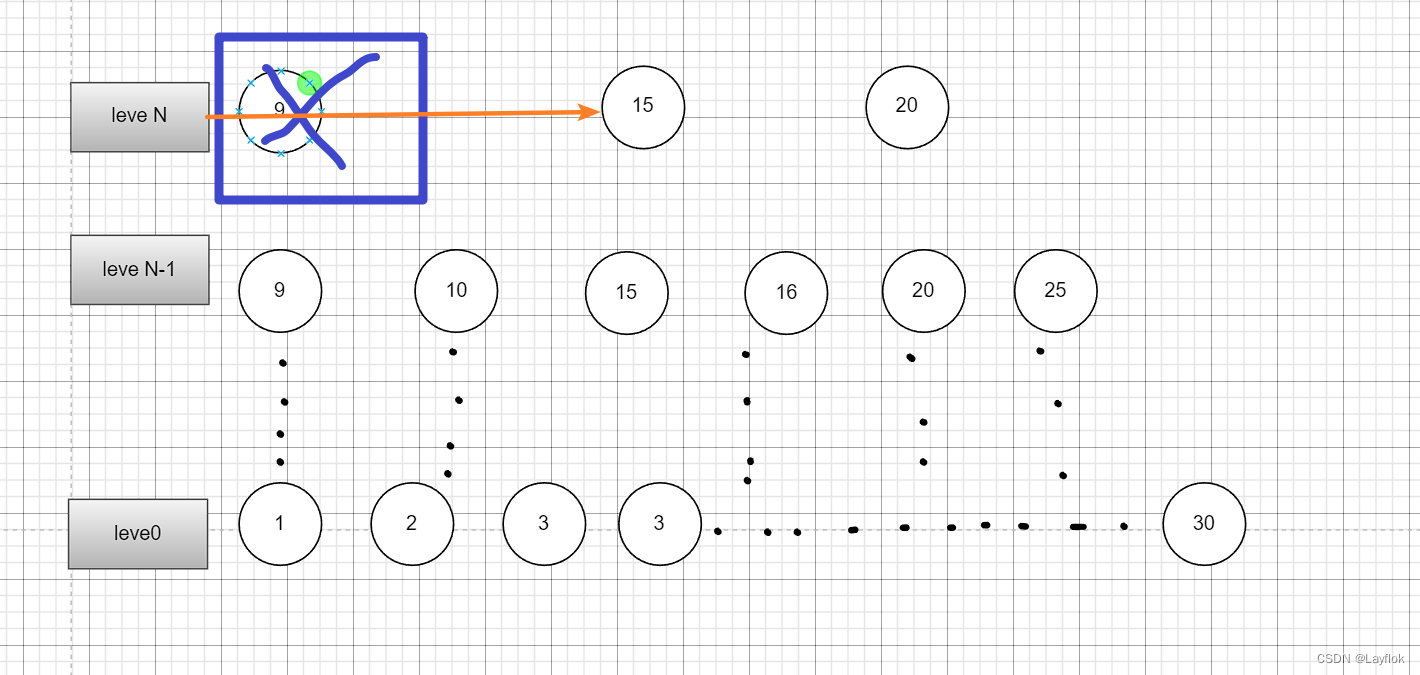

2:使用vivado创建设计模块并生成bit文件

添加设计模块并且设置模块名称

在模块中添加ZYNQ IP

配置 ZYNQ IP 的参数

双击 IP 对 IP 的各个功能参数进行配置,这个配置必须参考硬件原理图完成,所以 FPGA 或者 SOC 工程师必须 具备一定的硬件分析能力,可以阅读原理图,实现对硬件资料在软件上的定义分配。

若有配置文件预设可以直接导入配置,这里我们使用已经提供的配置文件对参数进行位置。

配置文件在 hello_world\file 目录下,选择配置文件点击OK即可导入

导入完成点击OK,把配置导入到ZYNQ内

把ZYNQ模块的时钟线连接起来

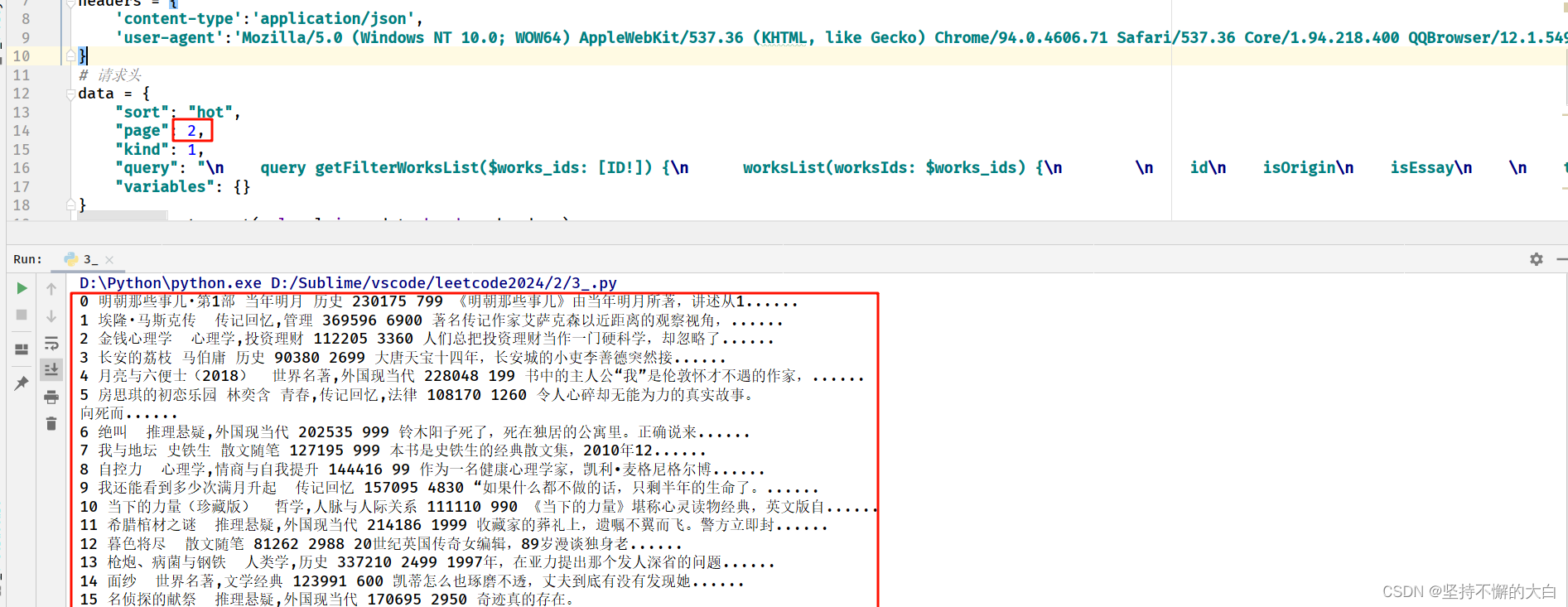

右键设计模块,点击Generate Output ...

默认设置点击生成

右键设计模块生成HDL文件,该文件就是一个 FPGA Verilog 文件。而 BD 图形化工程,VIVADO 把 BD 封装成了一个模块。顶层的 verilog 文件通过模块接口就可以调用 BD 图形代码了,和 ZYNQ 的调用相比,ZYNQ MPSOC 没有了 DDR 等内部信号接口,简洁了很多。

第一个选项是生成可编辑的HDL文件,第二个选项则不可编辑,这里默认即可

点击Generate Bitstream 生成bit流文件

默认设置点击OK

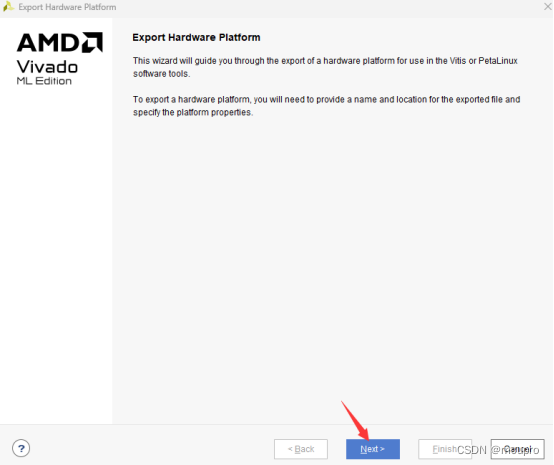

3:导出硬件平台,使用vitis建立工程

首先需要在vivado中导出硬件平台

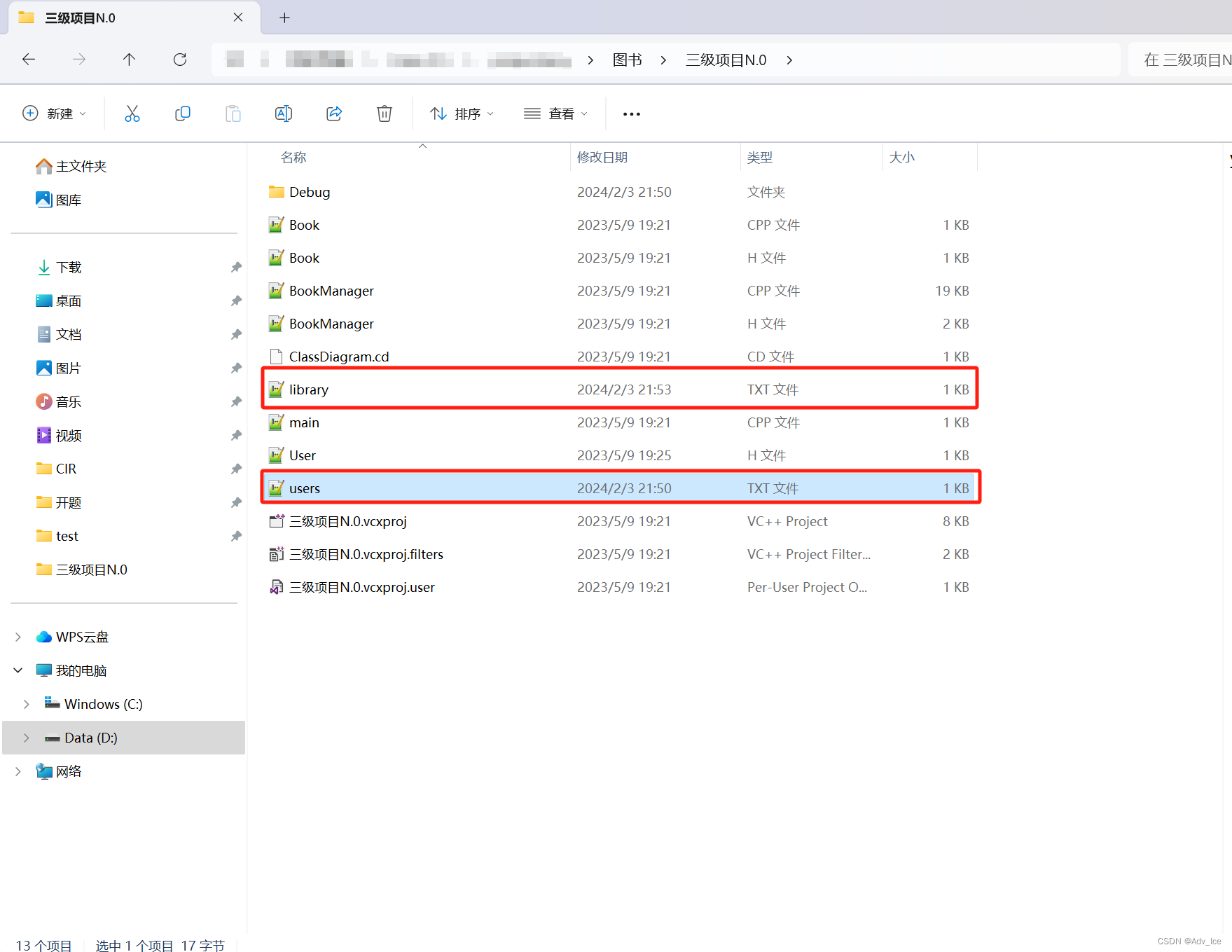

设置名称与选择保存地址,建议地址选择新建一个vitis文件夹,完成导出硬件平台

打开vitis

可用通过vivado打开vitis,tools->Launch vitis IDE

也可以通过vitis应用直接打开

无论那种方式打开后都会提示选择工作空间,我们选择上面创建的vitis文件夹为工作空间

打开vitis后创建平台项目

设置项目名称

导入在vivado中创建的硬件平台

4:使用vitis创建应用程序项目

设置项目名称

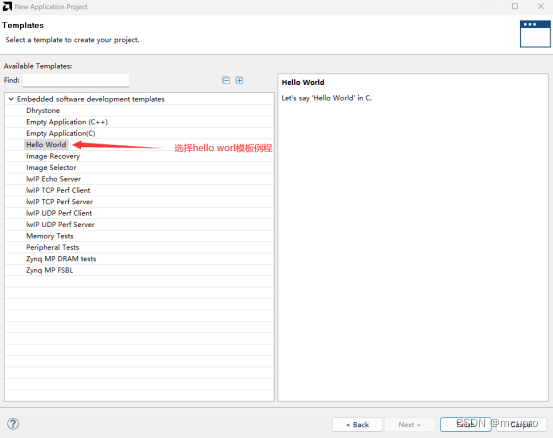

选择hello_world模板例程

右键创建的项目,选择编译

5:硬件设置与调试

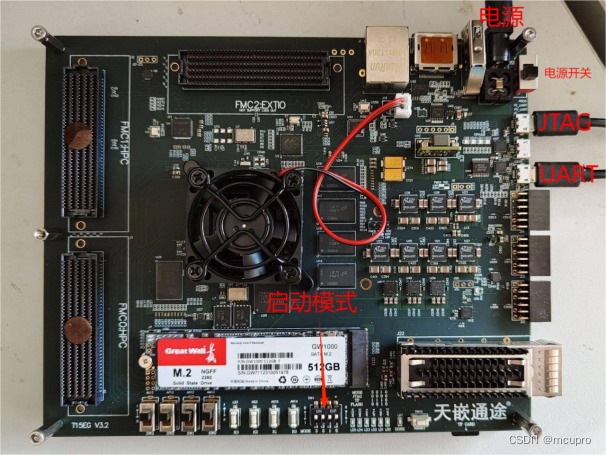

插好板子上的电源,JTAG和UART线,把启动模式设置为JTAG模式0000,开启电源开关

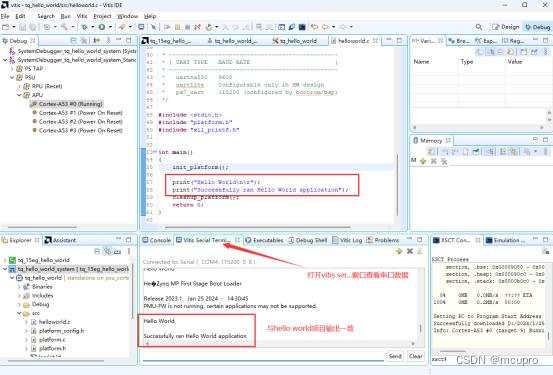

在vitis中点击Debug,进入调试界面

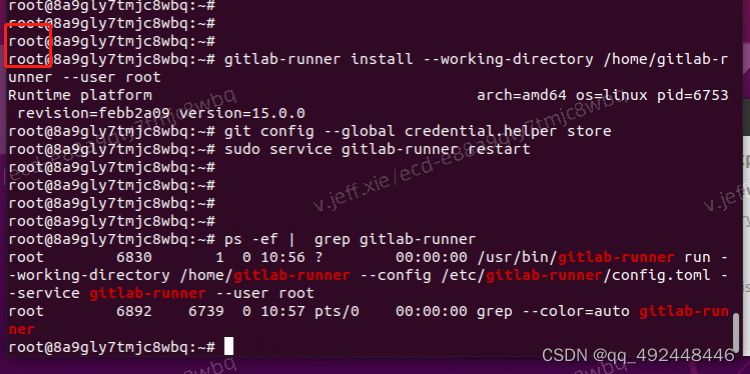

进入Vitis Ser...窗口,点击加号打开串口设置界面,选择COM口后点击OK

点击vitis下的Program Device,把bit流文件烧录进去

点击borwse...选择bit文件,文件在工程目录下的 ***.runs 文件夹,下的impl_1文件夹中,点击program进行烧录

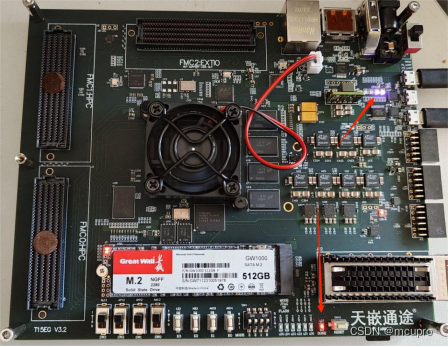

烧录成功,板子上的DL7,DL11和DL12都会亮起来

右键项目点击1 Launch Hardware把程序烧录进去

烧录成功后打开vitis ser...窗口,查看串口输出数据,与例程代码相同