SPI总线很有意思,

如我的NPI项目之Android 安全系列 -- 外挂SE集成(SPI)接口-CSDN博客

提到SPI的接口,基本的电气特性已经给出。这边文章就针对协议部分进行详细解析。从协议网找到了原文:SPI protocol 还有wilipedia SPI

主要涉及一下几个方面,

数据传输:

1. 数据传输之前,主设备首先通过CS(低有效)选择需要进行通信的从设备。

2. 数据传输是一个全双工的过程。在每个SPI时钟周期内,主设备在MOSI线上发送一个位,从设备在MISO线上发送一个位,然后这两个设备分别读取相应的传入位。即使进行的是一个单向的数据传输,也会按照这个顺序模式进行。这是一个典型的全双工的实例。

3.当总线上只有单个从设备进行通信的时候是一个最典型的例子,通常是多位传输,我们以8位数据类型传输为例。这里会涉及到主设备和从设备的移位寄存器。通常数据,首先移出最高有效位MSB。在时钟的边沿,主寄存器和从寄存器都移出其对应的一位。在下一个时钟沿,每个接收器对传输的位进行采样,并将其作为新的最MSB进行存储,所有的位移出和移入后,主寄存器和从寄存器就完成了数据交换。如果需要交换更多数据,那么就可以重复该过程。这样的传输可以持续任意数量的时钟周期。完成后,主设备停止切换时钟信号,并通常取消选择从设备,就是将CS片选型号拉高。

在某些时候,从设备允许的情况下,可以将CS片选信号固定为逻辑低电平。

对于,多个从设备情况下。多点配置的模式时候,需要每个子设备从主设备获取独立的CS片选信号。对于,菊花链的模式时候,仅仅需要一个CS片选信号(使用场景目前没有遇到过,暂时按下不表)。

4.SPI总线上未被选择的设备都应该忽略MOSI和CLK信号。为了防止MISO争用,从属设备需要具有三态逻辑的特性,所以当器件未被选中时,它们的MISO讯号变为高阻抗(逻辑断开)。没有三态输出的器件不能与其他器件共享SPI总线段,但是可以使用外接的三态逻辑缓存来解决这个问题。

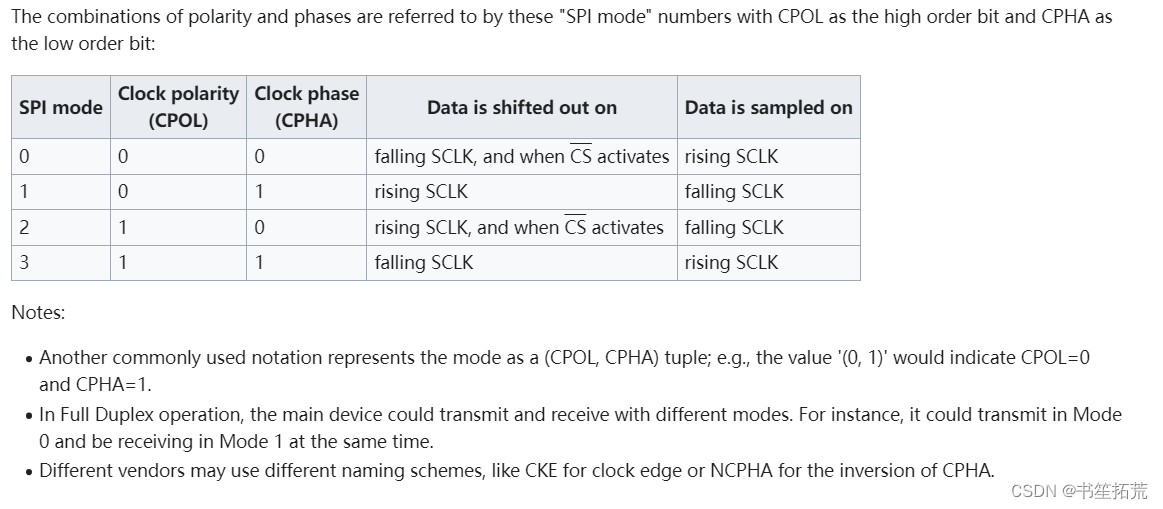

时钟极性和相位:

作为主设备,除了设定时钟,还需要设定有关数据的时钟极性和时钟相位。简称CPOL和CPHA,这个是由摩托罗拉定义。借用wikipedia的一段描述:

工作模式组合:

拓扑类型:

一对一,一对多。

优点:

- SPI协议默认是全双工通信。

- 与漏极开路输出相反,SPI的推挽输出可以提供良好的信号完整性和高速度。

- 比IIC有更高的出输带宽。不限于任何最大时钟频率,可以实现高速运行。

- 简单的线路连接,没有仲裁或者相关的失败模式。

缺点:

- 三线/四线的SPI也比IIC多IC线路。

- 没有带内寻址,共享总线上需要带片选信号。

- 不支持动态添加节点,不支持热插拔。没有从设备检测机制,主机无法检测是否已经与从设备断开。

- 必须通过带外信号来实现中断,或者通过类似USB1.1或者USB2.0的定期轮询来模拟中断。这点和IIC也是一样的。

传输速率:

SPI总线的传输速率取决于多种因素,包括SCK的频率、数据位数以及特定的硬件设计。一般来说,SPI总线的传输速率可以达到几Mbps到几百Mbps。而IIC的SCK大概是100K~400K之间。

总之,

学习一种总线,理解一种总线,发散到其它总线,最后由点到面的精通一个嵌入式系统。