RISC-V指令集之RV32C

- 1 指令格式

- 2 RV32C的指令

本文属于《 RISC-V指令集基础系列教程》之一,欢迎查看其它文章。

1 指令格式

RV32C(压缩指令)的意义:

RV32C基于32位寄存器的RISC-V架构,同时增加了压缩指令集(C),可以将32位指令压缩为16位或更短的指令,从而减少指令存储和传输的开销,提高指令的缓存效率,同时降低功耗和成本。

RV32C的每条指令长度,均为16位,并且每条指令必须和一条标准的32位RISC-V指令一一对应。

此外,16 位指令仅对汇编器和链接器可见,并由它们决定是否将标准指令替换为相应的短指令。编译器开发者和汇编语言程序员无需关心RV32C

指令及其格式,他们只需知道最终得到的程序比大部分情况下更小。

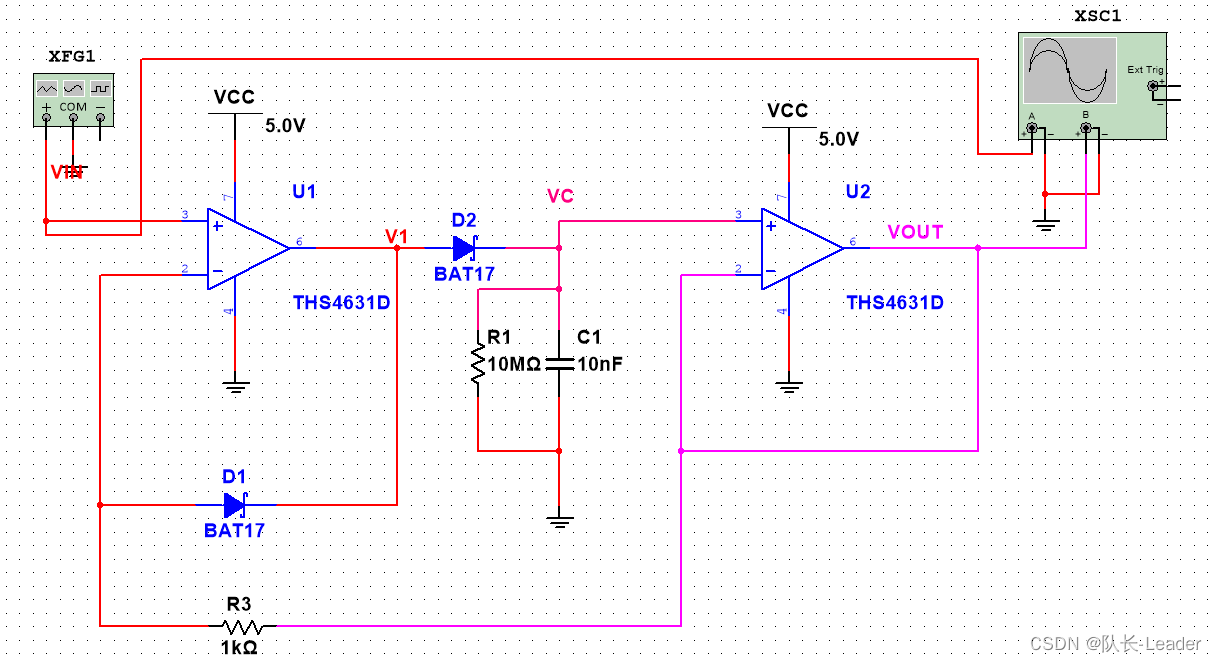

RV32C定义的指令格式,如下所示:

2 RV32C的指令

RV32C具备的所有指令,如下所示:

尽管处理器设计者不能忽略RV32C 指令,但能通过以下技巧降低实现开销:在执行指令前通过一个译码器将所有16 位指令翻译成相应的32 位指令。

本文中的这些指令较多,具体指令详细含义,见RISC-V指令手册,不再赘述。