相关阅读

静态时序分析![]() https://blog.csdn.net/weixin_45791458/category_12567571.html?spm=1001.2014.3001.5482

https://blog.csdn.net/weixin_45791458/category_12567571.html?spm=1001.2014.3001.5482

目录

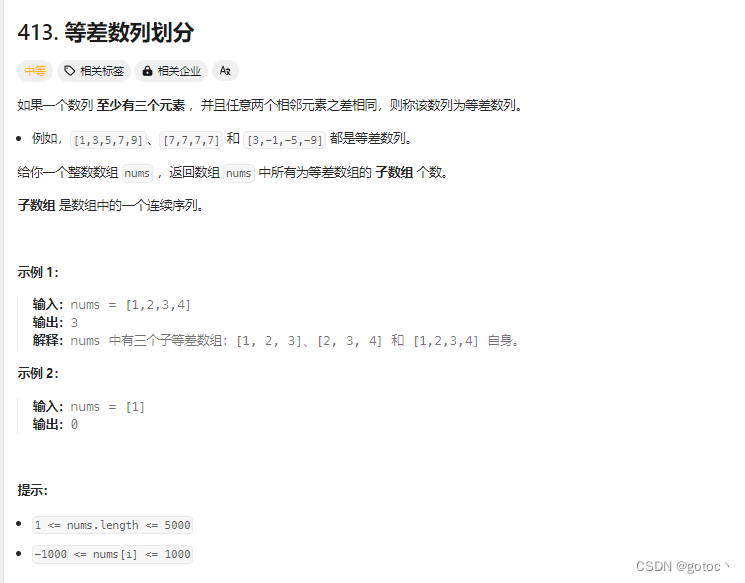

指定建立/保持时间检查

指定上升/下降沿

指定时序路径起点

删除虚假路径

添加注释

简单使用

写在最后

在之前的文章中,我们讨论了如何使用set_case_analysis命令和set_disable_timing命令,它们都能使时序弧失效,本章我们将学习一个虽然不使时序弧失效,但会影响时序路径的时序检查的命令——set_fasle_path,就像前文中直接指定触发器data_out_reg的时钟引脚CK到数据引脚D的时序弧失效一样。

set_fasle_path命令用于指定一条时序路径为虚假路径,虚假路径是不需要满足任何时序要求的路径,工具会忽略这种路径上的时序检查。

set_fasle_path指令的BNF范式(有关BNF范式,可以参考以往文章)为:

set_false_path[-setup | -hold][-rise | -fall][-from from_list | -rise_from rise_from_list | -fall_from fall_from_list][-through through_list] [-rise_through rise_through_list] [-fall_through fall_through_list][-to to_list | -rise_to rise_to_list | -fall_to fall_to_list][-reset_path] [-comment comment_string]

指定建立/保持时间检查

-setup选项指定只设置时序路径为建立时间检查时的虚假路径(只检查保持时间),-hold选项指定只设置时序路径为保持时间检查时的虚假路径(只检查建立时间)。如果这两个选项都没有指定,时序路径为建立时间和保持时间的虚假路径,此时这两种时序都不检查(相当于它们同时指定)。

指定上升/下降沿

-rise选项指定只设置终点是上升沿的时序路径为虚假路径,-fall选项指定只设置终点是下降沿的时序路径为虚假路径。如果这两个选项都没有指定,时序路径为终点是上升沿和下降沿的虚假路径(相当于它们同时指定)。

指定时序路径起点

-from选项、-rise_from选项、-fall_from选项指定了需要设置为虚假路径的时序路径的起点列表,每条命令中它们三者只能指定一个(因为这些指定路径的选项表示都要满足,而不是满足其一即可,所以不能即是上升沿也是下降沿)。

-from选项指定了时序路径的起点,它的参数是一个对象列表,如果有多于一个对象,需要使用引号或大括号包围。对象可以是时钟,代表着时序路径的起点是以该时钟触发的触发器时钟引脚;对象可以是端口,代表着时序路径的起点是该端口;对象可以是引脚,代表着时序路径的起点是该引脚(例如触发器时钟引脚);对象可以是单元,代表着时序路径的起点在该单元上(例如该单元时钟引脚)。

-rise_from选项指定了时序路径的上升沿起点,它的参数是一个对象列表,如果有多于一个对象,需要使用引号或大括号包围。对象可以是时钟,代表着时序路径的起点是所有以该时钟上升沿触发的触发器时钟引脚(这里要考虑时钟在时钟路径上传播时可能因为单元的单调性出现翻转,即以到达触发器时钟引脚的时钟信号上升沿为准);对象可以是端口,代表着时序路径的起点是该端口的上升沿;对象可以是引脚,代表着时序路径的起点是该引脚(例如触发器时钟引脚)的上升沿;对象可以是单元,代表着时序路径的起点在该单元上(例如该单元时钟引脚)的上升沿。

-fall_from选项指定了时序路径的下降沿起点,它的参数是一个对象列表,如果有多于一个对象,需要使用引号或大括号包围。对象可以是时钟,代表着时序路径的起点是所有以该时钟下降沿触发的触发器时钟引脚(这里要考虑时钟在时钟路径上传播时可能因为单元的单调性出现翻转,即以到达触发器时钟引脚的时钟信号下降沿为准);对象可以是端口,代表着时序路径的起点是该端口的下降沿;对象可以是引脚,代表着时序路径的起点是该引脚(例如触发器时钟引脚)的下降沿;对象可以是单元,代表着时序路径的起点在该单元上(例如该单元时钟引脚)的下降沿。

-through选项、-rise_through选项、-fall_through选项需要设置为虚假路径的时序路径的途经点列表,它们可以指定多个,表示依次途径每个列表中的一个对象的时序路径,它们可以以混合使用。

-through选项指定了时序路径的途径点,它的参数是一个对象列表,如果有多于一个对象,需要使用引号或大括号包围。对象可以是端口,代表着时序路径途径该端口;对象可以是引脚,代表着时序路径途径该引脚;对象可以是单元,代表着时序路径途径该单元。

-rise_through选项指定了时序路径的上升沿途径点,它的参数是一个对象列表,如果有多于一个对象,需要使用引号或大括号包围。对象可以是端口,代表着时序路径的上升沿途径该端口;对象可以是引脚,代表着时序路径的上升沿途径该引脚;对象可以是单元,代表着时序路径的上升沿途径该单元。

-fall_through选项指定了时序路径的下降沿途径点,它的参数是一个对象列表,如果有多于一个对象,需要使用引号或大括号包围。对象可以是端口,代表着时序路径的下降沿途径该端口;对象可以是引脚,代表着时序路径的下降沿途径该引脚;对象可以是单元,代表着时序路径的下降沿途径该单元。

-to选项、-rise_to选项、-fall_to选项指定了需要设置为虚假路径的时序路径的起点列表,每条命令中它们三者只能指定一个,并且不能与-fall选项和-rise选项的指定冲突(如已经指定了-fall选项,则只能指定-fall_to选项,因为没有时序路径的终点即是上升沿也是下降沿)。

-to选项指定了时序路径的终点,它的参数是一个对象列表,如果有多于一个对象,需要使用引号或大括号包围。对象可以是时钟,代表着时序路径的终点是以该时钟触发的触发器数据输入引脚;对象可以是端口,代表着时序路径的终点是该端口;对象可以是引脚,代表着时序路径的终点是该引脚(例如触发器数据输入引脚);对象可以是单元,代表着时序路径的起点在该单元上(例如该单元数据输入引脚)。

-rise_to选项指定了时序路径的上升沿终点,它的参数是一个对象列表,如果有多于一个对象,需要使用引号或大括号包围。对象可以是时钟,代表着时序路径的终点是以该时钟上升沿触发的触发器数据输入引脚(这里要考虑时钟在时钟路径上传播时可能因为单元的单调性出现翻转,即以到达触发器时钟引脚的时钟信号上升沿为准);对象可以是端口,代表着时序路径的终点是该端口的上升沿;对象可以是引脚,代表着时序路径的终点是该引脚(例如触发器数据输入引脚)的上升沿;对象可以是单元,代表着时序路径的起点在该单元上(例如该单元数据输入引脚)的上升沿。

-fall_to选项指定了时序路径的下降沿终点,它的参数是一个对象列表,如果有多于一个对象,需要使用引号或大括号包围。对象可以是时钟,代表着时序路径的终点是以该时钟下降沿触发的触发器数据输入引脚(这里要考虑时钟在时钟路径上传播时可能因为单元的单调性出现翻转,即以到达触发器时钟引脚的时钟信号下降沿为准);对象可以是端口,代表着时序路径的终点是该端口的下降沿;对象可以是引脚,代表着时序路径的终点是该引脚(例如触发器数据输入引脚)的下降沿;对象可以是单元,代表着时序路径的起点在该单元上(例如该单元数据输入引脚)的下降沿。

删除虚假路径

-reset_path选项移除了之前设置的虚假路径,使用该选项时,其它选项要和设置虚假路径时一样。

添加注释

-comment选项允许添加一条字符串注释,工具会将注释保存在SDC对象中,以便在使用write_sdc或write_script命令写出约束时输出准确的字符串。注释在综合、布局布线以及时序分析的流中中保持完整。

简单使用

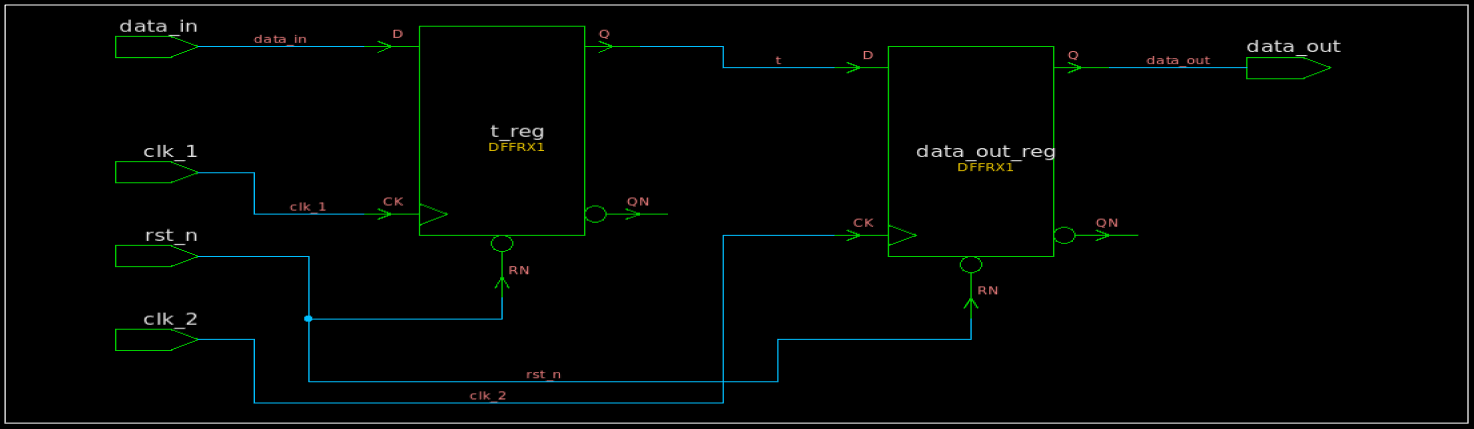

下面将通过具体实例加深印象,首先来看图1所示的简单电路,其中两个触发器分别受到两个时钟端口控制。

图1 一个简单的例子

首先使用下面的命令在输入端口clk_1和clk_2定义两个时钟。

create_clock -period 10 [get_port clk_1]

create_clock -period 15 [get_port clk_2]随后使用下面的命令在输入端口data_in定义输入延迟。

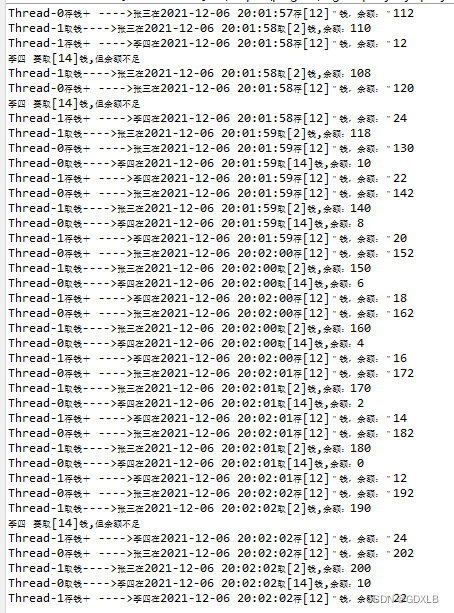

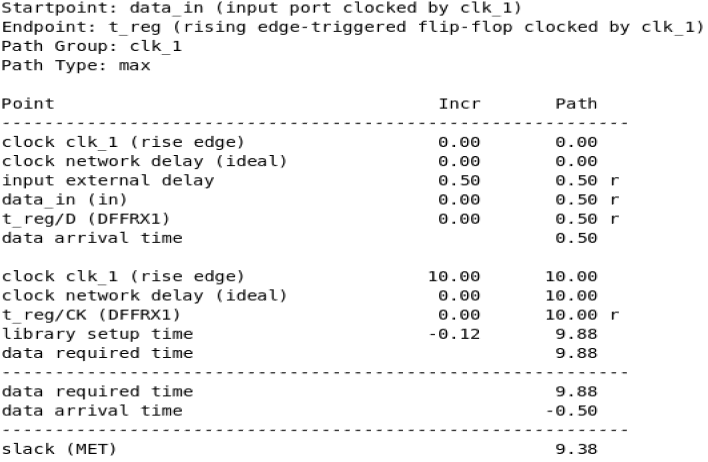

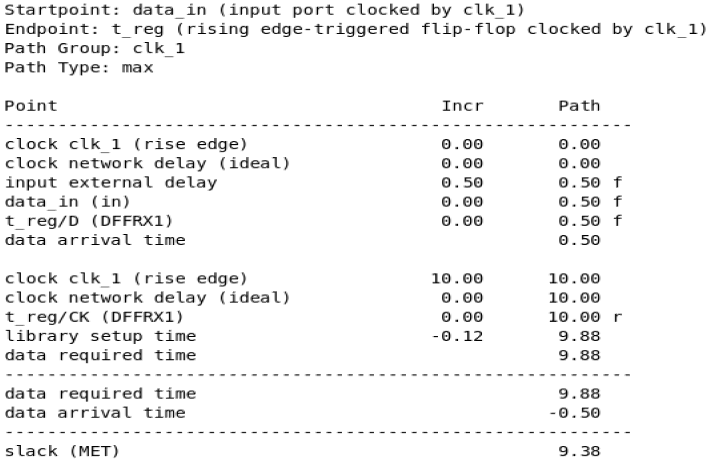

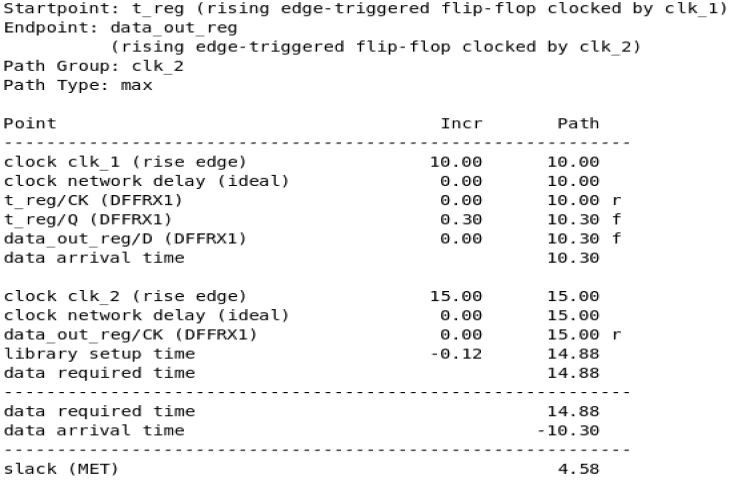

set_input_delay 0.5 -clock clk_1 [get_port data_in]此时使用report_timing命令,t_reg和data_out_reg以及端口data_in和t_reg之间的时序路径会正常报告,如图2、图3、图4、图5所示(本文如不加说明,默认时序报告为建立时间报告)。

图2 时序报告(输入端口上升沿)

图3 时序报告(输入端口下降沿)

图4 时序报告(触发器引脚输出上升沿)

图5 时序报告(触发器引脚输出下降沿)

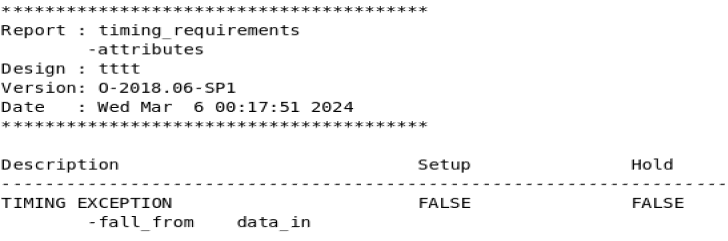

接着使用下面的命令将起点是输入端口data_in下降沿的所有数据路径设置为虚假路径,可以使用report_timing_requirements报告设置的虚假路径,如图6所示。

set_false_path -fall_from [get_port data_in]

图6 时序例外报告

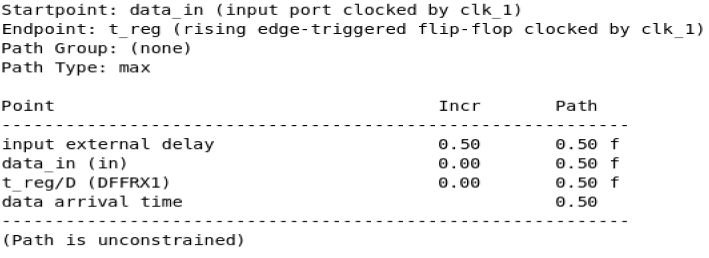

此时的输入端口下降沿的时序报告如图7所示,可以看出时序路径未约束,可以将其与图3对比。

图7 时序报告(输入端口下降沿)

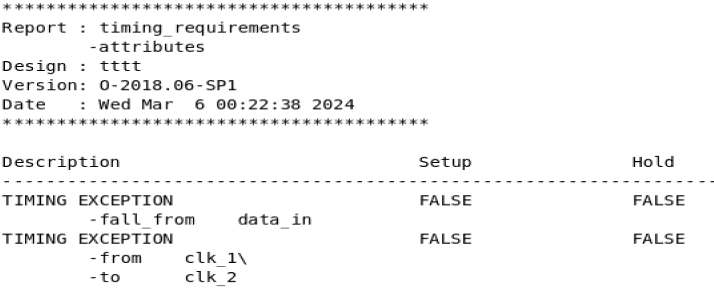

最后,我们使用下面的命令设置时序路径的起点是clk_1时钟,终点是clk_2时钟,如图8所示(注意,这里如果使用-fall_from、-fall_to选项是没有意义的,因为本例的触发器都是上升沿触发)。

set_false_path -from [get_clock clk_1] -to [get_clock clk_2]

图8 时序例外报告

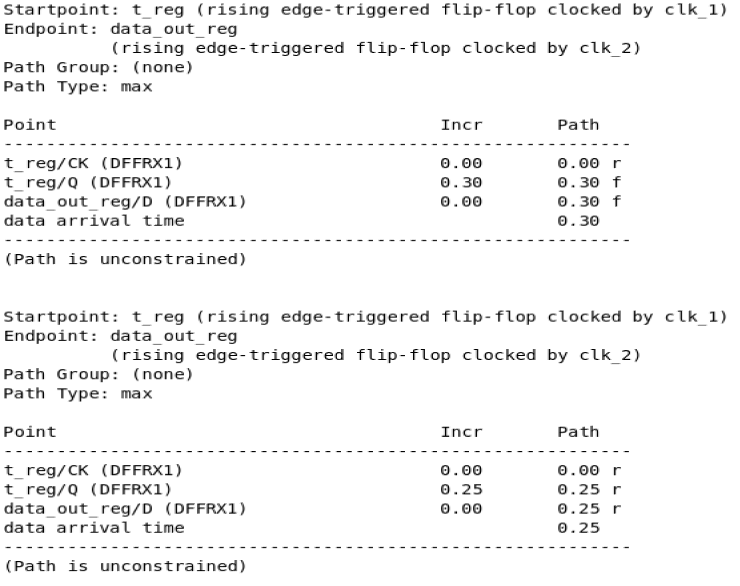

此时两个触发器之间的所有时序路径都被设置为虚假路径,工具不会检查其建立时间和保持时间,如图9所示。

图9 时序报告(触发器引脚输出上升/下降沿)

写在最后

set_false_path是一个点对点时序例外命令,其他的点对点时序例外命令包括set_max_delay命令、set_min_delay命令和set_multicycle_path命令。它们之间可能产生冲突,具体的解析规则可以查阅DC的手册。