本篇文章包含的内容

- 一、DDR SDRAM

- 1.1 基本概述

- 1.2 工作时序(以读取为例)

- 二、DDR2 SDRAM

- 2.1 基本概述

- 2.2 工作时序

- 三、DDR3 SDRAM

- 3.1 基本概述

- 3.2 硬件设计

- 3.3 读写时序

- 3.4 MIG IP核设计

- 3.5 读写代码设计

- 开发板:正点原子的达芬奇开发板(或MicroPhase的Z7-Lite 7020开发板)

- FPGA型号:XC7A35TFGG484-2(或XC7Z020CLG400-2)

- Vivado版本:2020.2

- 参考课程链接:正点原子手把手教你学FPGA-基于达芬奇开发板 A7

一、DDR SDRAM

1.1 基本概述

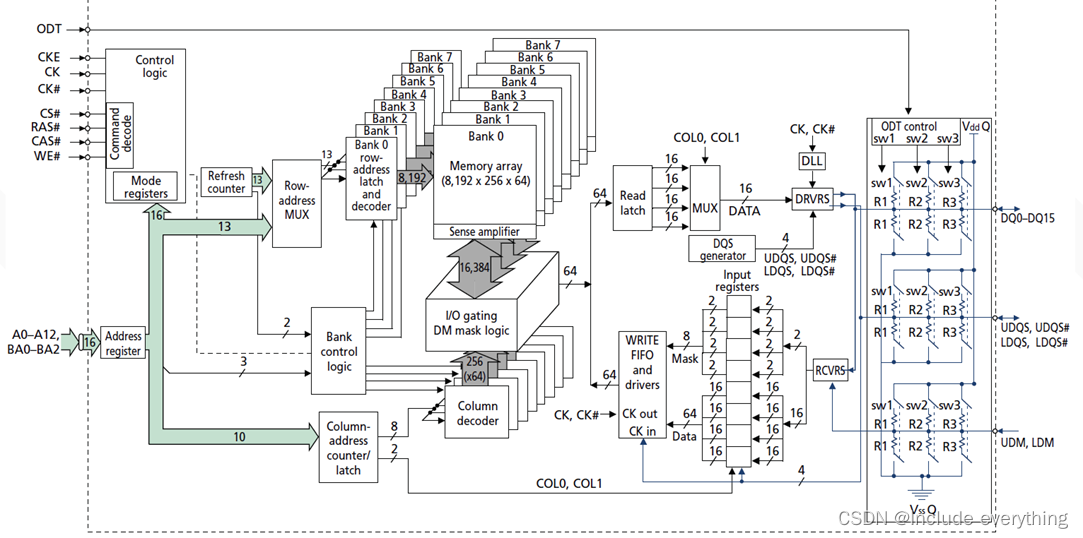

DDR SDRAM(Double Data Rate SDRAM),即(第一代)双倍速率同步动态随机存储器,它的主要结构示意图如上图所示。相较于SDRAM,它的主要有以下几点不同:

- 差分时钟:DDR SDRAM最核心的特点就是通过引入差分时钟,同时获取时钟信号

CK的上升沿和下降沿,在上升沿和下降沿都可以传输数据。 - 数据预取和预存(Prefetch):在读取过程中,为了提高数据传输效率,先将数据放到输出锁存中,之后再通过多路选择器将数据输出到数据线

DQ上。写入操作也与之类似,先将数据读入到缓存电路中,将数据拼接后存入对应的存储单元中。 - 同步数据信号

DQS:数据变化只在DQS的边沿改变,此信号只由数据的发送方给出,提供给数据的接收方用于同步数据信号,目的就是为了在高速的数据传输中保持数据传输的稳定性。 - 掩码控制只对写入起作用:如上图所示,数据的掩码控制只对写入起作用,对读出不再支持掩码控制操作。

1.2 工作时序(以读取为例)

二、DDR2 SDRAM

2.1 基本概述

DDR2的主体结构与第一代DDR没有太大的不同,但是读取速度提升了一倍。可以看到DDR2的内部结构相较于之前也更复杂,在这里仅仅对一些知识点作一些科普性的说明:

- 片外驱动调教(OCD,Off-Chip Driver):DDR2上电后同样有初始化过程,在这个过程中除了需要配置模式寄存器MRS(Mode Register Settings)之外,还添加了扩展模式寄存器设置过程EMRS(Extended Mode Register Settings),增加了新的设置选项。在EMRS阶段,DDR2添加了可选的OCD功能,主要作用是调整IO接口端的电压,用于补偿上拉电阻和下拉电阻对IO端口造成的影响,目的是使DQS和DQ之间的时间偏差降低到最小,以保证数据的稳定传输。调教期间,分别测试DQS高电平-DQ高电平与DQS低电平-DQ高电平时的同步情况,如果不满足要求,则通过设定突发长度的地址线来传送上拉/下拉电阻的等级,直到测试合格才会退出OCD操作。

- 片内终结(ODT,On-Die Termination):所谓的终结,就是让信号被电路的终端被吸收掉,而不会在电路上形成反射,造成对后面信号的影响。在 DDR 时代,控制与数据信号的终结在主板上完成,每块 DDR 主板在 DIMM 槽的旁边都会有一个终结电压岛(电压岛就是指一块特殊的电路,没有其他特殊含义)的设计,它主要由一排终结电阻构成。长期以来,这个电压岛一直是 DDR 主板设计上的一个难点。而 ODT 的出现,则将这个难点消灭了。顾名思义,ODT 就是将终结电阻移植到了芯片内部,主板上不在有终结电路。

- 前置CAS、附加潜伏期AL和写入潜伏期WL:前置 CAS(Posted CAS)是为了解决 DDR 内存中指令冲突而设计的功能。它允许 CAS 信号紧随 RAS (ACTIVE命令)发送,相对于以往的 DDR 等于将 CAS 前置了。这样,地址线可以立刻空出来,便于后面的行有效命令发出,避免造成命令冲突而被迫延后的情况发生,但读/写操作并没有因此而提前,仍有要保证有足够的延迟/潜伏期,为此,DDR-Ⅱ引入了附加潜伏期的概念(AL,Additive Latency),与 CL 一样,单位为时钟周期数。AL+CL 被定义为读取潜伏期(RL,Read Latency),相应的,DDR-Ⅱ还对写入潜伏期(WL,Write Latency)制定了标准,WL 是指从写入命令发出到第一笔数据输入的潜伏期,不要将它和 tDQSS 弄混了,后者是指 DQS 而不是数据。按规定,WL=RL-1,即 AL+CL-1。

2.2 工作时序

三、DDR3 SDRAM

3.1 基本概述

可以看到,DDR3 相较于前几代版本越来越复杂,很多工程师添加和很多的新功能,提升了数据的存储容量和传输效率。但是笔者学习了相关内容之后发现,想要自行编写 DDR3 的 Verilog HDL 程序是非常不现实的,其中涉及非常多时序等待时间的计算和校准,调用官方自带的IP核对于开发效率的提升还是很大的。

DDR3相较于前几代添加的核心概念有以下几点(科普性质内容,了解即可):

-

突发长度(Burst Length,BL)与前几代不同:由于DDR3的预取为8bit,所以突发传输周期(Burst Length,BL)也固定为8,而对于DDR2和早期的DDR架构系统,BL=4也是常用的,DDR3为此增加了一个4bit Burst Chop(突发突变)模式,即由一个BL=4的读取操作加上一个BL=4的写入操作来合成一个BL=8的数据突发传输,届时可通过地址线来控制这一突发模式。而且需要指出的是,任何突发中断操作都将在ddr3中予以禁止,且不予支持,取而代之的是更灵活的突发传输控制(如4bit顺序突发)。

-

寻址时序(Timing)改变:就像DDR2从DDR转变而来后延迟周期数增加一样,DDR3的CL周期也将比DDR2有所提高。DDR2的CL范围一般在2~5之间,而DDR3则在5~11之间,且附加延迟(AL)的设计也有所变化。DDR2时AL的范围是0~4,而DDR3时AL有三种选项,分别是0、CL-1和CL-2。另外,DDR3还新增加了一个时序参数——写入延迟(CWD),这一参数将根据具体的工作频率而定。

-

新增重置(Reset)功能:重置是DDR3新增的一项重要功能,并为此专门准备了一个引脚。DRAM业界很早以前就要求增加这一功能,如今终于在DDR3上实现了。这一引脚将使DDR3的初始化处理变得简单。当Reset命令有效时,DDR3内存将停止所有操作,并切换至最少量活动状态,以节约电力。

在Reset期间,DDR3内存将关闭内在的大部分功能,所有数据接收与发送器都将关闭,所有内部的程序装置将复位,DLL(延迟锁相环路)与时钟电路将停止工作,而且不理睬数据总线上的任何动静。这样一来,将使DDR3达到最节省电力的目的。 -

新增ZQ校准功能:ZQ也是一个新增的引脚,在这个引脚上接有一个240欧姆的低公差参考电阻。这个引脚通过一个命令集,通过片上校准引擎(On-Die Calibration Engine,ODCE)来自动校验数据输出驱动器导通电阻与ODT的终结电阻值。当系统发出这一指令后,将用相应的时钟周期(在加电与初始化之后用512个时钟周期,在退出自刷新操作后用256个时钟周期、在其他情况下用64个时钟周期)对导通电阻和ODT电阻进行重新校准。、

-

两个参考电压:在DDR3系统中,对于内存系统工作非常重要的参考电压信号VREF将分为两个信号,即为命令与地址信号服务的VREFCA和为数据总线服务的VREFDQ,这将有效地提高系统数据总线的信噪等级。

-

点对点连接(Point-to-Point,P2P):这是为了提高系统性能而进行的重要改动,也是DDR3与DDR2的一个关键区别。在DDR3系统中,一个内存控制器只与一个内存通道打交道,而且这个内存通道只能有一个插槽,因此,内存控制器与DDR3内存模组之间是点对点(P2P)的关系(单物理Bank的模组),或者是点对双点(Point-to-two-Point,P22P)的关系(双物理Bank的模组),从而大大地减轻了地址/命令/控制与数据总线的负载。而在内存模组方面,与DDR2的类别相类似,也有标准DIMM(台式PC)、SO-DIMM/Micro-DIMM(笔记本电脑)、FB-DIMM2(服务器)之分,其中第二代FB-DIMM将采用规格更高的AMB2(高级内存缓冲器)。

面向64位构架的DDR3显然在频率和速度上拥有更多的优势,此外,由于DDR3所采用的根据温度自动自刷新、局部自刷新等其它一些功能,在功耗方面DDR3也要出色得多,因此,它可能首先受到移动设备的欢迎,就像最先迎接DDR2内存的不是台式机而是服务器一样。在CPU外频提升最迅速的PC台式机领域,DDR3未来也是一片光明。Intel所推出的新芯片-熊湖(Bear Lake),其将支持DDR3规格,而AMD也预计同时在K9平台上支持DDR2及DDR3两种规格。

3.2 硬件设计

达芬奇板载的DDR3 SDRAM电路图如下,可以当作DDR3硬件设计的一个参考示例:

3.3 读写时序

3.4 MIG IP核设计

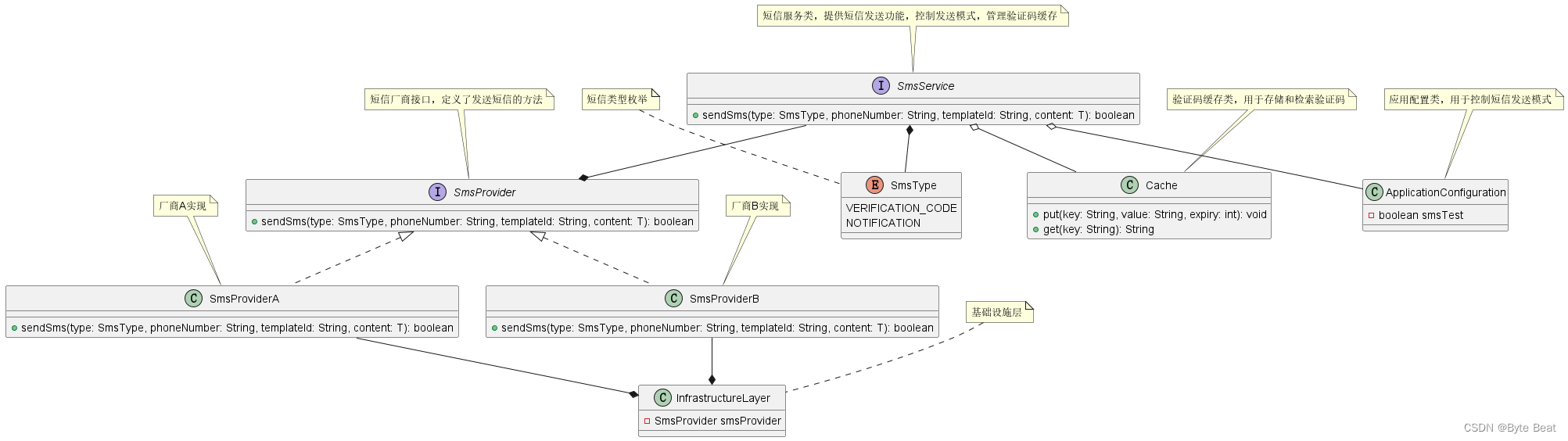

MIG(Memory Interface Generate)是Xilinx Vivado自带的一个IP核,它的结构以及连接关系如下图所示。可以看到,MIG IP核相当于一个连接FPGA用户逻辑和DDR3存储器的桥梁。用户仅需要关心左侧的用户接口的定义和时序即可。

-

在IP Catalog中搜索

mig,即可找到MIG IP核。

-

开始配置MIG,首先配置下列信息

-

选择是否兼容其他型号的FPGA(本次实验不需要)

-

选择DDR3控制器

-

配置时钟选项。包括器件时钟、器件时钟与用户时钟的比率(本次实验器件时钟为400MHz,用户时钟为100MHz)。Vccaux_io是一个与MIG性能有关的电压,本次实验同样保持默认。

-

配置存储器选项、ECC和数据屏蔽。

Memory Type选择Components;存储芯片只能选择美光(MT)的器件,具体的存储芯片型号要和实际的存储大小一致(达芬奇开发板保证设置为128M16即可)。ECC选项只有当数据位宽达到72位才可以开启。数据屏蔽功能本实验没有用到,这里开启或关闭对本次实验没有影响。

-

Bank Machine的数量决定了MIG的性能,但相对的,使用过多也会增大芯片内部的逻辑资源消耗,一般选择一个适中的数值。ORDERING规定是否允许MIG对指令进行重排序,在这里选择开启。

-

配置输入时钟频率(在这里为200MHz,有可能会出现Bug,选择为200MHz后打开依然是400MHz)、突发类型选择(这里选择顺序突发)、输出阻抗控制(默认选择RZQ/7)、终结电阻控制(默认选择RZQ/4)、片选信号输出使能(是否将

#CS信号引出,选择Enable)、寻址模式(颠倒Bank和行的寻址次序可以提高效率,连续地址可以并行处理)

-

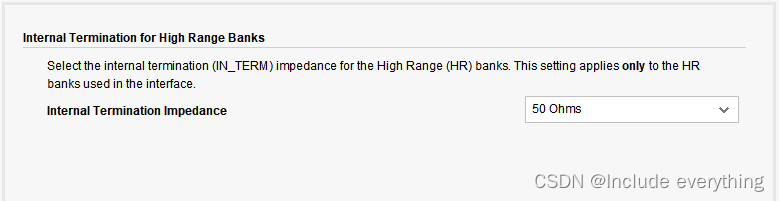

配置FPGA内部相关信息。

-

阻抗匹配设置,这里保持默认。

-

引脚模式设置

-

设置引脚。可以事先写好

.xdc文件,再导入直接读取引脚电平设置,点击Validate使引脚设置生效即可。

-

之后的选项均为总结页面,协议声明等,全部保持默认即可。

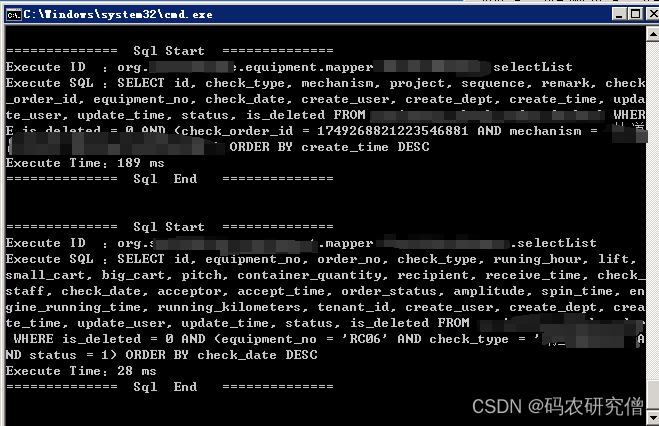

3.5 读写代码设计

ddr3_rw_top.v

module ddr3_rw_top(input sys_clk, // 系统时钟input sys_rst_n, // 复位,低有效// DDR3inout [31:0] ddr3_dq , // DDR3 数据inout [3:0] ddr3_dqs_n , // DDR3 dqs负inout [3:0] ddr3_dqs_p , // DDR3 dqs正output [13:0] ddr3_addr , // DDR3 地址output [2:0] ddr3_ba , // DDR3 banck 选择output ddr3_ras_n , // DDR3 行选择output ddr3_cas_n , // DDR3 列选择output ddr3_we_n , // DDR3 读写选择output ddr3_reset_n , // DDR3 复位output [0:0] ddr3_ck_p , // DDR3 时钟正output [0:0] ddr3_ck_n , // DDR3 时钟负output [0:0] ddr3_cke , // DDR3 时钟使能output [0:0] ddr3_cs_n , // DDR3 片选output [3:0] ddr3_dm , // DDR3_dmoutput [0:0] ddr3_odt , // DDR3_odt//用户output led // 错误指示信号);// wire definewire error_flag;wire ui_clk ; // 用户时钟wire [27:0] app_addr; // DDR3 地址wire [2:0] app_cmd; // 用户读写命令wire app_en; // MIG IP核使能wire app_rdy; // MIG IP核空闲wire [255:0] app_rd_data; // 用户读数据wire app_rd_data_end; // 突发读当前时钟最后一个数据wire app_rd_data_valid; // 读数据有效wire [255:0] app_wdf_data; // 用户写数据wire app_wdf_end; // 突发写当前时钟最后一个数据wire [31:0] app_wdf_mask; // 写数据屏蔽wire app_wdf_rdy; // 写空闲wire app_sr_active; // 保留wire app_ref_ack; // 刷新请求wire app_zq_ack; // ZQ 校准请求wire app_wdf_wren; // DDR3 写使能wire locked; // 锁相环频率稳定标志wire clk_ref_i; // DDR3参考时钟wire sys_clk_i; // MIG IP核输入时钟wire clk_200; // 200M时钟wire ui_clk_sync_rst; // 用户复位信号wire init_calib_complete; // 校准完成信号//*****************************************************//** main code//*****************************************************//读写模块ddr3_rw u_ddr3_rw(.ui_clk (ui_clk),.ui_clk_sync_rst (ui_clk_sync_rst),.init_calib_complete (init_calib_complete),.app_rdy (app_rdy),.app_wdf_rdy (app_wdf_rdy),.app_rd_data_valid (app_rd_data_valid),.app_rd_data (app_rd_data),.app_addr (app_addr),.app_en (app_en),.app_wdf_wren (app_wdf_wren),.app_wdf_end (app_wdf_end),.app_cmd (app_cmd),.app_wdf_data (app_wdf_data),.state (state),.rd_addr_cnt (rd_addr_cnt),.wr_addr_cnt (wr_addr_cnt),.rd_cnt (rd_cnt),.error_flag (error_flag),.led (led));// MIG IP核模块mig_7series_0 u_mig_7series_0 (// Memory interface ports.ddr3_addr (ddr3_addr), // output [14:0] ddr3_addr.ddr3_ba (ddr3_ba), // output [2:0] ddr3_ba.ddr3_cas_n (ddr3_cas_n), // output ddr3_cas_n.ddr3_ck_n (ddr3_ck_n), // output [0:0] ddr3_ck_n.ddr3_ck_p (ddr3_ck_p), // output [0:0] ddr3_ck_p.ddr3_cke (ddr3_cke), // output [0:0] ddr3_cke.ddr3_ras_n (ddr3_ras_n), // output ddr3_ras_n.ddr3_reset_n (ddr3_reset_n),// output ddr3_reset_n.ddr3_we_n (ddr3_we_n), // output ddr3_we_n.ddr3_dq (ddr3_dq), // inout [31:0] ddr3_dq.ddr3_dqs_n (ddr3_dqs_n), // inout [3:0] ddr3_dqs_n.ddr3_dqs_p (ddr3_dqs_p), // inout [3:0] ddr3_dqs_p.init_calib_complete (init_calib_complete),// init_calib_complete.ddr3_cs_n (ddr3_cs_n), // output [0:0] ddr3_cs_n.ddr3_dm (ddr3_dm), // output [3:0] ddr3_dm.ddr3_odt (ddr3_odt), // output [0:0] ddr3_odt// Application interface ports.app_addr (app_addr), // input [28:0] app_addr.app_cmd (app_cmd), // input [2:0] app_cmd.app_en (app_en), // input app_en.app_wdf_data (app_wdf_data),// input [255:0] app_wdf_data.app_wdf_end (app_wdf_end), // input app_wdf_end.app_wdf_wren (app_wdf_wren),// input app_wdf_wren.app_rd_data (app_rd_data), // output [255:0]app_rd_data.app_rd_data_end (app_rd_data_end),// output app_rd_data_end.app_rd_data_valid (app_rd_data_valid),// output app_rd_data_valid.app_rdy (app_rdy), // output app_rdy.app_wdf_rdy (app_wdf_rdy), // output app_wdf_rdy.app_sr_req (), // input app_sr_req.app_ref_req (), // input app_ref_req.app_zq_req (), // input app_zq_req.app_sr_active (app_sr_active),// output app_sr_active.app_ref_ack (app_ref_ack), // output app_ref_ack.app_zq_ack (app_zq_ack), // output app_zq_ack.ui_clk (ui_clk), // output ui_clk.ui_clk_sync_rst (ui_clk_sync_rst),// output ui_clk_sync_rst.app_wdf_mask (32'b0), // input [31:0] app_wdf_mask// System Clock Ports.sys_clk_i (clk_200),// Reference Clock Ports.clk_ref_i (clk_200),.sys_rst (sys_rst_n) // input sys_rst);//PLL模块clk_wiz_0 u_clk_wiz_0 (// Clock out ports.clk_out1(clk_200), // output clk_out1.clk_out2(clk_50),// Status and control signals.reset(1'b0), // input resetn.locked(locked), // output locked// Clock in ports.clk_in1(sys_clk)); // input clk_in1endmoduleddr3_rw.v

module ddr3_rw (input ui_clk, //用户时钟input ui_clk_sync_rst, //复位,高有效input init_calib_complete, //DDR3初始化完成input app_rdy, //MIG 命令接收准备好标致input app_wdf_rdy, //MIG数据接收准备好input app_rd_data_valid, //读数据有效input [255:0] app_rd_data, //用户读数据output reg [27:0] app_addr, //DDR3地址output app_en, //MIG IP发送命令使能output app_wdf_wren, //用户写数据使能output app_wdf_end, //突发写当前时钟最后一个数据output [2:0] app_cmd, //MIG IP核操作命令,读或者写output reg [255:0] app_wdf_data, //用户写数据output reg [1 :0] state, //读写状态output reg [23:0] rd_addr_cnt, //用户读地址计数output reg [23:0] wr_addr_cnt, //用户写地址计数output reg [20:0] rd_cnt, //实际读地址标记output reg error_flag, //读写错误标志output reg led //读写测试结果指示灯);//parameter defineparameter TEST_LENGTH = 1000;parameter L_TIME = 25'd25_000_000;parameter IDLE = 2'd0; //空闲状态parameter WRITE = 2'd1; //写状态parameter WAIT = 2'd2; //读到写过度等待parameter READ = 2'd3; //读状态//reg definereg [24:0] led_cnt; //led计数//wire definewire error; //读写错误标记wire rst_n; //复位,低有效//*****************************************************//** main code//*****************************************************assign rst_n = ~ui_clk_sync_rst;//读信号有效,且读出的数不是写入的数时,将错误标志位拉高assign error = (app_rd_data_valid && (rd_cnt!=app_rd_data));//在写状态MIG IP 命令接收和数据接收都准备好,或者在读状态命令接收准备好,此时拉高使能信号,assign app_en = ((state == WRITE && (app_rdy && app_wdf_rdy))||(state == READ && app_rdy)) ? 1'b1:1'b0;//在写状态,命令接收和数据接收都准备好,此时拉高写使能assign app_wdf_wren = (state == WRITE && (app_rdy && app_wdf_rdy)) ? 1'b1:1'b0;//由于DDR3芯片时钟和用户时钟的分频选择4:1,突发长度为8,故两个信号相同assign app_wdf_end = app_wdf_wren;//处于读的时候命令值为1,其他时候命令值为0assign app_cmd = (state == READ) ? 3'd1 :3'd0;//DDR3读写逻辑实现always @(posedge ui_clk or negedge rst_n)beginif((~rst_n)||(error_flag))beginstate <= IDLE;app_wdf_data <= 128'd0;wr_addr_cnt <= 24'd0;rd_addr_cnt <= 24'd0;app_addr <= 28'd0;endelse if(init_calib_complete)begin //MIG IP核初始化完成case(state)IDLE:beginstate <= WRITE;app_wdf_data <= 256'd0;wr_addr_cnt <= 24'd0;rd_addr_cnt <= 24'd0;app_addr <= 28'd0;endWRITE:beginif(wr_addr_cnt == TEST_LENGTH - 1 &&(app_rdy && app_wdf_rdy))state <= WAIT; //写到设定的长度跳到等待状态else if(app_rdy && app_wdf_rdy)begin //写条件满足app_wdf_data <= app_wdf_data + 1; //写数据自加wr_addr_cnt <= wr_addr_cnt + 1; //写地址自加app_addr <= app_addr + 8; //DDR3 地址加8endelsebegin //写条件不满足,保持当前值app_wdf_data <= app_wdf_data;wr_addr_cnt <= wr_addr_cnt;app_addr <= app_addr;endendWAIT:beginstate <= READ; //下一个时钟,跳到读状态rd_addr_cnt <= 24'd0; //读地址复位app_addr <= 28'd0; //DDR3读从地址0开始endREAD:begin //读到设定的地址长度if(rd_addr_cnt == TEST_LENGTH - 1 && app_rdy)state <= IDLE; //则跳到空闲状态else if(app_rdy)begin //若MIG已经准备好,则开始读rd_addr_cnt <= rd_addr_cnt + 1'd1; //用户地址每次加一app_addr <= app_addr + 8; //DDR3地址加8endelsebegin //若MIG没准备好,则保持原值rd_addr_cnt <= rd_addr_cnt;app_addr <= app_addr;endenddefault:beginstate <= IDLE;app_wdf_data <= 256'd0;wr_addr_cnt <= 24'd0;rd_addr_cnt <= 24'd0;app_addr <= 28'd0;endendcaseendend//对DDR3实际读数据个数编号计数always @(posedge ui_clk or negedge rst_n)beginif(~rst_n)rd_cnt <= 0; //若计数到读写长度,且读有效,地址计数器则置0else if(app_rd_data_valid && rd_cnt == TEST_LENGTH - 1)rd_cnt <= 0; //其他条件只要读有效,每个时钟自增1else if (app_rd_data_valid )rd_cnt <= rd_cnt + 1;end//寄存状态标志位always @(posedge ui_clk or negedge rst_n)beginif(~rst_n)error_flag <= 0;else if(error)error_flag <= 1;end//led指示效果控制always @(posedge ui_clk or negedge rst_n)beginif((~rst_n) || (~init_calib_complete ))beginled_cnt <= 25'd0;led <= 1'b0;endelsebeginif(~error_flag) //读写测试正确led <= 1'b1; //led灯常亮elsebegin //读写测试错误led_cnt <= led_cnt + 25'd1;if(led_cnt == L_TIME - 1'b1)beginled_cnt <= 25'd0;led <= ~led; //led灯闪烁endendendendendmodule原创笔记,码字不易,欢迎点赞,收藏~ 如有谬误敬请在评论区不吝告知,感激不尽!博主将持续更新有关嵌入式开发、FPGA方面的学习笔记。

![[Kali] 安装Nessus及使用](https://img-blog.csdnimg.cn/direct/17c6362b4b5f4880b19417cbe0b8f6cc.png)