系列文章目录

FPGA静态时序分析与约束(一)、理解亚稳态

FPGA静态时序分析与约束(三)、读懂vivado时序报告

文章目录

- 系列文章目录

- 前言

- 一、时序分析基本概念

- 1.1 时钟抖动

- 1.2 时钟偏斜

- 1.3 时钟不确定性Uncertainty

- 1.4 建立时间和保持时间

- 1.5 启动沿和锁存沿

- 二、时序分析基本步骤

- 2.1 时序分析基本模型

- 2.2 理想建立时间和保持时间

- 2.3 实际建立时间和余量分析

- 2.3.1 分析建立时间延迟参数

- 2.3.2 分析锁存沿时间延迟参数

- 2.3.3 建立时间余量分析

- 2.3.4 理想建立时间值

- 2.4 实际保持时间和余量分析

- 2.4.1 分析保持时间延迟参数

- 三、总结

- 参考资料

前言

从上篇理解亚稳态的文章可知,如果数字电路中出现了亚稳态现象,则可能导致整个系统失效;而出现亚稳态现象的最主要的原因就是寄存器在传输数据过程中发生了建立时间( t s u t_{su} tsu)或者保持时间( t h t_h th)的违规。因此时序分析至关重要,只有正确的时序才能让整个系统无异常的跑起来。

一、时序分析基本概念

1.1 时钟抖动

理想的时钟信号是非常完美的正弦波,但是实际晶振产生的正弦波是存在一些时钟抖动的。那么什么是时钟抖动呢?时钟抖动,英文名叫做 Clock Jitter,是相对于理想时钟沿实际时钟存在不随时间积累的、时而超前、时而滞后的偏移称为时钟抖动,如下图所示:

1.2 时钟偏斜

时钟偏差:Clock Skew,是指同一个时钟域内的时钟信号到达数字电路各个部分(一般是指寄存器)所用时间的差异。时序分析的起点一般是源寄存器(reg1),终点一般是目标寄存器(reg2)。时钟和其它信号的传输一样会有延时的。下图中,时钟信号从时钟源传输到源寄存器的延时我们定义为 Tc2s,传输到目标寄存器的延时我们定义为 Tc2d。如下图所示:

时钟网络延时 Tskew 就是 Tc2d 与 Tc2s 之差,即 Tskew=Tc2d-Tc2s

1.3 时钟不确定性Uncertainty

Clock Uncertainty就是时钟的不确定性。时钟的不确定性主要是由 Clock Skew 和 Jitter 构成。因此 Clock Uncertainty = Clock Skew + Clock Jitter。一般标准的时序约束文件中,都需要加 Clock Uncertainty 的约束,这个约束是为了让时序分析更贴近真实的电路设计。

1.4 建立时间和保持时间

建立时间:Setup Time,缩写是 T s u T_{su} Tsu,即在时钟上升沿之前数据必须稳定的最短时间。若不满足 setup time,数据无法进入寄存器,也就是说寄存器的数据采样会失败。(简单来说,建立时间就是数据变化必须在目标寄存器采样沿之前的最短时间)。

保持时间:Hold Time,缩写是 T h T_h Th,即在时钟上升沿之后数据必须稳定的最短时间。若不满足 hold time,数据也无法进入寄存器,也就是说寄存器的数据采样也会失败。(简单来说,保持时间就是数据变化必须在目标寄存器采样沿之后的最短时间)

总体来说,寄存器的采样需要同时满足建立时间和保持时间,如果不满足任何一个,那么寄存器可能采样失败从而进入亚稳态。

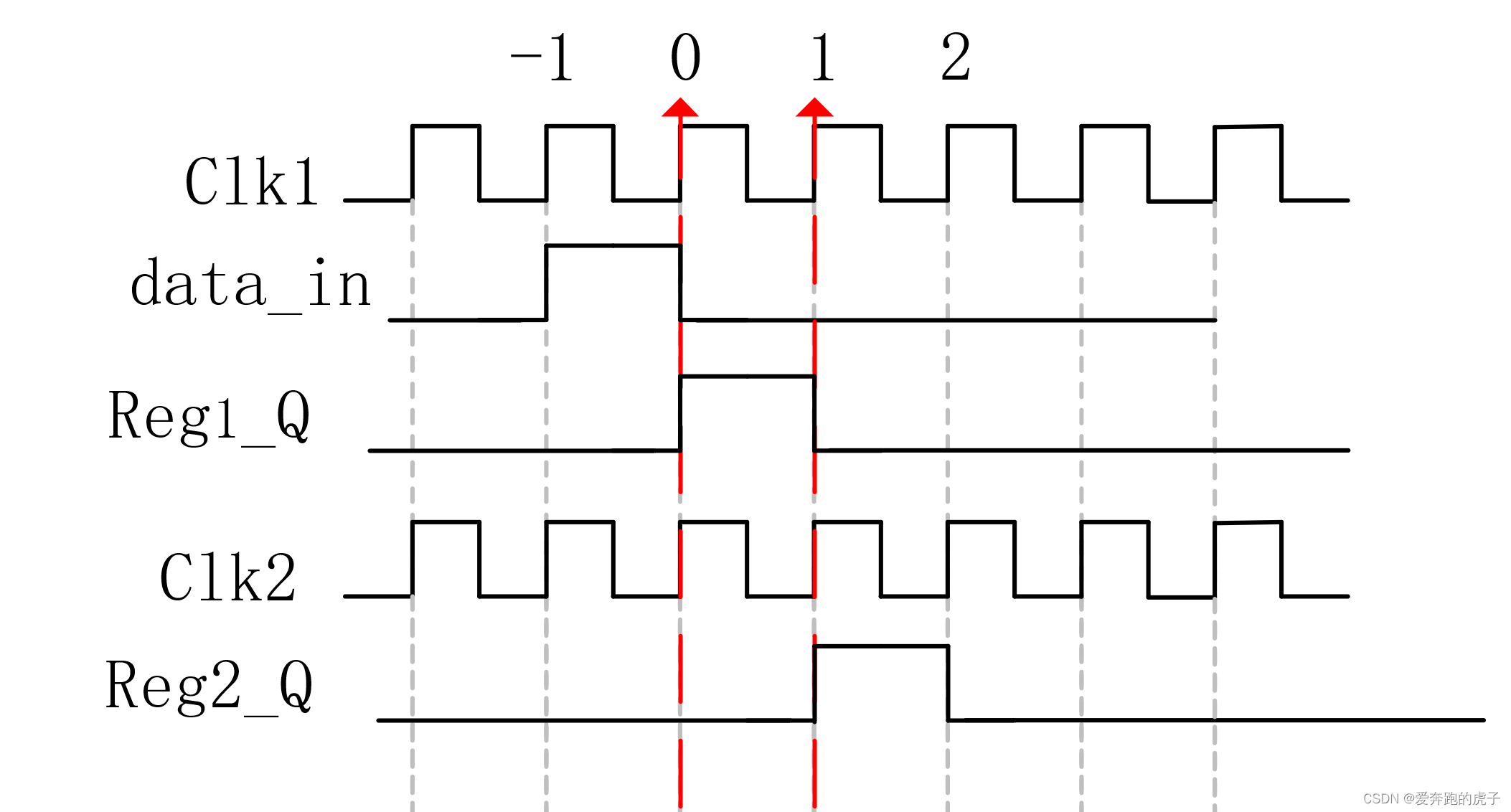

1.5 启动沿和锁存沿

寄存器发送数据和接收数据都是需要在时钟边沿进行的,因此对寄存器来说,都有一个发起沿和一个采样沿。

启动沿:lunch edge,是发送数据的时钟边沿,通常选择上升沿。

锁存沿:latch edge,是采样到该数据的时钟边沿,通常也是上升沿。理想情况这两个边沿会有一个时钟周期的差别。如图所示:

二、时序分析基本步骤

2.1 时序分析基本模型

时序分析是两个节点之间的时序分析,有以下四种情况:

- 管脚输入(PAD)和寄存器之间的路径(即 pin2reg)

- 寄存器和寄存器之间的路径(即 reg2reg)

- 寄存器和管脚输出(PAD)之间的路径(即 reg2pin)

- 管脚输入(PAD)和管脚输出 (PAD)之间的路径(即 pin2pin)

1、pin2reg:

从外部芯片到FPGA 的第一级寄存器的输入端口,这个部分包括 3 个延迟,分别是 Tco(外部芯片时钟到外部芯片寄存器输出延时),Input Delay(PCB 板子的输入走线延迟)和Internal Delay(FPGA 内部的输入走线延迟)。

2、reg2reg:

FPGA内部两个寄存器之间的路径包括 2 个延迟,分别是 Tco(FPGA内部时钟到内部寄存器输出延时)和 Data Path Delay(FPGA 内部的组合逻辑和数据走线延迟)。

3、reg2pin:

最后一级寄存器到外部芯片数据端口的路径部分包括 3 个延迟,分别是 Tco(FPGA内部时钟到内部寄存器输出延时),Internal Delay(FPGA 内部的输入走线延迟)和Output Delay(PCB 板子的输出走线延迟)。

4、pin2pin:

端口到端口的路径这个部分包括 1 个延迟,即 Data PathDelay(FPGA 内部的组合逻辑和数据走线延迟)。

2.2 理想建立时间和保持时间

在 T0 的时候,reg1 向 reg2 发送数据1,该数据长达一个周期时间,这段时间也称为“建立关系时间”,也就是图中T0红色箭头(启动沿)和T1红色箭头(锁存沿)之间的时间。理想情况下,CLK1与CLK2同频率,所以:

理想建立时间关系值=时钟周期

保存时间:reg2 用来锁存 reg1 发送过来数据所需的“最小时间”

在 T0 的时候 CLK1 的启动沿(红色的箭头↑)使得 reg1 向 reg2 发送数据。然后在 T1 的时候CLK2 的锁存沿(绿色箭头↑)使得 reg2 保存 reg1 发送过来的数据。换句话说,reg1 在 T0 向 reg2 发送的数据,而 reg2 乘数据还没有更新之前,reg2 必须迅速的将 reg1 在 T0 发送过来的数据保存起来。

保持关系值 = 0ns

2.3 实际建立时间和余量分析

在实际电路传输过程中,时钟和数据传输有一定的延迟,寄存器锁存数据和寄存器输出数据都有一定延迟,如下图所示:

- Tclk1和Tclk2是时钟走线延时,由时钟源到两个寄存器的延迟时间

- Tdata 是指数据路径延迟,数据由上一节点输出端,经过走线到下一节点输入端的延迟时间

- Tco 是数据从寄存器输入端到寄存器输出端需要的延迟时间

- Tsu是寄存器在锁存沿之前需要的数据"最小准备时间"

- Th 是寄存器在锁存数据过后需要的数据“最小保持时间

其中Tco、Tsu、Th是由FPGA出厂就自带的,不同的工艺、不同的芯片型号,这三个都不同。

2.3.1 分析建立时间延迟参数

如上图所示,红色虚线是整条链路的延迟路径,假设signal in已经准备好数据

源时钟CLK 的上升沿受到 Tclk1 的延迟来到 reg1 之前, 当 reg1_clk 的启动沿(红色箭头)触发 reg1 向 reg2 发送数据时,reg1 还要需要 Tco 的寄存器内部延迟时间。当经过 Tco 的延迟之后,数据从 Reg1-Q端 发送出去,数据到达reg2_D端之前还有 Tdata 的延迟。Tdata 延迟的产生源除了路径本身的延迟以外,最主要还是“组合逻辑”。最后 reg1 向 reg2 发送的数据经过 Tdata 的延迟之后就抵达reg2 的入口(reg2-D)。

如果源时钟输入管脚为0时刻,那么数据到达Reg2的D端所走过的延迟是Tclk1+Tco+Tdata

所以:

数据到达时间 Data Arrival time = Tclk1 + Tco + Tdata

由公式可以看出,建立时间延迟受Tclk1、Tco、Tdata影响

2.3.2 分析锁存沿时间延迟参数

如上图所示,Tclk2 和 Tsu。Tclk2 是锁存沿抵达 reg2 之前时钟路径的延迟。Tsu 是在 reg2 要锁存从 reg1 发来的数据之前,需要的最小准备时间。

源时钟锁存沿经过Tclk2延迟后到达Reg2,Tsu为数据采集前最小准备时间,所以数据至少提前锁存沿Tsu的时间到来,因此:

数据锁存时间 Data Required Time = 锁存沿时间 + Tclk2 - Tsu

由公式可知,数据锁存时间延迟跟Tclk2、Tsu有关。

2.3.3 建立时间余量分析

建立时间余量为正值,说明整体设计时序合格,甚至还能跑更高的时钟频率。公式为:

建立时间余量 = D a t a R e q u i r e d T i m e − D a t a A r r i v a l t i m e 建立时间余量 = Data_{ }Required_{ }Time - Data_{ }Arrival_{ }time 建立时间余量=DataRequiredTime−DataArrivaltime

= L a t c h e d g e + T c l k 2 – T s u – ( L u n c h e d g e + T c l k 1 + T c o + T d a t a ) =Latch_{ }edge + Tclk2 –Tsu– (Lunch_{ }edge+ Tclk1 +Tco +Tdata) =Latchedge+Tclk2–Tsu–(Lunchedge+Tclk1+Tco+Tdata)

- 举例:时钟周期Tcyc = 10ns、Tclk1 = 2ns、Tclk2 = 1ns、 Tco = 1ns、Tsu = 0.5ns、Tdata = 3ns;那么建立时间余量为多少?

- 数据到达时间 Data Arrival time = 2 + 1 + 3 =6ns

- 数据锁存时间 Data Required Time = 10 + 1 - 0.5 = 10.5ns

- 建立时间余量 Tsu slack = 10.5 - 6 = 4.5ns

最大主频 = 1 时钟周期 − 建立时间余量 = 1 10 − 4.5 = 222 M h z 最大主频=\frac{1}{时钟周期 - 建立时间余量}=\frac{1}{10 - 4.5}=222Mhz 最大主频=时钟周期−建立时间余量1=10−4.51=222Mhz

只要建立时间余量为正数,那么两个节点之间就能合格的传输数据,那么是不是建立时间余量越大越好?建立时间余量最大是多少呢?

2.3.4 理想建立时间值

理想建立时间 = 锁存沿时间

还是上面那个例子,假如时钟周期为10ns,我们将latch沿的时钟相移动45度(即将时钟左移1.25ns)如图所示:

此时

- 数据到达时间 Data Arrival time = 2 + 1 + 3 =6ns

- 数据锁存时间 Data Required Time = 8.75 + 1 - 0.5 = 9.25ns

- 建立时间余量 Tsu slack = 10.5 - 6 = 3.25ns

时序余量相对于第一个例子的4.5ns,变少了,但没超过锁存沿的时间8.75ns。

那么我们再假如假如时钟周期为10ns,我们将latch沿的时钟相移动-45度(即将时钟右移1.25ns)如图所示:

此时

- 数据到达时间 Data Arrival time = 2 + 1 + 3 =6ns

- 数据锁存时间 Data Required Time = 11.25 + 1 - 0.5 = 11.75ns

- 建立时间余量 Tsu slack = 10.5 - 6 =5.75ns

时序余量相对于第一个例子的4.5ns,变多了,但没超过锁存沿的时间11.25ns。

结论:理想建立关系值和锁存沿时间在评估数据锁存时间是等价的关系,在原理上“建立余量是不可能超过理想建立关系值”,如果超过了,那么两个节点(寄存器)之间的建立关系就违规,或者不合格化了。

2.4 实际保持时间和余量分析

保持时间是寄存器在读取某个数据以后,需用一段最小时间来“确保数据锁存”的稳定。

2.4.1 分析保持时间延迟参数

数据保持时间 Data Hold Time = Tclk1 + Tco + Tdata +时钟周期

数据锁存时间 Data Required Time = 锁存沿 + Tclk2 + Th

保持余量 = 数据保持时间 - 数据锁存时间

- 举例:时钟周期Tcyc = 10ns、Tclk1 = 2ns、Tclk2 = 1ns、 Tco = 1ns、Th = 0.5ns、Tdata = 3ns;那么建立时间余量为多少?

- 数据保持时间 Data Hold Time = 2 + 1 + 3 + 10 =16ns

- 数据锁存时间 Data Required Time = 10 + 1 + 0.5 = 11.5ns

- 保持时间余量 Th slack = 16 - 11.5 = 4.5ns

最后取得的保持余量是 4.5ns,保持余量是正值,所以reg1和reg2之间传输的的保持关系是合格的。

根据保持时间余量公式可以看出,Data Hold Time - Data Required Time 其中的时钟周期相互抵消了,所以保持时间余量跟时钟频率没有关系。

三、总结

数据到达时间 Data Arrival time = Tclk1 + Tco + Tdata

数据锁存时间 Data Required Time = 锁存沿时间 + Tclk2 - Tsu

建立余量公式Setup Slack= 数据锁存时间 - 数据抵达时间

数据保持时间 Data Hold Time = Tclk1 + Tco + Tdata +时钟周期

数据锁存时间 Data Required Time = 锁存沿 + Tclk2 + Th

保持余量 = 数据保持时间 - 数据锁存时间

FPGA静态时序分析与约束(三)、读懂vivado时序报告

参考资料

- 《正点原子 FPGA 静态时序分析与时序约束_V2.3》

- 《FPGA那些事儿–TimeQuest静态时序分析》

- 《FPGA时序约束与分析_吴厚航》