Vivado IP核提供了强大的FIFO生成器,可以通过图形化配置快速生成FIFO IP核。

本文将详细介绍如何在Vivado中配置一个FIFO IP核,以及如何调用这个FIFO IP核。

一、FIFO IP核的配置

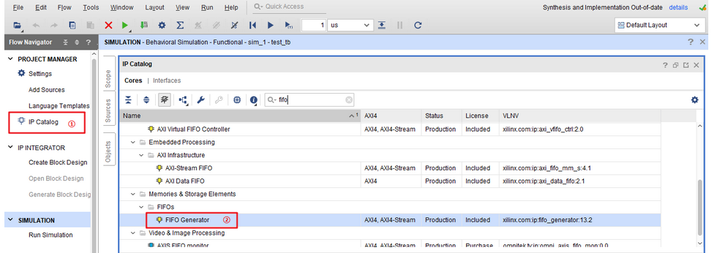

1、新建FIFO IP

在Vivado的IP Catalog中找到FIFO Generator IP核,双击打开参数配置界面。

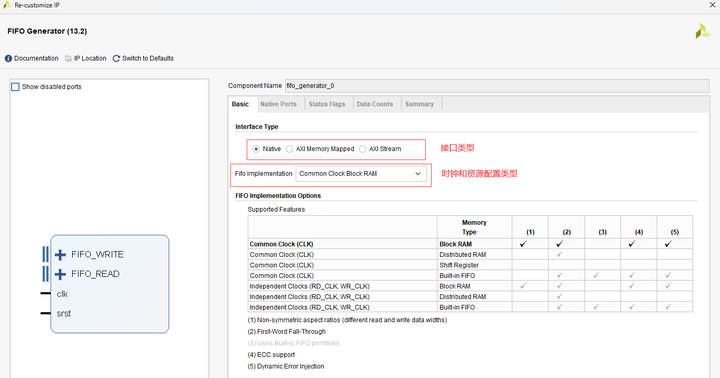

2、配置FIFO基本参数

(1)接口类型

Native interface FIFOs:

这是最基本的FIFO接口,包括数据输入、输出端口、写使能、读使能等信号。

AXI Memory Mapped interface FIFOs:

这种接口将 FIFO 封装为一个AXI内存映射的IP核,可以通过AXI总线进行访问。

AXI4-Stream interface FIFOs:

这种接口兼容AXI4-Stream协议,适合在流式数据传输场景中使用。

(2)时钟类型和资源类型

时钟:同步时钟(common clock) 和 异步时钟(Independent clock)

资源:block RAM、Distributed RAM、Shift Register、Built-in FIFO

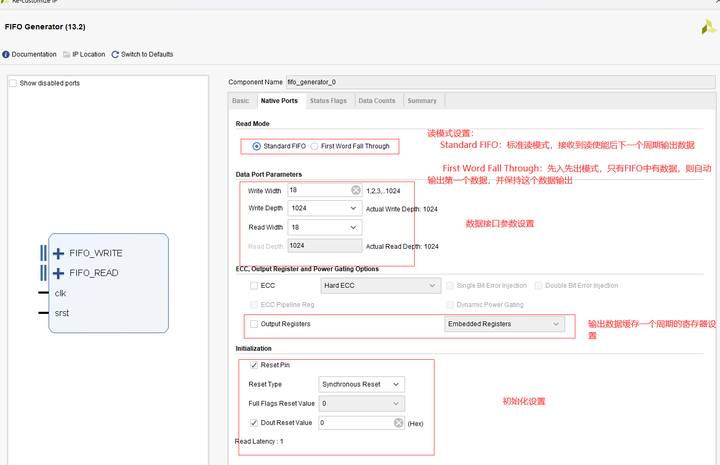

3、配置fifo接口参数

(1)读模式设置

Standard FIFO:标谁读模式,接收到读使能后下一个周期输出数据

First Word Fall Through:先入先出模式,只有FIFO中有数据,则自动输出第一个数据,并保持这个数据输出

(2)数据接口参数设置

FIFO读数据接口的位宽和深度,FIFO写数据接口的位宽和深度

(3)ECC和输出寄存器设置

(4)初始化设置

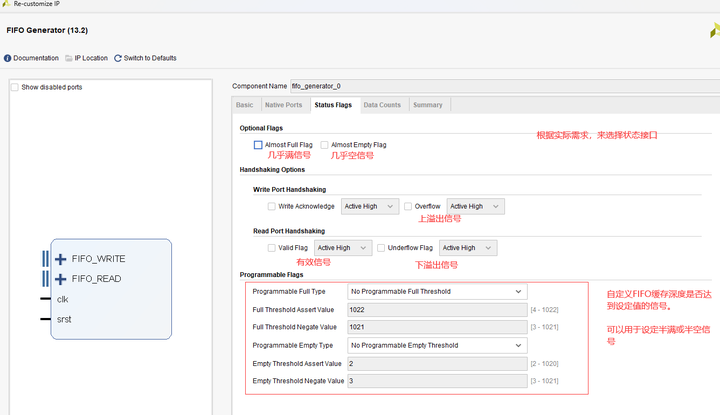

4、状态信号接口设置

根据实际需求,选择对应的状态信号即可。

注意(Programmable Flags):自定义FIFO缓存深度是否达到设定值的信号,可以用于设定半满或半空信号

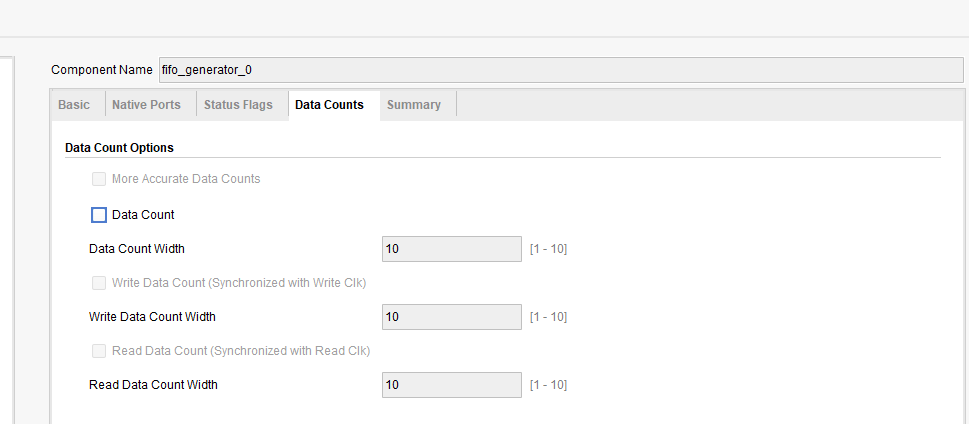

5、计数端口设置

fifo已缓存的数据深度计数,可选。

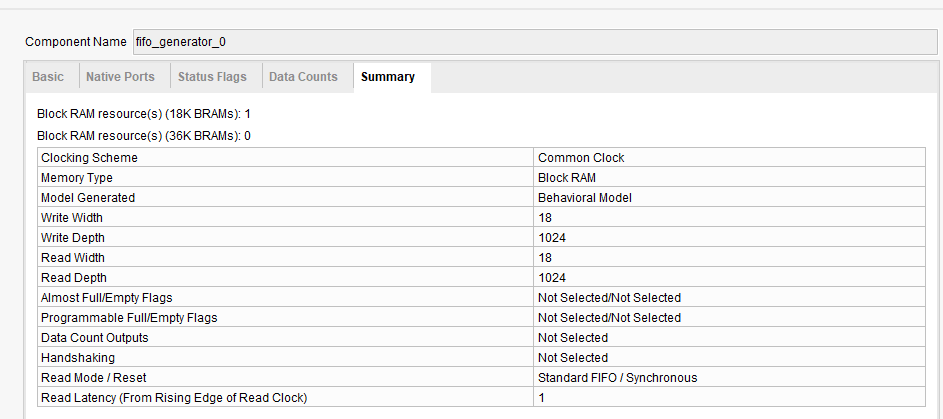

6、FIFO设置参数总览

这是FIFO IP的设置参数总览,可看到资源消耗、宽度、深度、读延迟等信息。

7、点击OK生成FIFO IP核。

二、FIFO IP核的接口

生成的FIFO IP核提供以下接口:

wr_clk 写时钟

rd_clk 读时钟

din 数据输入端口,宽度为配置的Data Width;

wr_en 写使能信号;

rd_en 读使能信号;

dout 数据输出端口;

full 满标志,高电平表示FIFO满;

empty 空标志,高电平表示FIFO空;

almost_full 几乎满标志;

almost_empty 几乎空标志;

valid 有效数据标志

rd_data_count 读计数

wr_data_count 写计数

overflow 写溢出标记

underflow 读溢出标记

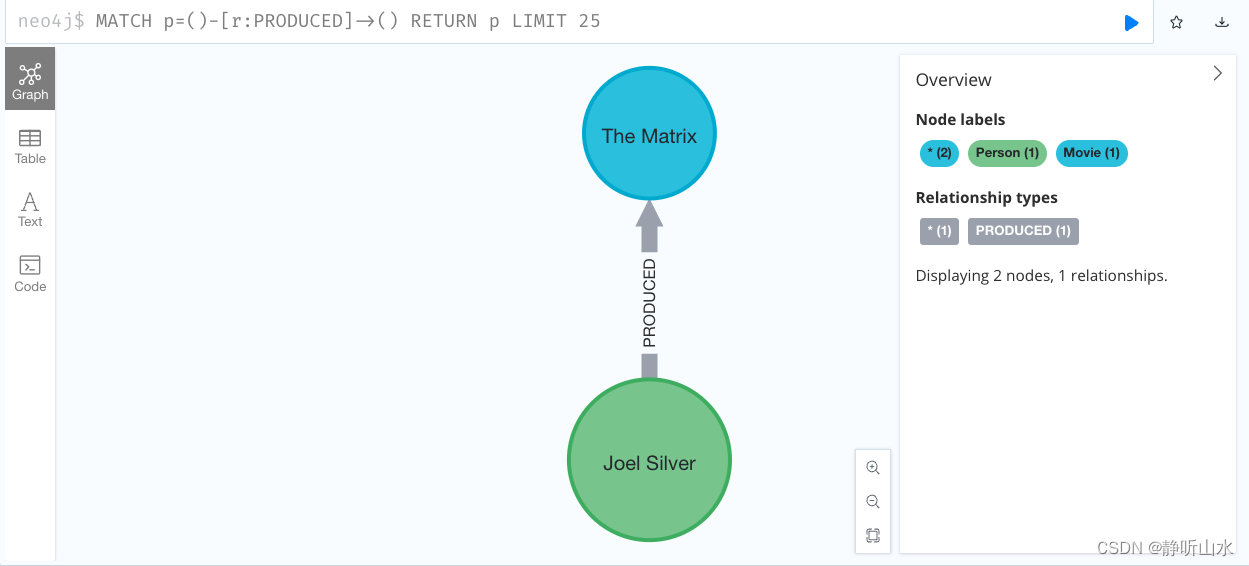

三、FIFO IP核的调用

FIFO IP核的调用很简单,只需要对接口进行适当的连接,并根据Full和Empty标志控制读写使能信号。下面给出一个简单的调用例子:

module fifo_test(input clk,input [17:0] din,input wr_en, rd_en,output valid,output [17:0] dout,output full, empty, overflow, underflow

);fifo_generator_0 fifo_inst(.clk(clk),.din(din),.wr_en(wr_en),.rd_en(rd_en),.dout(dout),.full(full),.empty(empty),.overflow(overflow),.valid(valid), .underflow(underflow)

);endmodule

在这个例子中,din和wr_en分别连接到FIFO的输入端口,dout和empty连接到输出端口。在写入数据时需要检查full信号,在读出数据时需要检查empty信号,以避免overflow和underflow的情况发生。

下面是FIFO IP核的一个简单的testbench:

`timescale 1ns / 1psmodule fifo_testbench();reg clk;

reg [17:0] din;

reg wr_en;

reg rd_en;

wire valid;

wire [17:0] dout;

wire full, empty, overflow, underflow;fifo_test dut(.clk(clk),.din(din),.wr_en(wr_en),.rd_en(rd_en), .dout(dout),.full(full),.empty(empty),.overflow(overflow),.valid(valid), .underflow(underflow)

);always #5 clk = ~clk; initial beginclk = 0;wr_en = 0; rd_en = 0;#10;wr_en = 1; din = 18'd1;#10;wr_en = 1; din = 18'd2;#10;wr_en = 1; din = 18'd3;#10;wr_en = 0; rd_en = 1;#10;wr_en = 0; rd_en = 1;#10;wr_en = 1; din = 18'd4;wr_en = 1; din = 18'd5;#10;wr_en = 0; rd_en = 1;#10wr_en = 0; rd_en = 1;#10;$finish;

endendmodule

这个testbench通过 Applying 不同的读写使能信号来测试FIFO的写入和读取功能。

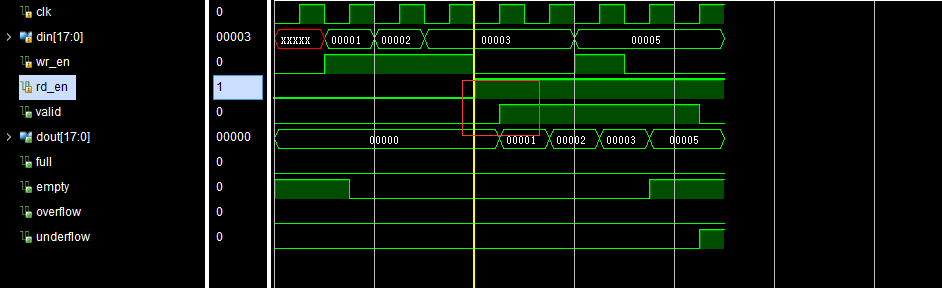

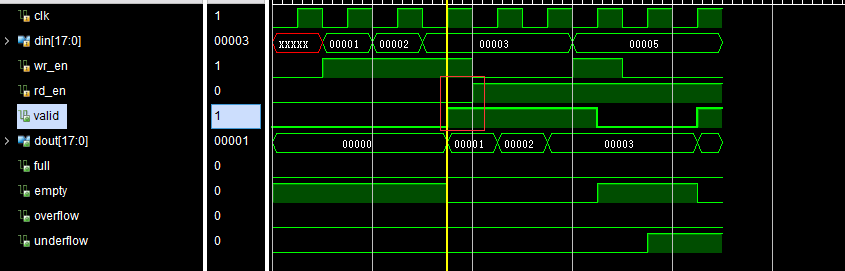

仿真测试图:

(1)FIFO读模式设置为“Standard FIFO”

valid信号完全由rd_en控制。

(2)FIFO读模式设置为“First Word Fall Through”

缓存一定长度数据后,自动读取第一个数据,并保持,直到下一个rd_en 信号到来

四、总结

通过上面的描述,我们详细介绍了如何在Vivado中配置FIFO IP核,FIFO的接口信号,以及如何调用FIFO IP核的一个简单例子。FIFO是一种非常常用的IP核,通过Vivado的FIFO Generator可以大大简化配置和使用FIFO的过程。

xilinx 官方手册:

AMD Adaptive Computing Documentation Portal

夸克网盘分享

本文将不断定期更新中,码字不易,点⭐️赞,收⭐️藏一下,不走丢哦

本文由FPGA狂飙原创,有任何问题,都可以在评论区和我交流哦

获取免费学习资料,github开源代码:“FPGA知识库”

您的支持是我持续创作的最大动力!如果本文对您有帮助,请给一个鼓励,谢谢。