首先在仿真之前,你得有一个ADC。然后是思考如何仿真的问题,如何加激励,如何使用相关工具查看仿真结果。假定你有一个可以仿真的ADC,大致经过下列步骤可以得到ADC的相关动态性能指标。

第一步:在ADC后面接一个理想的DAC。

第二步:确定如何加激励(满足相干采样情况下,设定输入信号频率)。此步为重点

第三步:使用相关工具进行频谱分析,查看结果。

第四步:把参数送到ADE L中的OUTPUT中查看

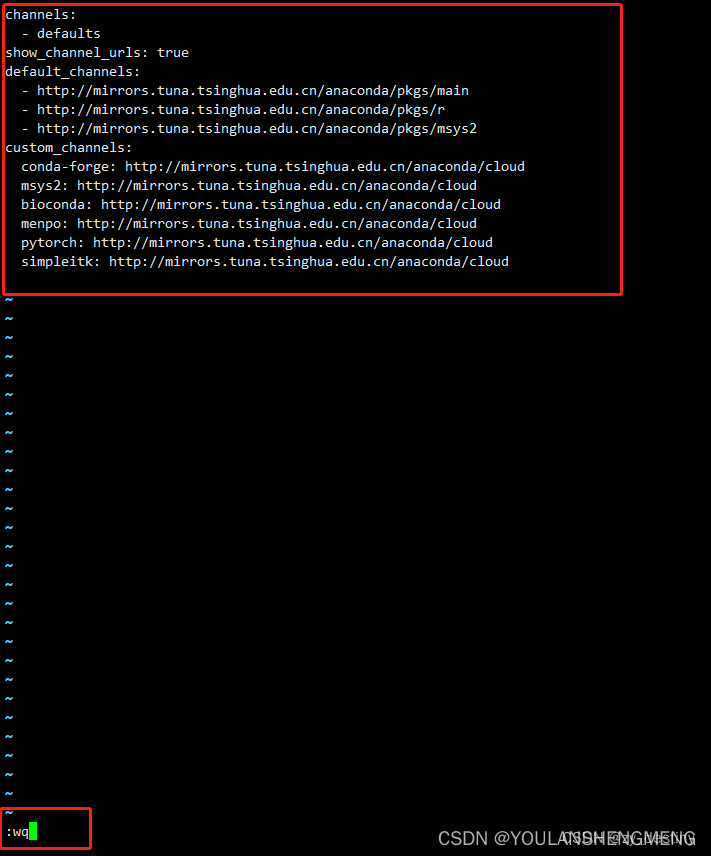

第一步:修改理想DAC的VerilogA代码

至于要在ADC后面加一个理想DAC,对于没有仿真ADC经验的可能不知道。可以参考何乐年老师的《逐次逼近模/数转换器(SAR ADC)设计与仿真》。

那么理想DAC自己写VerilogA吗?有些资料(如陈铖颖的《CMOS模拟集成电路设计与仿真实例——基于Cadence ADE》)的附录中会把代码贴出来,何老师这本书也贴出来了,还贴在正文部分,并且代码中不仅注释有误,其它地方也有错误。我觉得这一点都不友好!对于一个没有交流途径的人来说还以为要自己敲代码呢!!

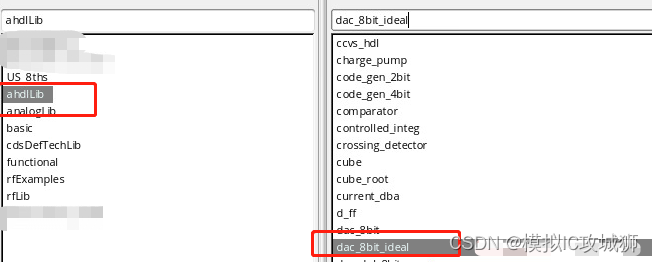

其实Cadence就自带的理想DAC的代码。

位于以下Library中

至于要修改到自己需要的位数,也很简单,相信有一定基础的都可以自己改过来。

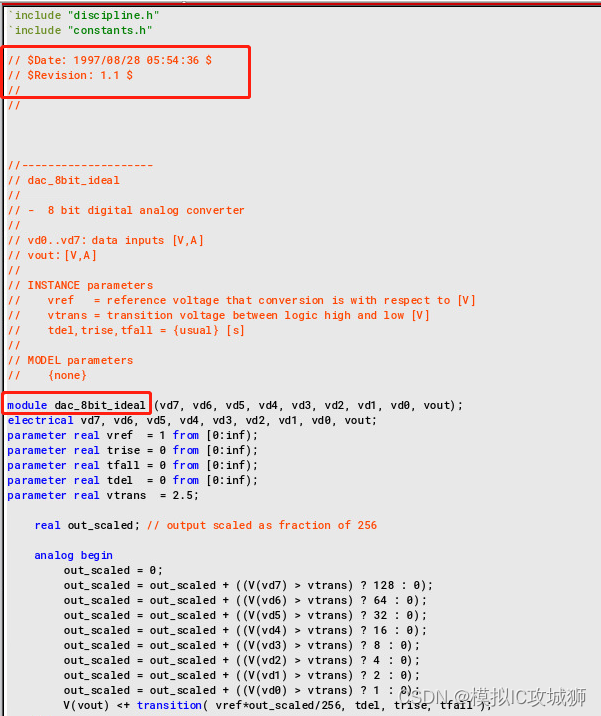

下图是源代码

示例中是 module dac_8bit_ideal,何乐年书中居然这个都没有改过来,当然这都无伤大雅。

有个感慨就是这个示例程序居然是1997年,20多年过去,由此也可见中国与世界的差距!!!

第二步:确定相关输入频率及仿真

这一步是比较重要的一步,也是最容易出错的一步。

重点参考文章:ADC FFT仿真基础_Klein N的博客-CSDN博客_adc fft

我这里就不复制了,以一具体实例,按步骤说明如何操作。

首先要知道以下几个核心要点:

频谱分析工具DFT,在样本点为时有个高效的方法叫FFT

采样若满足相干采样,则不需要加窗函数就可以分析

满足相干采样时,采样频率、信号频率、采样周期数M、采样点数N要满足以下关系:

上面这个关系是进行一切设置的基础。通常取M为质数且奇数,如3、5、13等,N取

下面就重点说明根据上面的公式进行相关的计算:

一、确定采样率

设ADCCLK的周期为40ns,即频率为25MHz,设置采样周期为8CLK,转换周期是12CLK,因此采样时间间隔为20CLK,从而采样率为1/(20*40n)=1.25MSPS(1.25MHz)

(若采样周期为4CLK,采样率为25M/16=1.5625MSPS)

也就是ADCCLK的频率除以采样周期+转换周期。

二、确定采样点N和周期数M

采样点取2^n,这样可以进行FFT分析。此处取M=3,N=128

三、确定AC分析的输入频率fin=fs*M/N

根据采样定理,输入频率要小于1.25M/2=0.625MHz=625KHz。

若M=3,取N=128,则fin=1.25M*3/128=29.296875KHz

四、确定仿真时间

如果采样M个周期,每个周期时间1/fin,则:

T=M/fin=N/fs=128/1.25M=102.4us。仿真时,稍微多点时间,保证后面分析时,取数据取在非跳变处。比如仿真110us。

由这个公式也可以看出,在采样率确定的情况下,N越大需要的仿真时间越长,而与输入信号频率无关。

至此,已经考虑到有如何加激励,设置多长的仿真时间的问题。

接下来就是在电路图做好设置,就可以仿真啦。

如果仿真时间比较长,比如取4096个点,那仿真时间可能无法接受。可以考虑使用多核

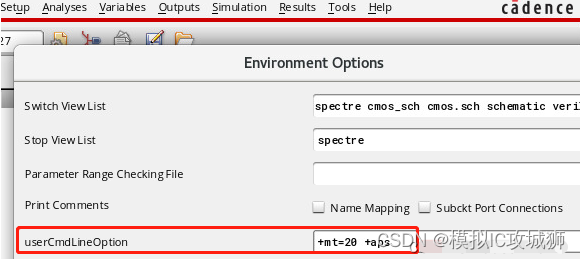

在ADE窗口中:Setup>Environment,弹出如下窗口,加上:

+mt=20 +aps

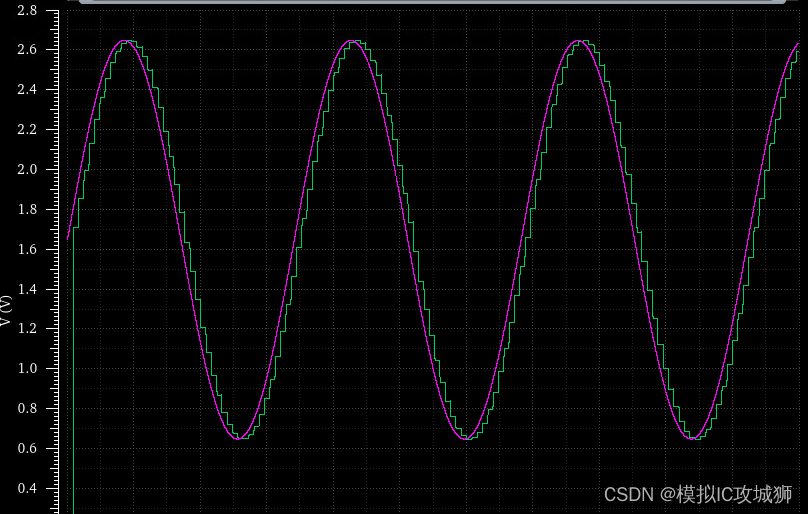

仿真完成后,波形大概如下:

从图中可以看出,正弦信号经过ADC转换,再经过理想DAC的转换,基本靠谱。

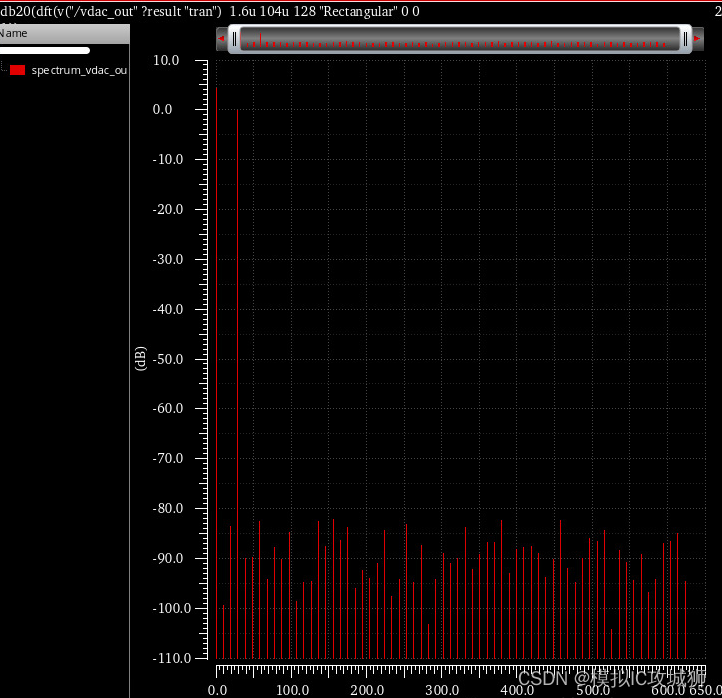

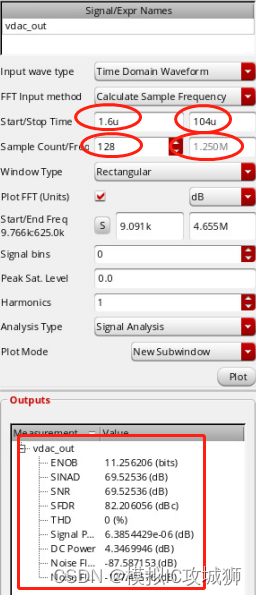

第三步:设置参数并查看结果

得到瞬态仿真波形后,接下来就是对信号进行频谱分析。

分析方法可以采用:

1.Cadence Spectrum工具

2.MATLAB计算

Spectrum工具的调用,可以参考:cadence-virtuoso中的FFT分析 - 知乎

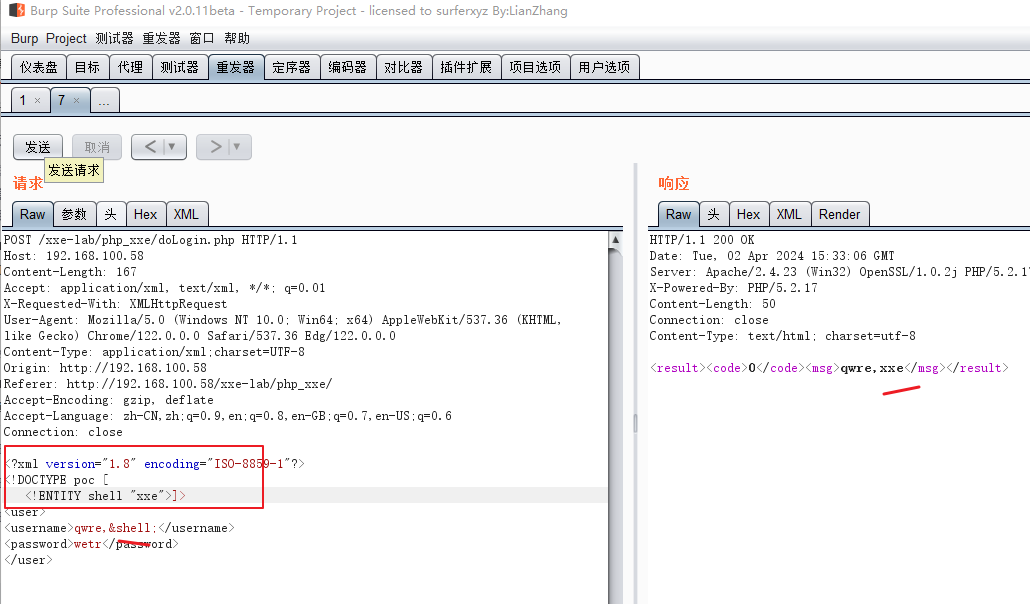

这里要重点说明的是开始时间、结束时间、采样点数。

比如此文中,采样点是128个,采样周期是3个,采样时间是102.4us

因此在设置时,首先选择一个稳定的点,比如本文选的1.6us,那么结束时间就为102.4+1.6=104us

再在下面的采样点中输入128,那么灰色的采样率将会与你预设的一致!!!

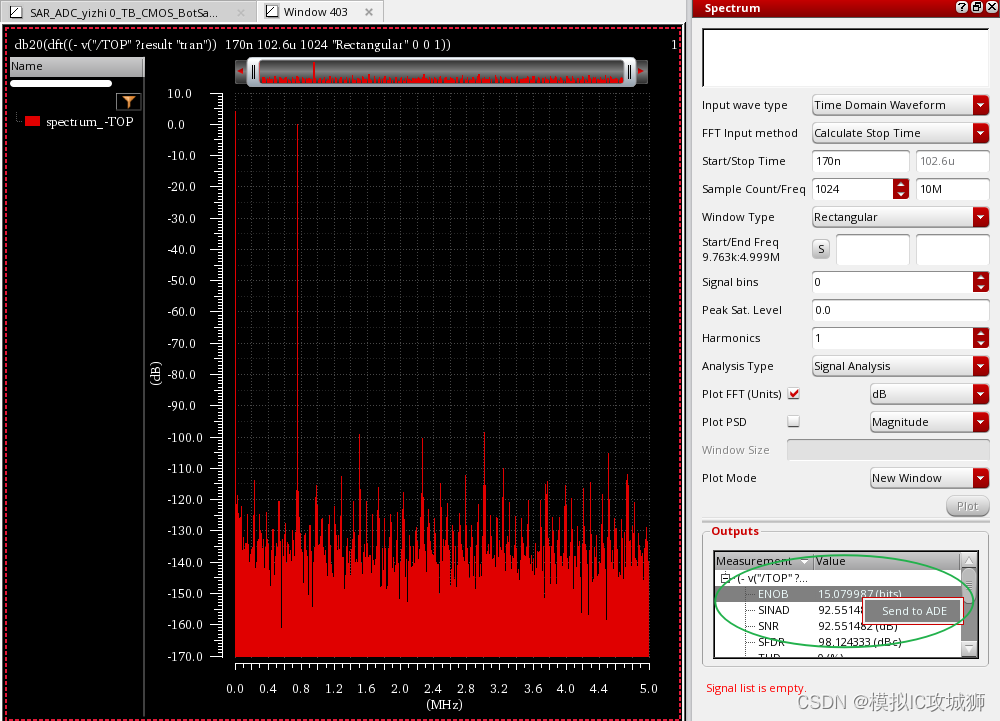

如下图所示。

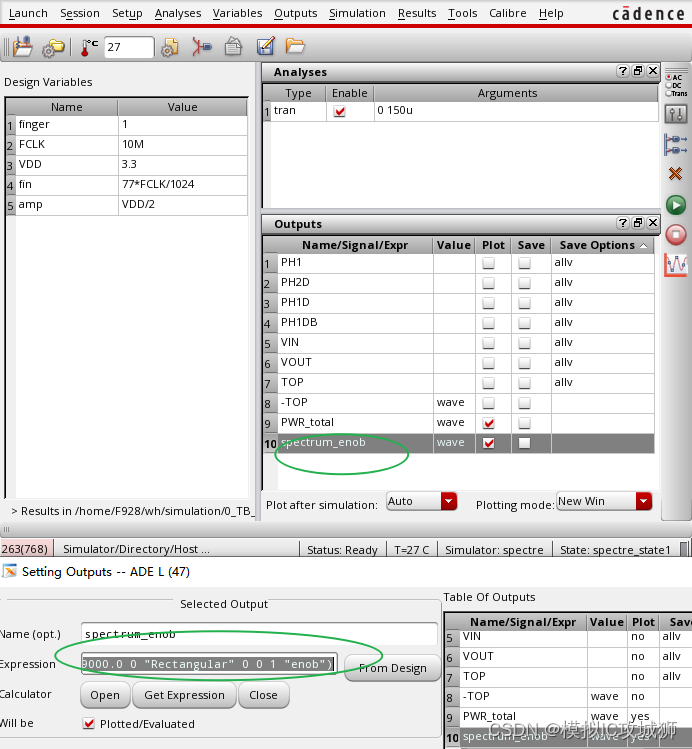

第四步:把参数送到ADEL中的OUTPUT中查看