文章目录

- 一、sim_speedup_control信号

- 二、

一、sim_speedup_control信号

一般来说我们自己进行仿真时候该信号都直接给1,之前的高速IP核好像并没有出过错误,但是10G PCSPMS IP核进行仿真的时候,该信号必须要先置为0,等待用户复位结束之后在coreclk上升沿拉高该信号,才能使得仿真时候的rx_resetdone正常拉高。

二、

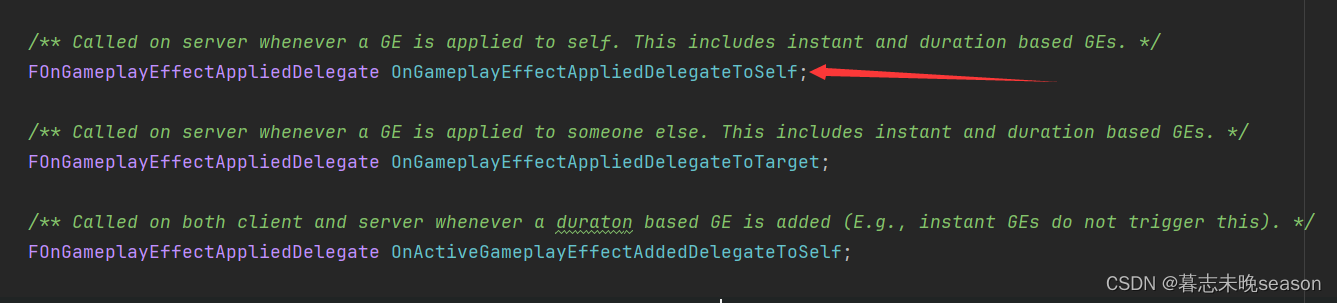

用户输入XGMII数据的时候,必须要等待w_block_sync信号拉高,否则XGMII_TX接口处的数据正确,接收端也无法接收数据。

w_block_sync信号来自于core_status[0]

AXIS_test_module AXIS_test_module_u0(.i_clk (w_xgmii_clk ),.i_rst (w_xgmii_rst || (!w_block_sync)),.m_axis_tdata (s_axis_tdata ),.m_axis_tuser (s_axis_tuser ),.m_axis_tkeep (s_axis_tkeep ),.m_axis_tlast (s_axis_tlast ),.m_axis_tvalid (s_axis_tvalid ),.s_axis_tready (s_axis_tready )

);