1 ZYNQ-7000简介

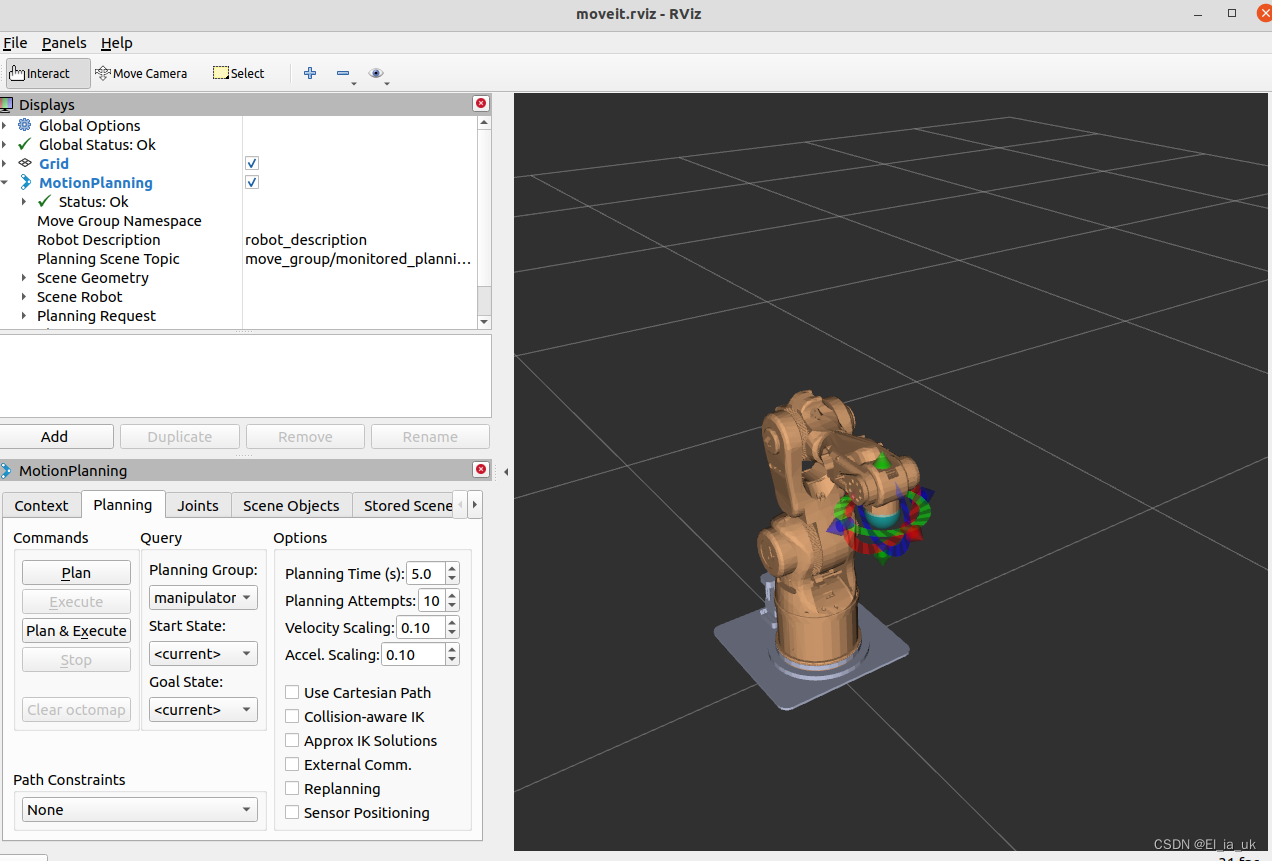

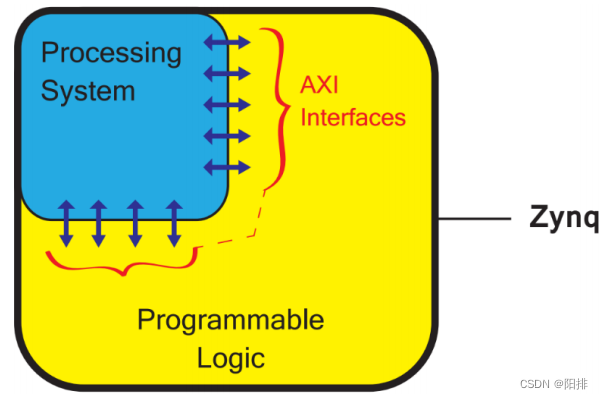

ZYNQ 是由两个主要部分组成的:一个由双核 ARM Cortex-A9 为核心构成的处理系统(PS,Processing System),和一个等价于一片 FPGA 的可编程逻辑(PL,Programmable Logic)部分。两者之间通过AXI高速接口连接。

1.1 ZYNQ PL简介

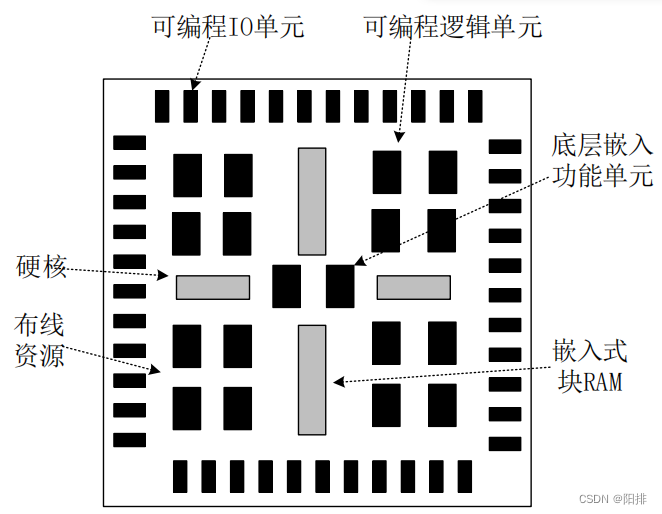

PL(可编程逻辑)就是FPGA,FPGA基本结构:

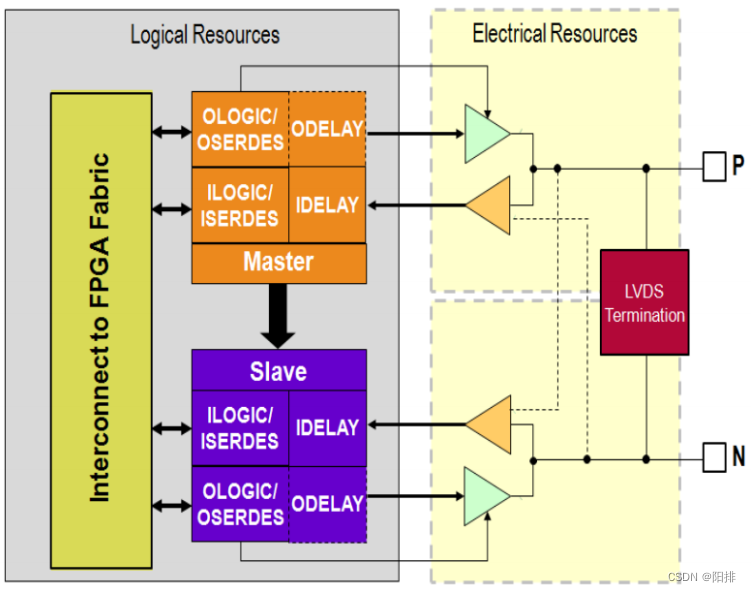

1、可编程I/O单元:

FPGA上的每一个通用输入输出功能(IOB)都有一个焊盘,与芯片外部 连接用作信号的输入输出。

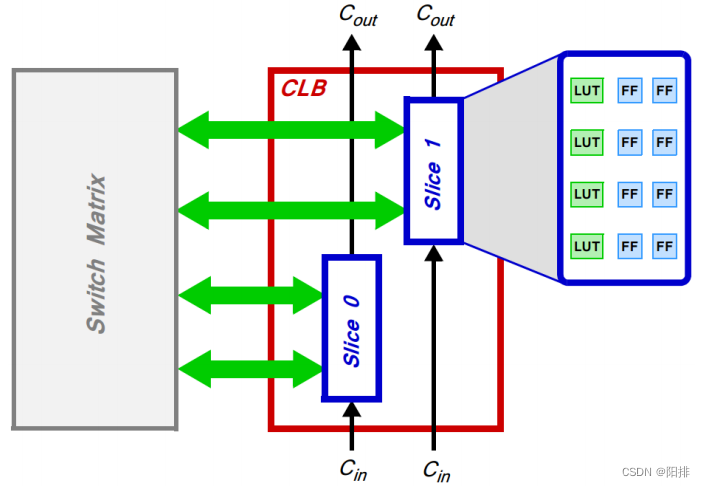

2、基本可编程逻辑单元:

FPGA基于SRAM工艺,基本可编程逻辑单元几乎都是由查找表(LUT)和寄存器(Register)组成。Xilinx 7系列的FPGA为6输入查找表。

Xilinx 7系列的FPGA中的可编程逻辑单元称为CLB(可配置逻辑块),每个CLB中包含两个逻辑片(Slice)。每个 Slice 由 4 个查找表、8 个触发器和其他一些逻辑所组成的。

CLB示意图如下:

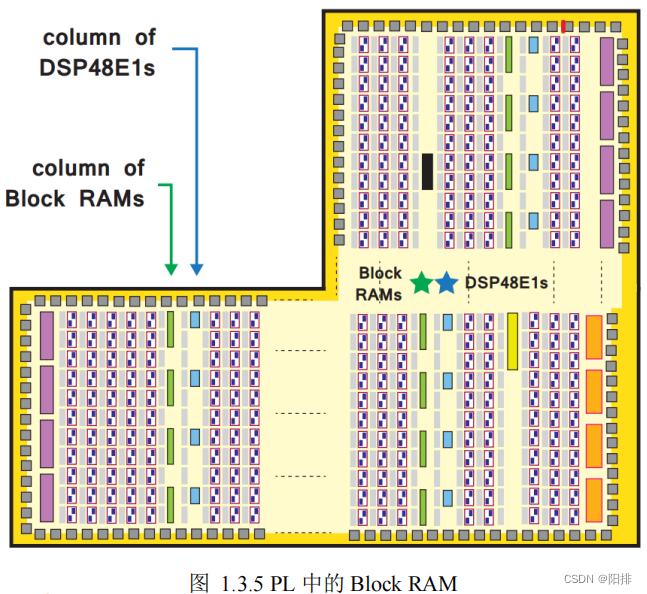

3、嵌入式块RAM:

目前大多数 FPGA 都有内嵌的块 RAM(Block RAM),FPGA 内部嵌入可编程 RAM 模块。绿色的长条方块就是Block RAM。

除了块 RAM,还可以灵活地将 LUT 配置成 RAM,ROM,FIFO 等存储结构,这种技术被称为分布式 RAM。

4、丰富的布线资源:

布线资源连通 FPGA 内部的所有单元,而连线的长度和工艺决定着信号在连线上的驱动能力和传输速度。FPGA 芯片内部有着丰富的布线资源,这些布线资源根据工艺、长度、宽度和分布位置的不同而划分为4 类不同的类别:

第一类是全局布线资源,用于芯片内部全局时钟和全局复位/置位的布线;

第二类是长线资源,用以完成芯片 Bank 间的高速信号和第二全局时钟信号的布线;

第三类是短线资源,用于完成基本逻辑单元之间的逻辑互连和布线;

第四类是分布式的布线资源,用于专有时钟、复位等控制信号线。

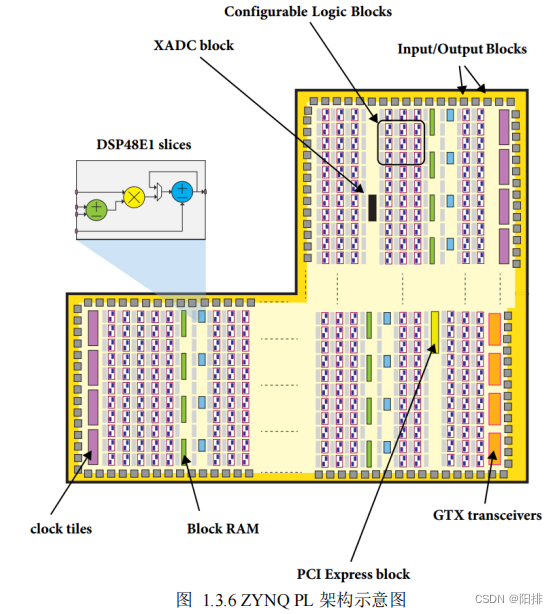

5、底层嵌入功能单元:

PLL(Phase Locked Loop)、DLL(Delay Locked Loop)、DSP、CPU 等。

6、内嵌专用硬核:

数模混合模块(XADC),就是一个硬核。XADC包含两个模数转换器(ADC),一个模拟多路复用器,片上温度和片上电压传感器等。我们可以利用这个模块监测芯片温度和供电电压,也可以用来测量外部的模拟电压信号。

PL架构示意图:

1.2 ZYNQ PS简介

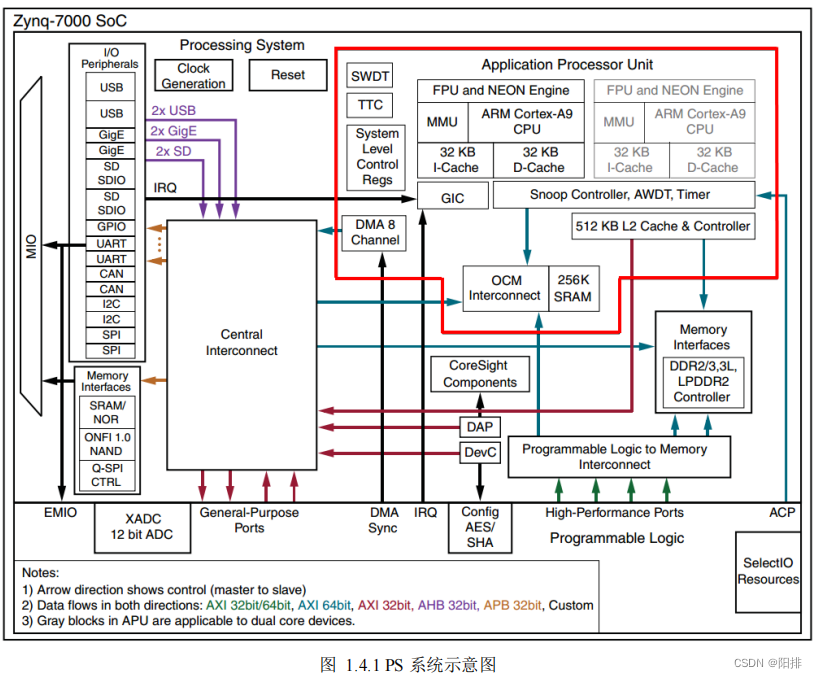

PS为双核 ARM Cortex-A9 为核心构成的处理系统,形成了一个应用处理器单元(Application Processing Unit,APU),另外还有扩展外设接口、cache 存储器、存储器接口、互联接口和时钟发生电路等。

在 ZYNQ 中,PL 和 PS 两部分的供电电路是独立的,这样 PS 或 PL 部分不被使用的话就可以被断电。

PS系统示意图如下:

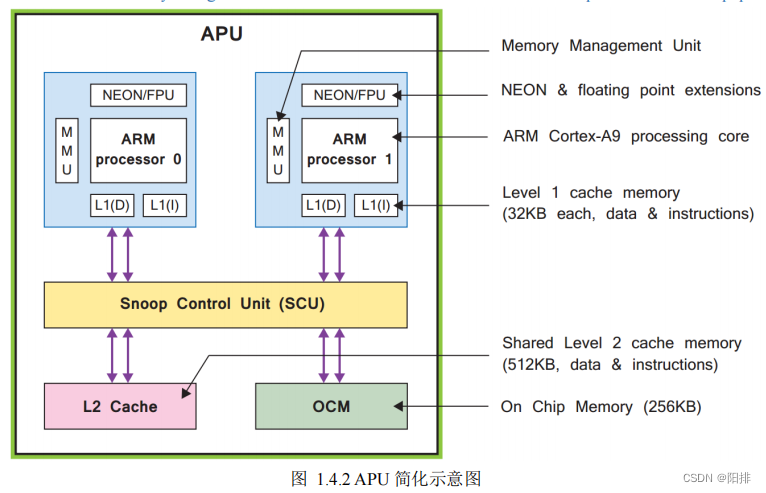

1、APU:

一致性控制单元(SCU)在ARM核心、二级Cache缓存和OCM存储器之间形成了桥接。SCU还部分负责与PL 对接,图中没有标明这个接口。

2、外部接口:

SPI、I2C、CAN、UART、GPIO、SD、USB、GigE。

3、存储器接口:

包含一个动态存储器控制器和几个静态存储器接口模块。动态存储器控制器可以用于 DDR3、DDR3L、DDR2 或 LPDDR2。静态存储器控制器支持一个 NAND 闪存接口、一个 Quad-SPI 闪存接口、一个并行数据总线和并行 NOR 闪存接口。

4、片上存储器:

片上存储器包括 256kB 的 RAM(OCM)和 128kB 的 ROM(BootROM)。OCM 支持两个 64 位 AXI 从机接口端口,一个端口专用于通过 APU SCU 的 CPU/ACP 访问,而另一个是由 PS 和 PL 内其他所有的总线主机所共享的。BootROM 是 ZYNQ 芯片上的一块非易失性存储器,它包含了 ZYNQ 所支持的配置器件的驱动。BootROM 对于用户是不可见的,专门保留且只用于引导的过程。

5、AXI接口:

AXI 的英文全称是 Advanced eXtensible Interface,即高级可扩

展接口,它是 ARM 公司所提出的 AMBA(Advanced Microcontroller Bus Architecture)协议的一部分。

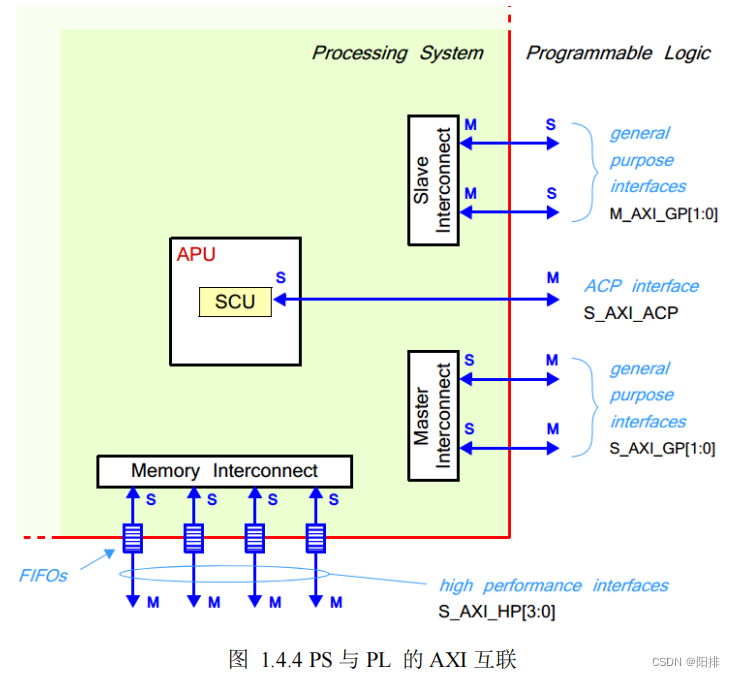

在 PS 和 PL 之间的主要连接是通过一组 9 个 AXI 接口,每个接口有多个通道组成。这些形成了 PS 内部的互联以及与 PL 的连接,如下图所示:

PS 和 PL 之间的 9 个 AXI 接口可以分成三种类型:

1、通用 AXI(General Purpose AXI):一条 32 位数据总线,适合 PL 和 PS 之间的中低速通信。接口是透传的不带缓冲。总共有四个通用接口:两个 PS 做主机,另两个 PL 做主机。

2、加速器一致性端口(Accelerator Coherency Port):在 PL 和 APU 内的 SCU 之间的单个异步连接,总线宽度为 64 位。这个端口用来实现 APU cache 和 PL 的单元之间的一致性。PL 是做主机的。

3、高性能端口(High Performance Ports):四个高性能 AXI 接口,带有 FIFO 缓冲来提供“批量”读写操作,并支持 PL 和 PS 中的存储器单元的高速率通信。数据宽度是 32 或 64 位,在所有四个接口中 PL 都是做主机的。

| 接口名 | 接口描述 | 主机 | 从机 |

|---|---|---|---|

| M_AXI_GP0 | 通用AXI(AXI_GP) | PS | PL |

| M_AXI_GP1 | 通用AXI(AXI_GP) | PS | PL |

| S_AXI_GP0 | 通用AXI(AXI_GP) | PL | PS |

| S_AXI_GP1 | 通用AXI(AXI_GP) | PL | PS |

| S_AXI_ACP | 加速器一致性端口(ACP),缓存一致性交互 | PL | PS |

| S_AXI_HP0 | 带有读写FIFO的高性能端口(AXI_HP) | PL | PS |

| S_AXI_HP1 | 带有读写FIFO的高性能端口(AXI_HP) | PL | PS |

| S_AXI_HP2 | 带有读写FIFO的高性能端口(AXI_HP) | PL | PS |

| S_AXI_HP3 | 带有读写FIFO的高性能端口(AXI_HP) | PL | PS |

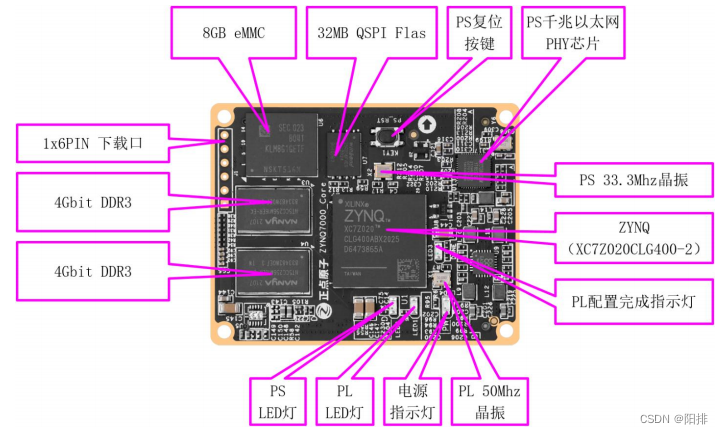

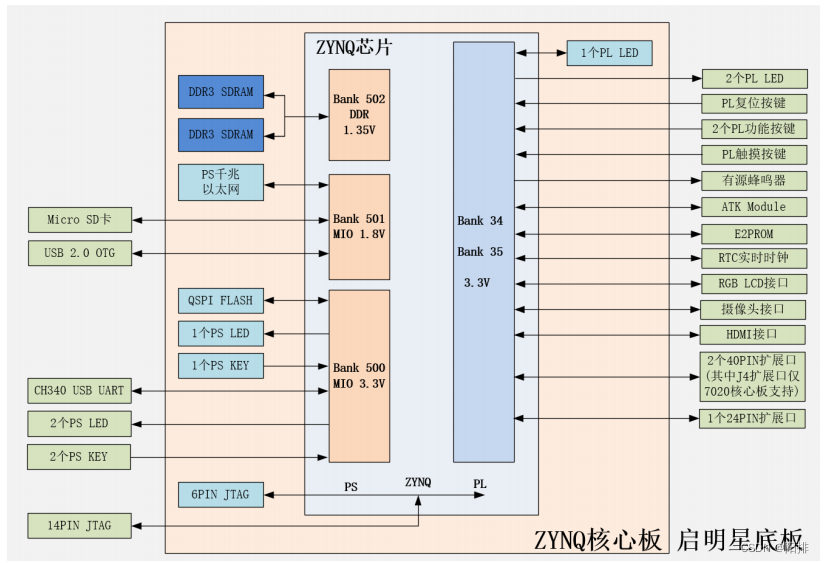

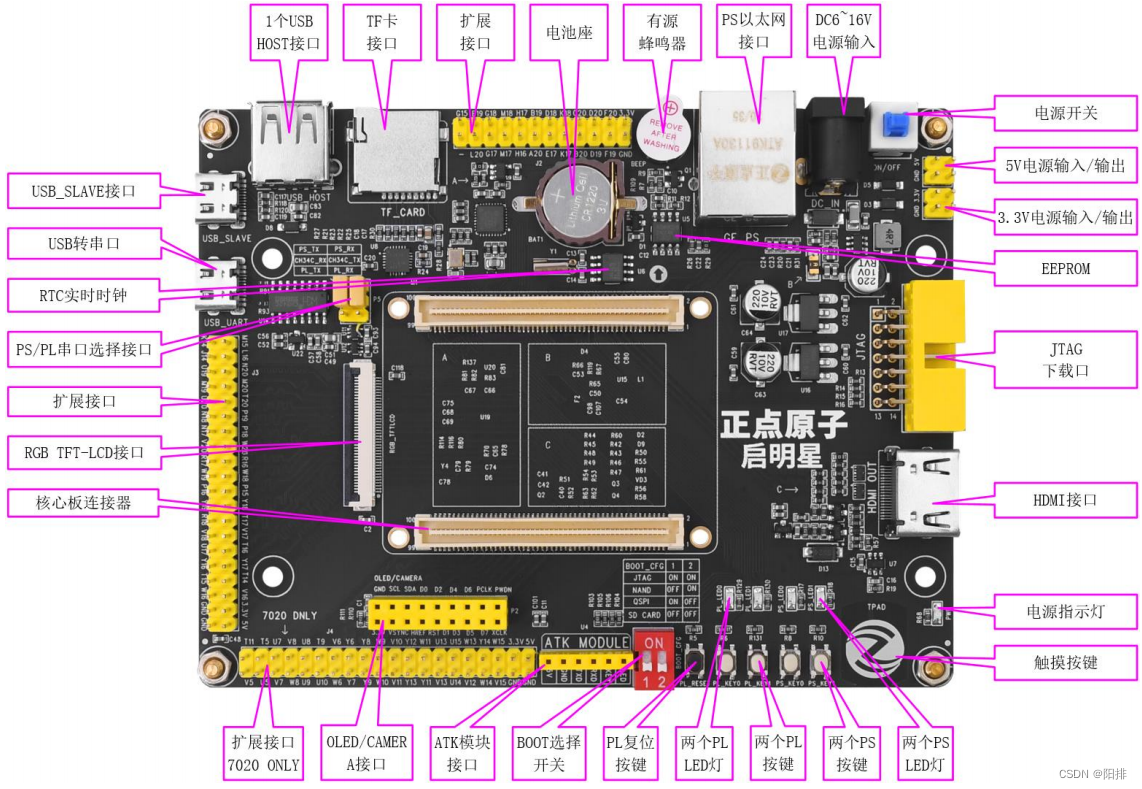

1.3 正点原子ZYNQ7000核心板及底板简介

ZYNQ 芯片采用 Xilinx 公司的 ZYNQ7000 系列芯片,ZYNQ-7020 核心板的 ZYNQ 芯片型号为 XC7Z020CLG400-2,PL 逻辑单元多达 85K,BRAM 存储资源为 4.9Mbit;

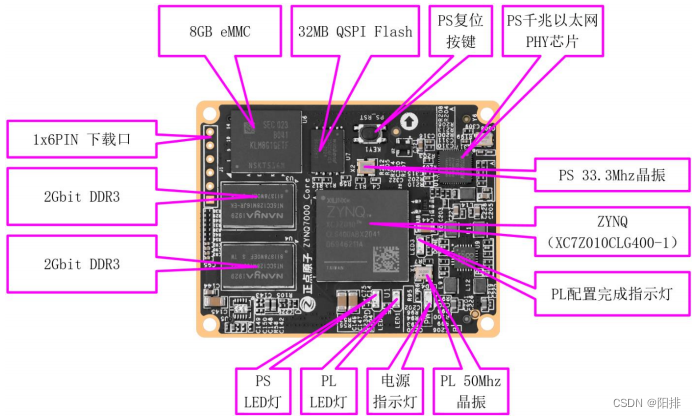

ZYNQ-7010核心板的 ZYNQ 芯片型号为 XC7Z010CLG400-1,PL 逻辑单元多达 28K,BRAM 存储资源为2.1Mbit;

两种 ZYNQ 芯片的处理器系统均为双核 Cortex-A9 结构。

需要注意的是,ZYNQ-7020核心板主控芯片的速度等级为“-2”(最高766MHz),ZYNQ-7010 核心板主控芯片的速度等级为“-1”(最高666MHz),因此 ZYNQ-7020 核心板主控芯片的速度等级更高,所支持的频率也更高。

2 片 DDR3 SDRAM,ZYNQ-7020 核心板的 DDR3 型号为NT5CC256M16,每片 4Gbit,总容量为 8Gbit(1GB);

ZYNQ-7010 核心板的 DDR3 型号为 NT5CC128M16,每片 2Gbit,总容量为 4Gbit(512MB)。

组成双路DDR3的原因:提高带宽,增大读写能力。

7020核心板资源:

7010核心板资源:

硬件资源:

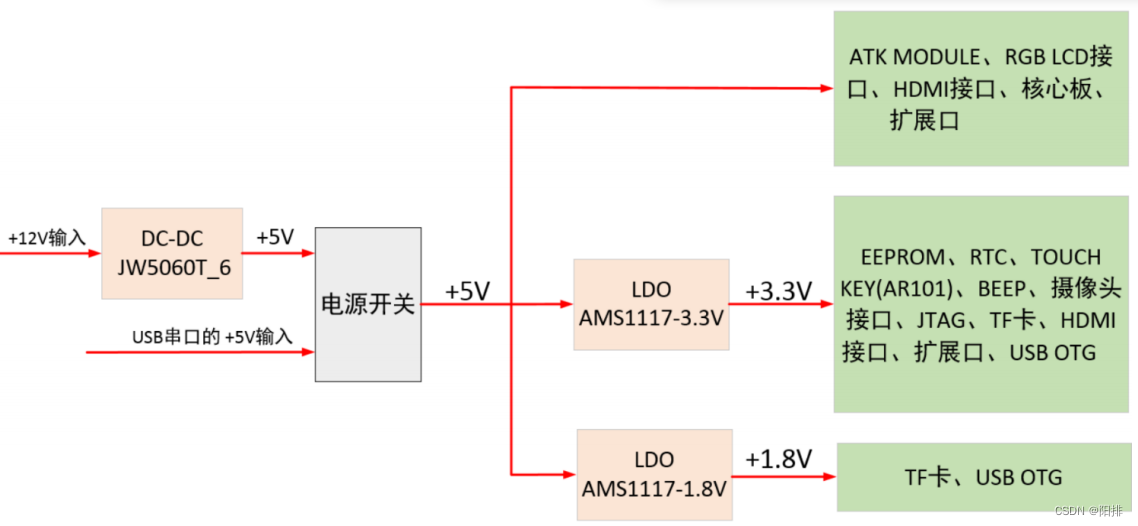

底板电源拓扑结构: