目录

1.概述

2. Cache映射模式

3.DCache的数据一致性

4.小结

1.概述

上一篇Cache基本原理--以TC3xx为例(1)-CSDN博客,我们聊了Cache基本概念,接下来我们将继续聊Cache映射模式,DCache的数据一致性问题。

2. Cache映射模式

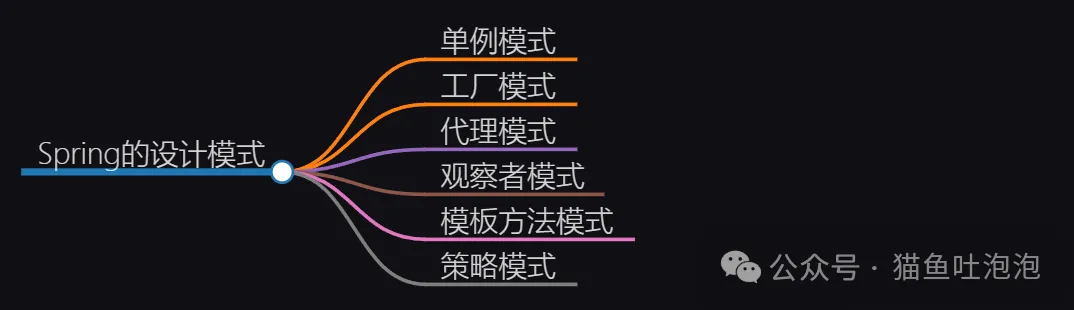

常见的Cache地址映射模式包括直接映射、组相联和全相联。

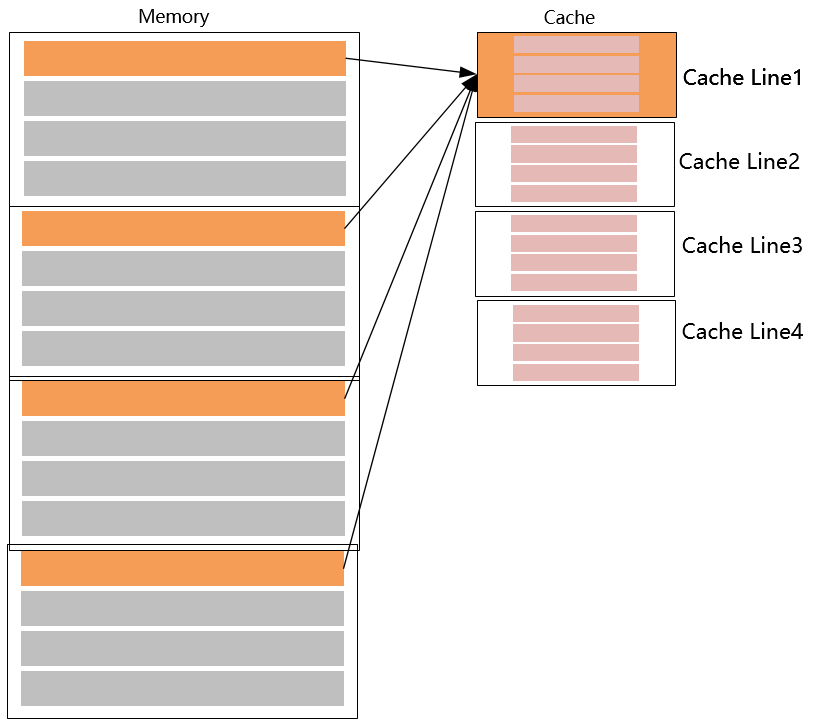

直接映射(Direct Mapping):在直接映射中,每个主存地址只能映射到Cache中的唯一一行。这意味着主存中不同块可能会填充到相同的Cache Line里。如下图:

组相联(Set Associative Mapping) :Cache被划分为多个Set,每个Set包含多个Way的Cache Line。主存地址被映射到某个Set,然后在该Set内进行查找。每个Set内的CacheLine数量通常是2的幂次方,例如2、4、8等。组相联映射通过减少冲突提高了缓存的性能。

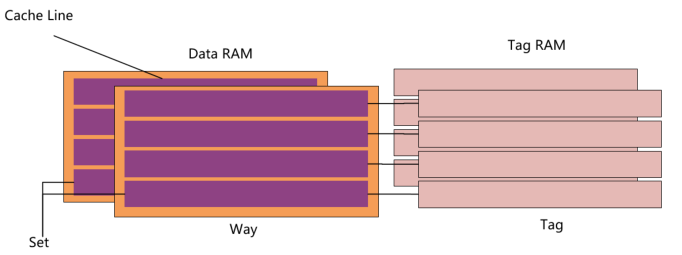

上面有点晕不要慌,这里就不得不来点术语了。如下图所示:

Way -- 相当于Cache的一页,如上述示例,Cache就有2 Ways

Set -- 每个Way里的同一Cache Line组成Set

这里理解了,英飞凌描述的2-way set associative DCache是不是就手拿把攥了。

英飞凌每个CPU都有16K DCache,Cache Line为32Bytes,因此总共有512个Cache Line。那么针对memory地址就可以分为:

我们计算非Tag后的偏移2^14 = 16KB,这也与Cache Size刚好对上。

全相联映射(Fully Associative Mapping): 主存地址可以映射到Cache中的任何一行,而不受限制于特定的组。这意味着任何Cache Line都可以存储任何主存地址的数据。全相联映射通常需要更多的硬件支持,如标记比较电路,但可以最大程度地减少冲突,提高缓存的命中率。

3.DCache的数据一致性

谈到DCache的数据一致性,就不得不先讨论Cache的写策略。

常见的Cache写策略分为Write-Through和Write-Back。

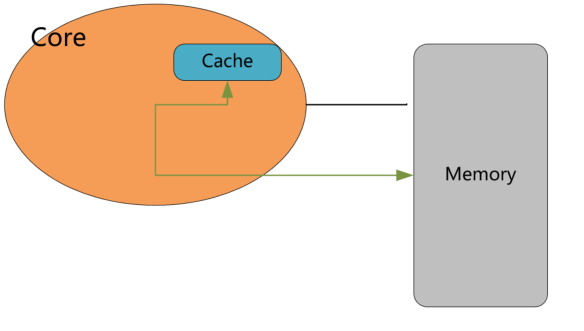

Write-Through :修改数据时,该修改会同时作用在Cache和Memory中,如下图:

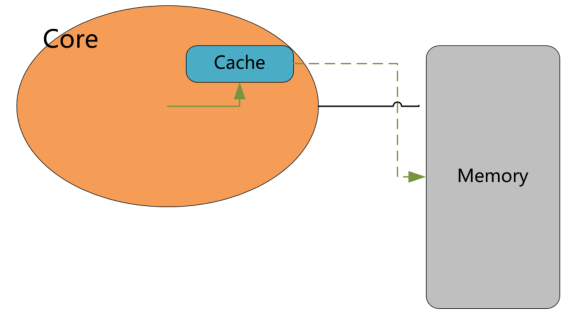

Write-Back:修改数据时,会先发生在Cache里,Memory中的母本更新会等待一些时间:

以英飞凌TC3xx系列为例,我们来看它是如何出现数据一致性问题的(注意TC3xx是Write Back Cache)。

CPU0\1共享LMU0,CPU0和CPU1同时修改LMU0[3]的值 3->9、LMU0[2]的值 2 -> 8,我们可以看到LMU0里的值确实变为了9,但是思考一下,这时候CPU1去获取LMU0[3],应该是几?当然是Cache里面的3,这里数据就不一致了。紧接着由于CPU1中的Cache数据改变也反映到了LMU0中,此时可以发现,LMU0[3]变为了3,cpu0的修改出现了丢失了。因为Cache的更新至少得以Cache Line为单位。

那么,如何来避免这些问题呢?翻看TC3xx Aurix 内核手册,可以得到以下几种方式:

- 使用cachea指令:cachea.wi将写策略强制更新为write-through;cachea.i重刷cache

- 使用英飞凌提供的Non-cache地址,例如LMU使用0xB开头;

4.小结

以上,我们简述了cache的基本原理,从软件工程师角度,了解Cache,知道Cache通常会带来什么好处,引起什么问题,这对我们在系统层级的性能优化是有巨大帮助的。