软件版本:Anlogic -TD5.9.1-DR1_ES1.1

操作系统:WIN10 64bit

硬件平台:适用安路(Anlogic)FPGA

实验平台:米联客-MLK-L1-CZ06-DR1M90G开发板

板卡获取平台:https://milianke.tmall.com/

登录"米联客"FPGA社区 http://www.uisrc.com 视频课程、答疑解惑!

1概述

SPI(Serial Peripheral Interface,串行外围设备接口)通讯协议,是Motorola 公司提出的一种同步串行接口技术,是一种高速、全双工、同步通信总线,在芯片中只占用四根管脚用来控制及数据传输,广泛用于 EEPROM、Flash、RTC(实时时钟)、ADC(数模转换器)、DSP(数字信号处理器)以及数字信号解码器上,是常用的、重要的低速通讯协议之一。本节我们主要学习SPI通信的原理。

SPI通信协议简介:

SPI是一种高速的、全双工、同步、主从式的串行总线接口,也是各类嵌入式设备以及FPGA应用开发中常用的一种串行通信接口。SPI的接口速度可以最高到上百兆,因此SPI接口不仅仅可以应用于低速设备进行合理的时序设计,也可以用于一些高速串行外设通信。

采用SPI接口的设备一般兼顾低速通信和上百兆的高速通信,比如最常见的FPGA的配置FLASH,最高可以支持100Mbps以上。FPGA内置的SPI配置控制器,可以支持多数据总线方式:X1 X2 X4 X8模式,这样大大提高配置速度,减少配置时间,另外比如高精度ADC芯片AD7606,可以采用自定义SPI协议完成多路高精度ADC的实时采集。

相比嵌入式单片机或者ARM已经集成了的SPI控制器,FPGA的SPI控制器完全由逻辑代码实现,我们可以在FPGA上自己设计SPI控制器然后应用于我们的项目中。

学习FPGA一定要具备非常熟练的FPGA代码设计能力,作为入门学习,掌握SPI串行控制器设计的意义不仅仅是SPI的实用性,更重要的是通过这些简单接口时序的设计,增加初学者原创代码的设计能力,创造能力,这些基础的能力是我们以后面对复杂问题,解决FPGA代码构架设计、通信接口设计、时序逻辑设计的关键能力。

对于SPI Master主设备(所谓的主设备也就是所有的数据发送或者发起者):

SCLK:(spi clock)时钟,由Master发送,用于同步数据,决定了通信速率,不同设备支持的最高时钟频率不同

MOSI:(master out slave in)主设备输出数据,从设备输入数据,信号线上的数据方位由主机到从机

MISO:(master in slave out)主设备输入数据,从设备输出数据

SS:(slave selcet)从设备选择,该信号由Master主机产生,

对于SPI SLAVE从设备:

SCLK:(spi clock)时钟,该时钟由Master主机产生

SIMO:(slave in master out)从机接收来自主机发送的数据

SOMI:(slave out master in)从机发送数据

SS:(slave selce)t从设备选择,该信号由Master主机产生

寻址方式:

需要注意对于SPI控制器数据位宽可以X1 X2 X4 X8方式,SS选通的外设根据控制器的设计也可以支持多个。当有多个SPI Slave与SPI Master相连时,都共同使用SCK、MOSI、MISO这三条总线,每一个SPI Master都有独立的片选信号(SS),通过SS片选信号来决定和哪台从设备进行通信。更复杂的SPI控制器才能通过SS信号进行总线的竞争实现多主机的仲裁。

以下方案中主控制器通过SS0~SS1可以选通多个SPI外设。当主设备要和某个从设备进行通信时,主设备需要先向对应从设备的片选线上发送使能信号(高电平或者低电平,根据从机而定)表示选中该从设备。如果使能多个SS片选信号,则MISO线上的数据会被破坏,因为主机无法识别哪个从机正在传输数据。

通信过程:

要开始SPI通信,主机必须发送时钟信号,并通过使能SS信号选择从机。只有片选信号SS拉低(或者拉高),MOSI和MISO在SCLK每一个周期传送一位数据。SPI总线在进行数据传送时,没有硬性规定先传送高位还是低位,但是通信双方要约定好相同的传送方式,一般采用先传送高位,后传送低位。例如下图,MOSI和MISO同时从高位开始传输,一个字节传送完成后无需应答即可开始下一个字节的传送,八个时钟周期即可完成一个字节数据的传送。

多从机配置:

主机可以通过将从机的CS片选信号来选择要与之通信的从机,从机可以采用常规模式连接,或采用菊花链模式连接。

常规SPI模式

主机上可以有多个CS引脚,允许多个从机并联接线。如果主机只有一个CS引脚,则可以通过菊花链将多个从器件连接到主机。所有从机的片选信号连接在一起,所有从机同时接收同一SPI时钟,来自主机的数据直接送到第一个从机,该从机将数据提供给下一个从机,依此类推。然而在这种方法中,当数据从一个从机传SDO播到下一个从机SDI时,会有周期延迟。

菊花链SPI模式

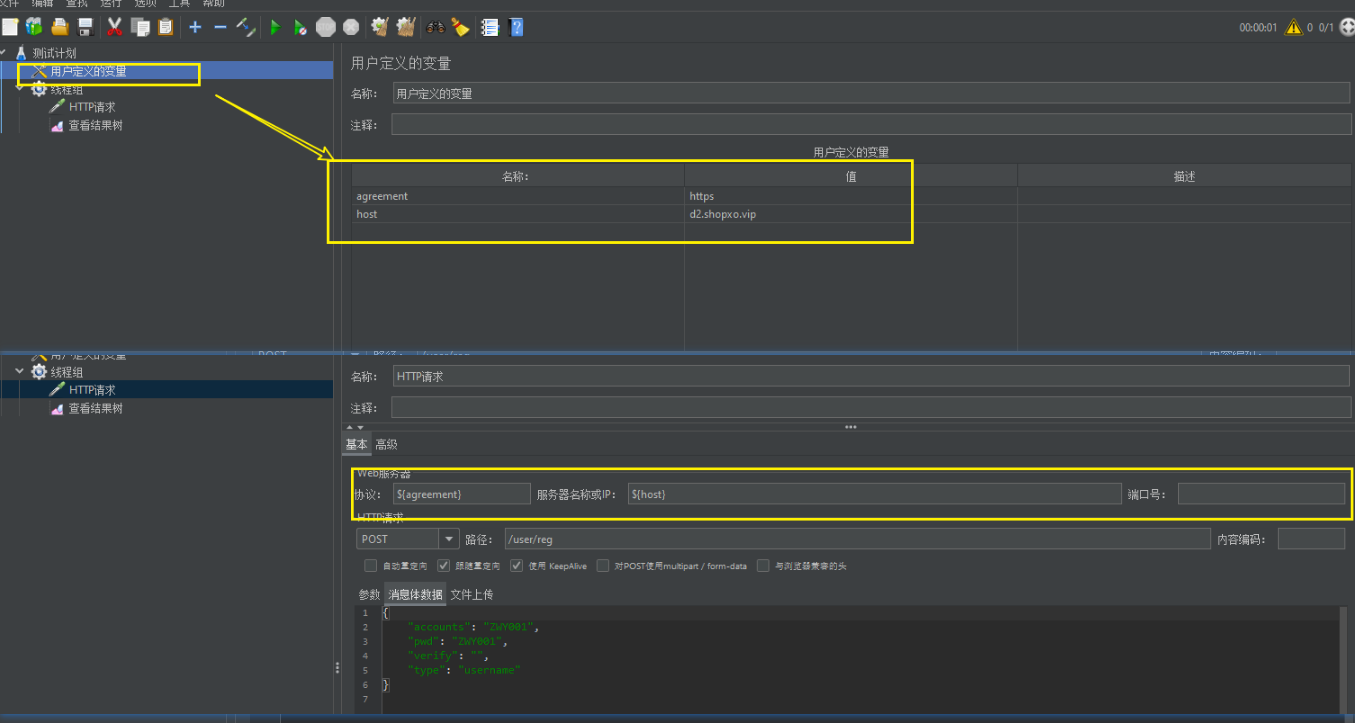

2 SPI时序协议

米联客的FPGA入门课程以标准的SPI控制器来说明,SPI的数据位宽是X1方式来讲解协议本身和标准控制器的设计,SS选通信号可以不使用,并且SPI控制器不支持仲裁功能。这种标准的协议作为入门学习是最佳选择,对于SPI的扩展应用,比如X4模式访问QSPI 接口的FLASH,我们可以在应用方案部分继续讨论。

SPI总线传输有4种不同的模式,不同的从设备可能在出厂是就是配置为某种模式,这是不能改变的,但我们的通信双方必须是工作在同一模式下。SPI总线的工作方式由时钟极性(Clock Polarity ,CPOL)与时钟相位(Clock Phase ,CPHA)来定义。我们可以通过CPOL(时钟极性)和CPHA(时钟相位)来控制我们主设备的通信模式。

CPOL(时钟极性):

决定在总线空闲时,同步时钟(SCLK)信号线上的电位是高电平还是低电平。当时钟极性为0时(CPOL=0),SCK信号线在空闲时为低电平;当时钟极性为1时(CPOL=1),SCK信号线在空闲时为高电平;

CPHA(时钟相位):

对于SPI主控制器决定了数据的更新时刻设计,对于SPI从控制器决定了数据的采样时刻。当时钟相位为0时(CPHA=0),在sclk的第1个跳变沿采样;当时钟相位为1时(CPHA=1),在sclk的第2个跳变沿采样;

以下我们给出CPOL和CPHA的共计4种情况。

SCLK:SPI的总线时钟

DATA:SPI的总线数据

Sendstrobe:SPI 控制器内部程序发送数据的触发信号

CapStroble:SPI 接收制器内部程序采样数据的触发信号

2.1 CPOL=0 CPHA=0

CPOL=0 CPHA=0默认SCLK为低电平,对于发送方,在对于第1个bit数据提前放到总线,建议提前0.5个SCK周期,对于接收方,数据在第1个SCLK跳变沿采样,并且容易满足时序约束。

2.2 CPOL=0 CPHA=1

CPOL=0 CPHA=1默认SCLK为低电平,对于发送方,在第1个SCLK的跳变沿更新(对于第一个bit数据可以提前放到总线)对于接收方,数据在第2个SCLK跳变沿采样,并且容易满足时序约束。

2.3 CPOL=1 CPHA=0

CPOL=1 CPHA=0默认SCLK为高电平,对于发送方,在对于第1个bit数据提前放到总线,建议提前0.5个SCK周期,对于接收方,数据在第1个SCLK跳变沿采样,并且容易满足时序约束。

2.4 CPOL=1 CPHA=1

CPOL=1 CPHA=1默认SCLK为高电平,对于发送方,在第1个SCLK的跳变沿更新(对于第一个bit数据可以提前放到总线)对于接收方,数据在第2个SCLK跳变沿采样,并且容易满足时序约束。

3 SPI驱动程序基本模块

一个基本的SPI Master驱动程序至少包含用于产生SCLK的时钟分频单元,发送数据并串移位模块、接收数据串并移位模块;

一个基本的SPI Slave驱动程序至少包含接收数据的串并移位模块,和发送数据的并串转换模块。

4 FPGA时序要求

基于FPGA的程序设计一定要时刻考虑程序能够满足时序要求,如下图所示。最佳的采样时刻在数据的中心位置,这样可以获得最大的Tsu(数据建立时间)和Thd(数据保持时间)。关于更多时序方面的设计要求可以参考"米联客FPGA代码时序设计专题篇"相关课程内容。

![[米联客-安路飞龙DR1-FPSOC] FPGA基础篇连载-13 SPI通信协议原理](https://img2024.cnblogs.com/blog/2504661/202407/2504661-20240729154926738-1309179775.png) SPI(串行外围设备接口)通信协议是一种高速、全双工、同步通信总线。它通过四根管脚实现控制和数据传输,广泛应用于EEPROM、Flash、RTC、ADC、DSP等设备,是一种重要的低速通讯协议。SPI协议具有高速、全双工、同步、主从式等特点,接口速度最高可达上百兆,因此不仅适用于低速设备,也能用于高速串行外设通信。例如,FPGA的配置FLASH可以支持100Mbps以上。SPI Master(主设备)通过发送时钟信号(SCLK)同步数据传输,决定通信速率。

SPI(串行外围设备接口)通信协议是一种高速、全双工、同步通信总线。它通过四根管脚实现控制和数据传输,广泛应用于EEPROM、Flash、RTC、ADC、DSP等设备,是一种重要的低速通讯协议。SPI协议具有高速、全双工、同步、主从式等特点,接口速度最高可达上百兆,因此不仅适用于低速设备,也能用于高速串行外设通信。例如,FPGA的配置FLASH可以支持100Mbps以上。SPI Master(主设备)通过发送时钟信号(SCLK)同步数据传输,决定通信速率。