FIFO:先进先出的缓存器。

常应用于带宽不同或者跨时钟域等数据传输情况。 相关参数:数据宽度,存储深度,将空标志位。空标志位。将满标志位,满标志位。读写时钟。其中将满信号与将空信号相较于真正的满信号与空信号都会提前一个时钟周期拉高。

FIFO generator配置注意事项:

Basic选项卡:Interface Type 选 Native,即传统接口。FIFO Implementation是指选择想要实现的是同步FIFO还是异步FIFO,以及使用什么资源实现FIFO,当选择Independent Clocks Block RAM,就是表示用块RAM实现异步FIFO。值得注意,FIFO是一种不包含地址的缓存方式。因此这里选择RAM或者ROM其实不影响对FIFO的应用。 Native Ports选项卡:Read Mode用于设置读FIFO时的读模式,一般选默认的 Standard FIFO. 在Data Port Parameters中设置读写端口的数据总线宽度与FIFO深度(Write Width,Write Depth,Read Width)。Reset Pin是复位信号,按需勾选。其余默认。 Status Flags选项卡:按需勾选将满和将空。其余默认。 Data Counts选项卡:计数FIFO中有效数据的个数,为更方便观察读写过程,可以将读写端口的计数都打开。Write/Read Data Count表示计数值总线位宽。一般选8bit就够用了。 Summary选项卡:显示当前配置。确认当前配置无误时直接点击OK. Generate Output Products窗口,直接点击Generate。

.veo例化模版:

fifo16to8 your_instance_name (.rst(rst), // input wire rst.wr_clk(wr_clk), // input wire wr_clk.rd_clk(rd_clk), // input wire rd_clk.din(din), // input wire [15 : 0] din.wr_en(wr_en), // input wire wr_en.rd_en(rd_en), // input wire rd_en.dout(dout), // output wire [7 : 0] dout.full(full), // output wire full.empty(empty), // output wire empty.rd_data_count(rd_data_count), // output wire [10 : 0] rd_data_count.wr_rst_busy(wr_rst_busy), // output wire wr_rst_busy.rd_rst_busy(rd_rst_busy) // output wire rd_rst_busy );

基础的模块例化之fifo_rd:

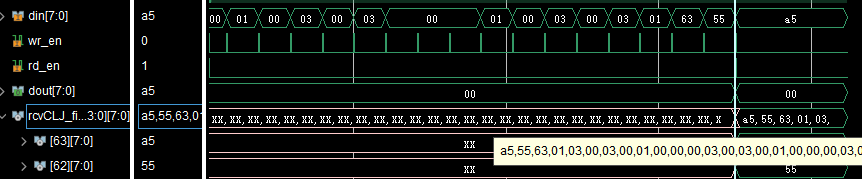

功能:设定rd_cnt[7:0],以便取数存用。`timescale 1ns / 1nsmodule fifo_rd(input clk , // 时钟信号input rst_n , // 复位信号input CLJwhole_en , //收好一组指令留待处理。output reg [7:0] rd_cnt , // 向外读64个。output reg fifo_rd_en // FIFO读使能 );reg [3:0] state;//读出FIFO的数据always @(posedge clk ) beginif(~rst_n) beginfifo_rd_en <= 1'b0;rd_cnt <= 4'd0;state <= 4'd0;endelse begincase(state)2'd0: begin if(CLJwhole_en) begin //如果检测到FIFO被写满rd_cnt <= 8'd1; //给出第一个rd_cnt.fifo_rd_en <= 1'b1; state <= 2'd1; //开始取数。得到64个8比特数。endelsestate <= state;end 2'd1: begin //接下来在rd_cnt从1数到64的过程中FIFO就会每个时钟拍打出一个[7:0] dout。if(rd_cnt == 8'd65) begin //rd_cnt数到第65开始关闭rd_en。等待下一个whole_en。fifo_rd_en <= 1'b0; //关闭读使能rd_cnt <= 8'd0;state <= 2'd2; //开始读操作endelserd_cnt <= rd_cnt + 4'd1;end2'd2: beginrd_cnt <= 8'd0;fifo_rd_en <= 1'b0; //关闭读使能state <= 4'd0;end default : state <= 2'd0;endcaseendendendmodule

fifo_rd功能优化之“存满读空预处理”

(留待编辑)

generate 变量i取数

wire [7:0] rcvCLJ_fifo [63:0]; genvar i; generate for(i=0; i<=63; i=i+1) begin: dataassign rcvCLJ_fifo[i] = (rd_cnt == i+2) ? fifo_dout : rcvCLJ_fifo[i]; end endgenerate

为什么从i+2开始算?

(留待编辑)