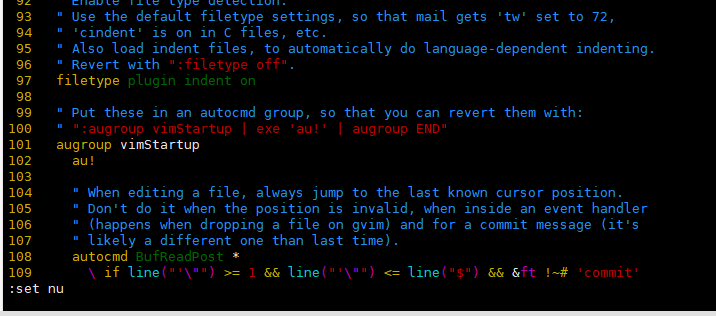

这个题目的意思是输入是单bit脉冲,然后当8个周期的脉冲序列符合给定的参数值则match输出1;

因此肯定需要一共8位的寄存器存储总共8个a的输入脉冲

此外由于是从左向右匹配,因此每个周期输入的a要从寄存器最低位输入,从右向左移位(temp_a<={temp_a[6:0],a};),这样才是输入满足条件的01110001

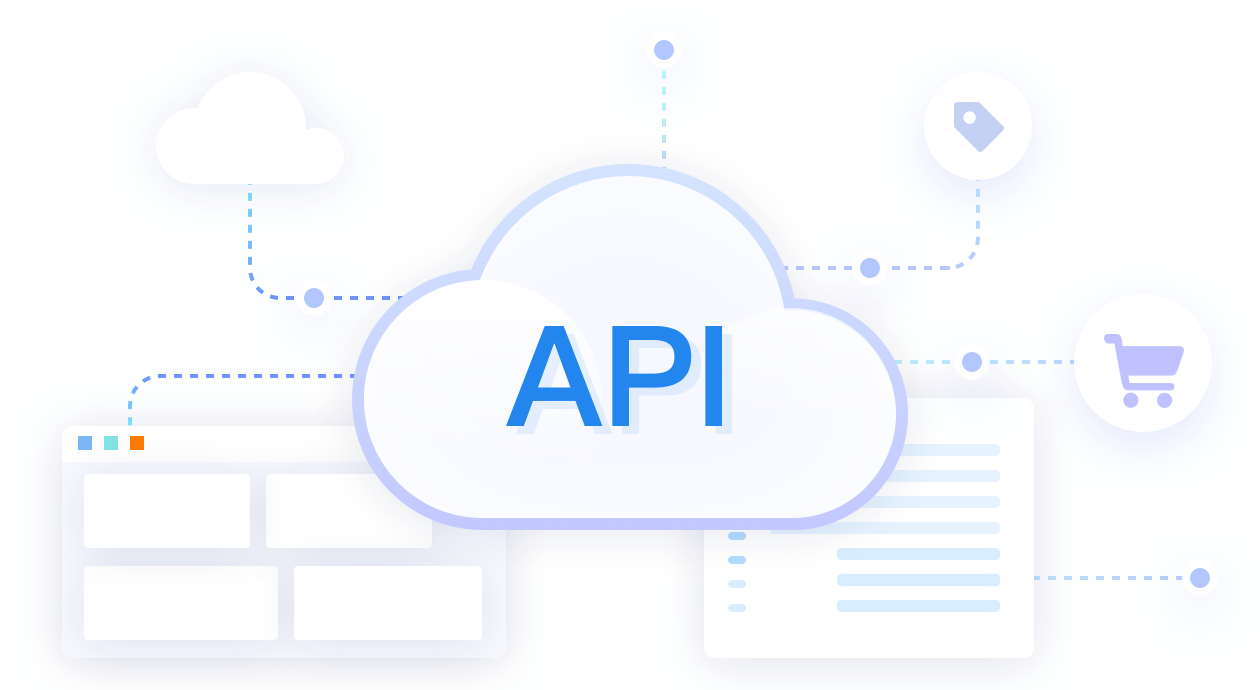

`timescale 1ns/1ns

module sequence_detect(

input clk,

input rst_n,

input a,

output reg match

);

reg [7:0] temp_a;

always @(posedge clk,negedge rst_n)begin

if(!rst_n)

temp_a<=0;

else

temp_a<={temp_a[6:0],a};

end

always @(posedge clk,negedge rst_n)begin

if(!rst_n)begin

match<=1'b0;

end

else if(temp_a==8'b01110001)begin

match<=1'b1;

end

else

match<=1'b0;

end

endmodule

最后的写法也可以用()?:来写,第一次错误是因为没有写

else

match<=1'b0;

以后要注意

![[JS] ArrayBuffer、DataView和TypedArray](https://fox-blog-image-1312870245.cos.ap-guangzhou.myqcloud.com/202408291546852.png)