差分输入时钟缓冲器(IBUFDS)

点击查看代码

// IBUFDS: Differential Input Buffer// 7 Series// Xilinx HDL Language Template, version 2024.1IBUFDS #(.DIFF_TERM("FALSE"), // Differential Termination.IBUF_LOW_PWR("TRUE"), // Low power="TRUE", Highest performance="FALSE".IOSTANDARD("DEFAULT") // Specify the input I/O standard) IBUFDS_inst (.O(O), // Buffer output.I(I), // Diff_p buffer input (connect directly to top-level port).IB(IB) // Diff_n buffer input (connect directly to top-level port));// End of IBUFDS_inst instantiation

差分输出时钟缓冲器(OBUFDS)

点击查看代码

// OBUFDS: Differential Output Buffer// 7 Series// Xilinx HDL Language Template, version 2024.1OBUFDS #(.IOSTANDARD("DEFAULT"), // Specify the output I/O standard.SLEW("SLOW") // Specify the output slew rate) OBUFDS_inst (.O(O), // Diff_p output (connect directly to top-level port).OB(OB), // Diff_n output (connect directly to top-level port).I(I) // Buffer input);// End of OBUFDS_inst instantiation

三态差分输入输出(IOBUFDS)

点击查看代码

// IOBUFDS: Differential Bi-directional Buffer// 7 Series// Xilinx HDL Language Template, version 2024.1IOBUFDS #(.DIFF_TERM("FALSE"), // Differential Termination ("TRUE"/"FALSE").IBUF_LOW_PWR("TRUE"), // Low Power - "TRUE", High Performance = "FALSE".IOSTANDARD("BLVDS_25"), // Specify the I/O standard.SLEW("SLOW") // Specify the output slew rate) IOBUFDS_inst (.O(O), // Buffer output.IO(IO), // Diff_p inout (connect directly to top-level port).IOB(IOB), // Diff_n inout (connect directly to top-level port).I(I), // Buffer input.T(T) // 3-state enable input, high=input, low=output);// End of IOBUFDS_inst instantiation

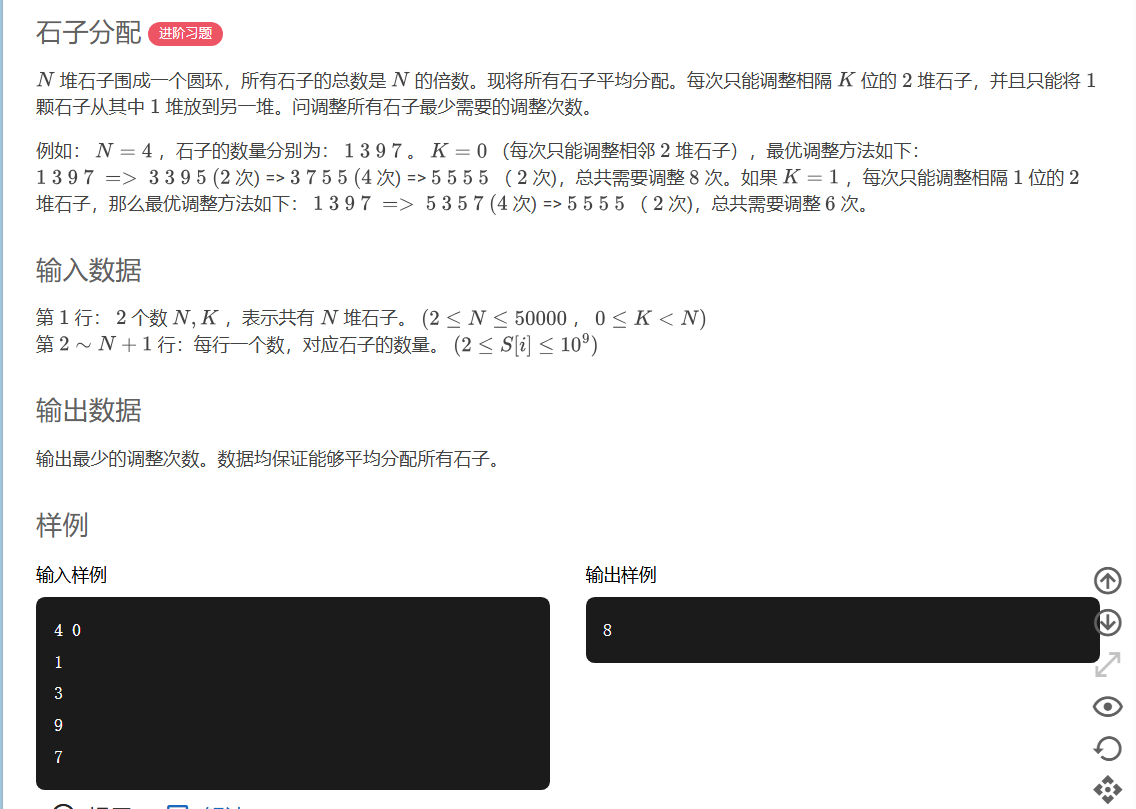

以下是我使用的118评估版的IO

补充电平特性

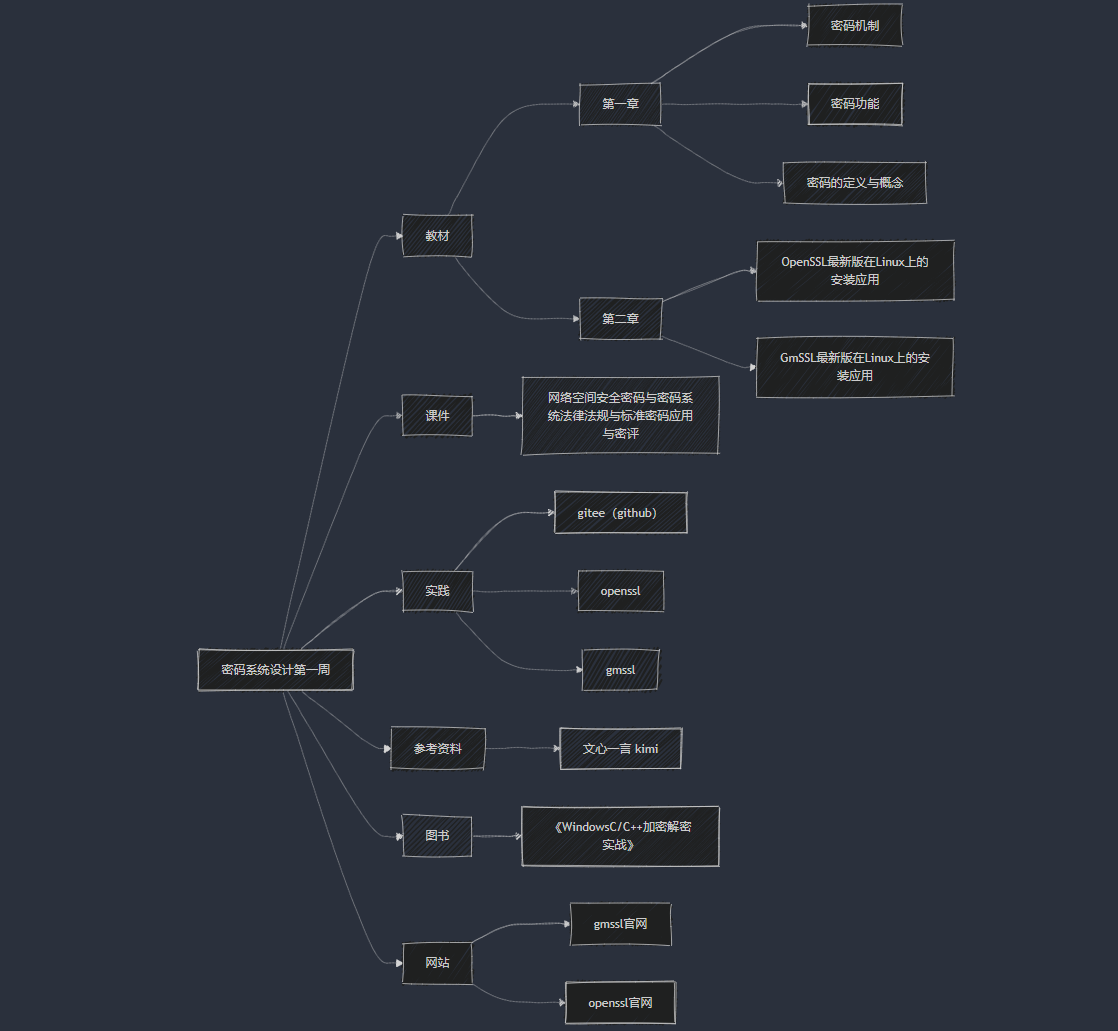

参考

7 Series FPGAs SelectIO Resources User Guide (UG471)

7 Series FPGA and Zynq 7000 SoC Libraries Guide(ug953)

Zynq UltraScale+ RFSoC Data Sheet:DC and AC Switching Characteristics(DS926)