一、FIFO概述

1、FIFO的定义

FIFO是英文First-In-First-Out的缩写,是一种先入先出的数据缓冲器,与一般的存储器的区别在于没有地址线, 使用起来简单,缺点是只能顺序读写数据,其数据地址由内部读写指针自动加1完成,不能像普通存储器那样可以由地址线决定读取或写入某个指定的地址。

2、FIFO的作用

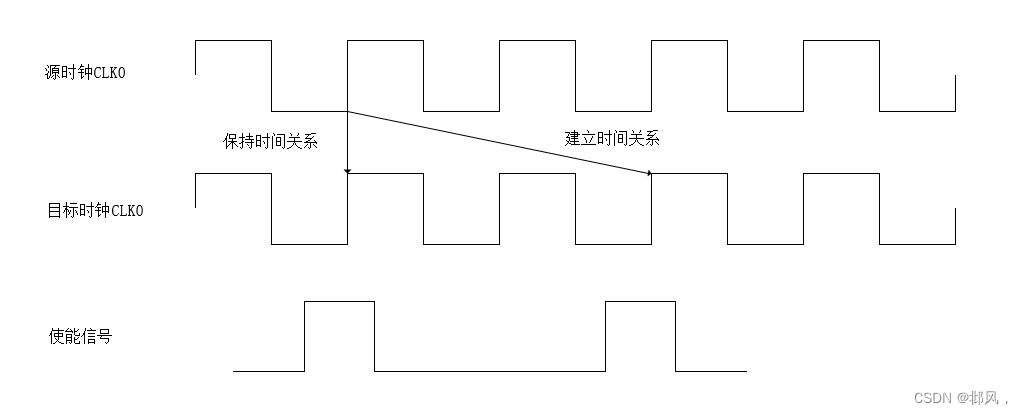

(1)跨时钟域的数据传输

(2)对不同宽度的数据进行位宽转换

(3)数据缓存

3、FIFO的分类

根据FIFO工作的时钟域的不同,可以将FIFO分为以下两类

(1)同步FIFO:读时钟和写时钟为同一个时钟,在时钟沿来临时同时发生读写操作。常用于对不同宽度的数据进行位宽转换

(2)异步FIFO:读写时钟不一致,读写操作是互相独立的。常用于跨时钟域的数据传输

4、FIFO的一些重要参数

(1)FIFO宽度:指的是FIFO读写的数据位,就像MCU有8位和16位,ARM 32位等等,FIFO的宽度在单片成品IC中是固定的,也有可选择的,如果用FPGA自己实现一个FIFO,其数据位,也就是宽度是可以自己定义的。

(2)FIFO深度:指的是FIFO可以存储多少个N位的数据(假设FIFO宽度为N)。

(3)满标志(full):FIFO已满或将要满时由FIFO送出的状态信号,以阻止FIFO的写操作,避免数据溢出。

(4)空标志(empty):FIFO已空或将要空时由FIFO送出的状态信号,以阻止FIFO的读操作,避免数据读空。

(5)读时钟:读操作的时钟,在每个时钟沿来临时读数据。

(6)写时钟:写操作的时钟,在每个时钟沿来临时写数据。

(7)读指针:指向下一个要读出的地址,读完后自动加1。

(8)写指针:指向下一个要写入的地址,写完后自动加1。

读写指针其实就是读写的地址,只不过这个地址不能任意选择,而是连续的。

二、FIFO IP核

xilinx官方提供了FIFO Generator IP核来帮助我们快速实现FIFO。

1、支持的接口

FIFO Generator这个IP核支持两种接口:Native(原始接口)和AXI(AXI接口)。

1.1 Native接口FIFO

Native接口的FIFO可以被定制成通过BRAM或DRAM或(一些系类有)片上固定的FIFO资源来实现。支持 Standard 和 First Word Fall Through 两种操作模式。

1.2 AXI接口FIFO

AXI接口的FIFO是由Native接口的FIFO发展过来的,它能支持3中存储器映射的接口:AXI4,AXI3和AXI4-Lite。除了Native接口FIFO所具有的基本功能(毕竟是从Native升级过来的),带有AXI接口的FIFO还能用于AXI系统总线和点对点高速应用中。

关于AXI的部分会在AMBA的文章中有深入讲解,这里只要知道FIFO这个IP核可以支持AXI接口就行(其实xilinx中非常多的IP核都能支持AXI接口,这也是其设计时的一个特点与优势)。本文接下来讨论的都是Native接口的情况。

2、Native FIFO的接口信号

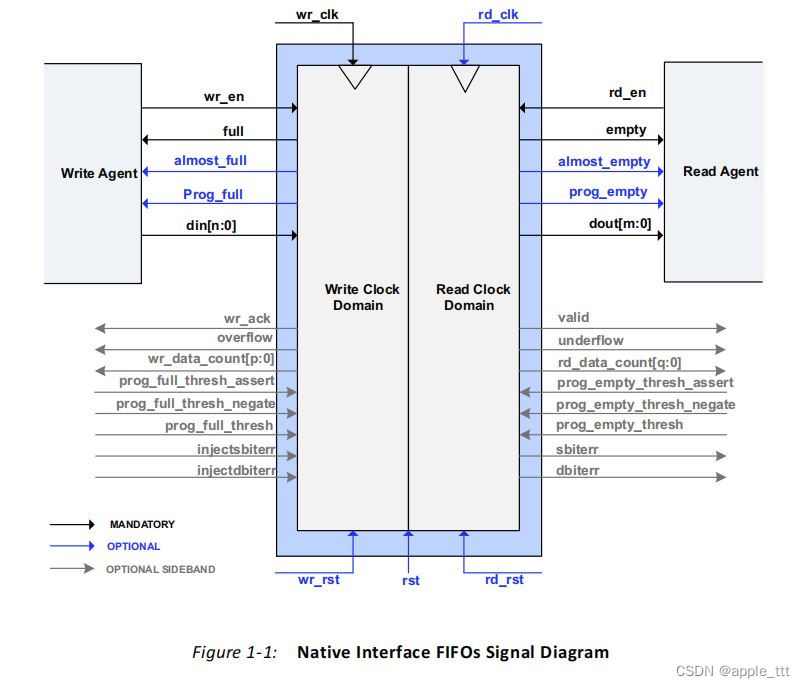

下图给出了一个具有独立读写时钟的FIFO的模块示意图(标准的接口和可选接口都展现了)

这个图一看就挺恐怖的,没办法,学习嘛,逃不过的,不过饭要一口一口吃,信号要一个一个看,我们先来简单分个类:

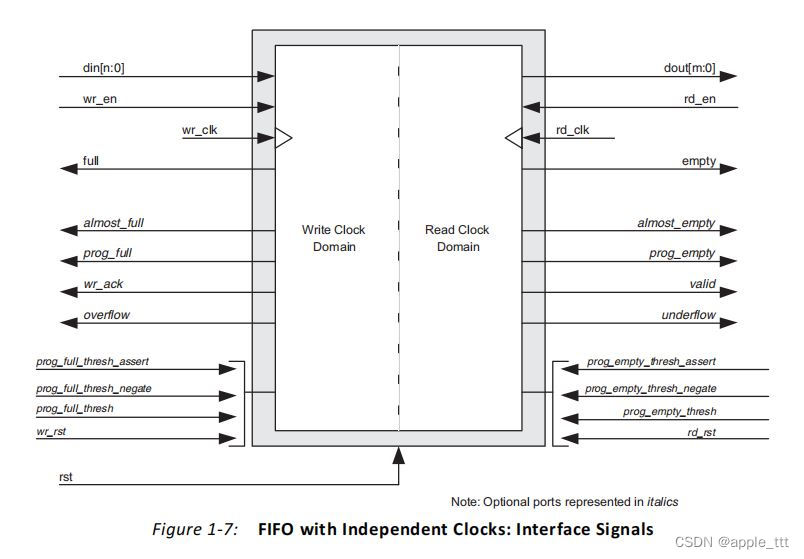

2.1 接口信号:异步FIFO(FIFOs With Independent Clocks)

(1)特殊信号

先来看2个特殊的信号:

| 名称 | 方向 | 描述 |

| rst | 输入 | Reset复位:一个异步复位信号,能初始化所有的内部指针和输出寄存器。 对于UltraScale系类的嵌入式FIFO不适用。 |

| sleep | 输入 | 动态功率门控:如果sleep有效,FIFO进入省电模式(不懂,低功耗叭) 不重要了,反正它只存在于UltraScale系类的嵌入式FIFO里。 |

(2)写接口信号

我们来看一下和写操作相关的异步FIFO接口信号,这些信号中有些是标准接口下的(就是标配,肯定有的),还有一部分是可选的(附加功能,得加钱(bushi))。

| 名称 | 方向 | 描述 |

| Required(就是我们说的标准接口,也是需要重点掌握的部分) | ||

| wr_clk | 输入 | 写时钟:所有写时钟域下的信号都和这个信号同步 |

| din[n:0] | 输入 | 数据输入:写FIFO时候的数据总线 |

| wr_en | 输入 | 写使能信号:如果FIFO没满,这个信号生效就会使得数据(din,写数据总线上的)写进FIFO |

| full | 输出 | 满标志:这个信号生效时说明FIFO满了,在FIFO满的时候,写操作是直接忽视的(反正不能再让你写进去了),所以FIFO满的时候,写操作不会对FIFO里面的数据产生破坏(外面的数据:我谢谢你啊)。 |

| Optional(可选接口信号,最后几个看看有个印象进行了,又臭又长的,看着就学不会) | ||

| wr_rst | 输入 | 写复位:同步于写时钟。生效时,初始化写时钟域下所有的指针和标志信号 |

| almost_full | 输出 | 将满信号:生效时,说明FIFO只能最多再允许一个写操作啦 |

| prog_full | 输出 | 可编程满信号:可以和上面一个将满做个对比,这个信号的存在允许我们设置一个阈值来判断FIFO还有多少空间,它在FIFO剩余空间大于等于生效阈值时生效,小于等于失效阈值时失效。 |

| wr_data_count[d:0] | 输出 | 写数据计数:更高级了,这条总线直接告诉我们FIFO里写进了多少字,这家伙保证绝对不少报(多报问题还不大,顶多我不写了,少报数据还在写,直接寄了),这样就保证了我们永远不会溢出(overflow)。此行为的例外情况是,当一个写操作发生在wr_clk/ clk的上升缘时,该写操作将只反映在下一个上升时钟边缘的wr_data_count上。如果D小于log2(FIFO depth)-1,总线通过删除最不重要的位而被截断。 注,这条总线在UltraScale系类,通过一个common clock Block RAM-based 实现的(还要用上了Asymmetric Port Width端口)FIFO里也有效。 |

| wr_ack | 输出 | 写确认:这个信号表示上一个时钟周期的写请求成功。 |

| overflow | 输出 | 溢出信号:这个信号表示上一个时钟周期的写请求被拒绝,因为FIFO已经满了。FIFO溢出不会破坏已经在FIFO里的内容 |

| prog_full_thresh | 输入 | 可编程满阈值:这个信号用来输入阈值,可动态调控 |

| prog_full_thresh_assert | 输入 | 可编程阈值生效信号:这个信号定义了可编程满的上阈值什么时候生效,可动态设置 |

| prog_full_thresh_negate | 输入 | 可编程阈值失效信号:这个信号定义了可编程满的下阈值什么时候生效,可动态设置 |

| injectsbiterr | 输入 | 使用ECC的时候插入(inject,注射?)一位错误 |

| injectdbiterr | 输入 | 使用ECC的时候插入(inject,注射?)两位错误 |

| wr_rst_busy | 输出 | 生效时表示整个写时钟域处于复位状态 仅存在于UltraScale系类的嵌入式FIFO里 |

(3)读接口信号

有写就有读,很多地方都和写接口有着异曲同工之妙。

| 名称 | 方向 | 描述 |

| Required(就是我们说的标准接口,也是需要重点掌握的部分) | ||

| rd_rst | 输入 | 读复位信号:同步于读时钟,生效时,初始化读时钟域内所有的内部指针,标志信号,输出寄存器 |

| rd_clk | 输入 | 读时钟:所有读时钟域下的信号都同步于这个信号 |

| dout[m:0] | 输出 | 数据输出:读FIFO时输出数据总线被驱动 |

| rd_en | 输入 | 读使能:如果FIFO不是空的,这个信号生效的时候会使得数据从FIFO中被读出(通过dout) |

| empty | 输出 | 空标志:生效时,说明FIFO已经空了,当FIFO空的时候,读请求会被忽视, |

| Optional(可选接口信号,最后几个看看有个印象进行了,又臭又长的,看着就学不会) | ||

| almost_empty | 输出 | 将空信号:生效时表示FIFO就快要空了,只剩下最后一个数据可以读 |

| prog_empty | 输出 | 可编程空:当FIFO中的数据数小于或等于生效阈值时,就会生效该信号。当FIFO中的数据数超过失效阈值时,它即被取消生效。 |

| rd_data_count [c:0] | 输出 | 读数据计数:这个总线告诉我们在FIFO中还有多少个数据可读,注,这条总线在UltraScale系类,通过一个common clock Block RAM-based 实现的(还要用上了Asymmetric Port Width端口)FIFO里也有效。 |

| vaild | 输出 | 有效信号:生效时表示输出总线上的数据有效 |

| underflow | 输出 | 下溢出:由于FIFO是空的,上一个时钟周期的读操作被拒绝 |

| prog_empty_thresh | 输入 | 可编程空阈值:此信号用于输入可编程空(prog_empty)标志的确认和取消。 |

| prog_empty_thresh_assert | 输入 | 可编程空阈值生效:此信号用于设置可编程空标志的下阈值 |

| prog_empty_thresh_negate | 输入 | 可编程空阈值失效:此信号用于设置可编程空标志的上阈值 |

| sbiterr | 输出 | 单位错误:表示ECC解码器检测到并修复了块RAM或内置的FIFO宏上的单位错误。 |

| dbiterr | 输出 | 双位错误:表示ECC解码器在块RAM或内置的FIFO宏上检测到双位错误,并且FIFO核心中的数据已损坏。 |

| rd_rst_busy | 输出 | 当生效时,该信号表示读取域处于复位状态。 仅存在于UltraScale系类的嵌入式FIFO里 |

2.2 接口信号:同步FIFO(Interface Signals: FIFOs with Common Clock)

看完了异步FIFO的接口信号,我们来看一看同步FIFO的接口信号,在理解了上一部分的基础上,这部分的内容就简单很多了。

对于同步FIFO来说,所有的信号(异步复位信号除外)都同步于时钟,对于用DRAM或BRAM构成的FIFO来说,用户可以选择使用同步复位还是异步复位。

| 名称 | 方向 | 描述 |

| Required(就是我们说的标准接口,也是需要重点掌握的部分) | ||

| rst | 输入 | 一个异步复位信号,能初始化所有的内部指针和输出寄存器。对于UltraScale系类的嵌入式FIFO不适用。 |

| srst | 输入 | 一个同步复位信号:能初始化所有的内部指针和输出寄存器。 |

| clk | 输入 | 时钟:读写时钟域的所有信号都同步于它。 |

| din[n:0] | 输入 | 数据输入:写入FIFO时使用的输入数据总线 |

| wr_en | 输入 | 写使能:如果FIFO未满,则生效此信号会导致数据(在din上)被写入FIFO。 |

| full | 输出 | 满标志:生效时,该信号表示FIFO已满。当FIFO满时,写入请求被忽略,在FIFO满时启动写入不会对FIFO的内容造成破坏。 |

| dout[m:0] | 输出 | 数据输出:读取FIFO时驱动的输出数据总线。 |

| rd_en | 输入 | 读使能:如果FIFO不为空,生效此信号会导致从FIFO读取数据(dout上)。 |

| empty | 输出 | 空标志:在生效时,此信号表示FIFO为空。当FIFO为空时,读取请求被忽略,在空时启动读取对FIFO没有破坏性。 |

| Optional(可选接口信号) | ||

| data_count [c:0] | 输出 | 数据计数:此总线表示在FIFO中存储的单词数。如果C小于log2(FIFO深度)-1,总线通过删除最小显著位来截断。 |

| almost_full | 输出 | 将满:生效时,此信号表示在FIFO满之前只能执行一次写入。 |

| prog_full | 输出 | 可编程满:当FIFO中的数据数大于或等于生效阈值时,即会生效该信号。当FIFO中的单词数小于失效阈值时,则取消失效。 |

| wr_ack | 输出 | 写确认:此信号表示前一个时钟周期中的写入请求(wr_en)已成功 |

| overflow | 输出 | 溢出:此信号表示在前一个时钟周期中的写入请求(wr_en)被拒绝,因为FIFO已满。溢出FIFO对FIFO没有破坏性。 |

| prog_full_thresh | 输入 | 可编程满阈值:此信号用于设置可编程满(PROG_FULL)标志的阈值。 |

| prog_full_thresh_assert | 输入 | 可编程满阈值生效:此信号用于设置可编程全标志的上阈值,它定义了信号的生效时间。 |

| prog_full_thresh_negate | 输入 | 可编程满阈值生效:此信号用于设置可编程满标志的较低阈值 |

| almost_empty | 输出 | 将空的标志:当生效时,该信号表示FIFO几乎为空的,并且有一个字保留在FIFO中。 |

| prog_empty | 输出 | 可编程空:该信号在FIFO中的单词数小于或等于可编程的阈值后被生效。当FIFO中的单词数超过可编程阈值时,它即被失效。 |

| valid | 输出 | 有效:此信号表示在输出总线(dout)上有有效的数据可用。 |

| underflow | 输出 | 下溢出:表示前一个时钟周期中的读取请求被拒绝(rd_en)。注入FIFO对FIFO没有破坏性。 |

| prog_empty_thresh | 输入 | 可编程空阈值:此信号用于设置可编程空(prog_empty)标志的生效和失效的阈值 |

| prog_empty_thresh_assert | 输入 | 可编程空阈值生效:此信号用于设置可编程空标志的下阈值 |

| prog_empty_thresh_negate | 输入 | 可编程空阈值失效:此信号用于设置可编程空标志的上阈值 |

| sbiterr | 输出 | 单位错误:表示ECC解码器检测到并修复了一个单位错误 |

| dbiterr | 输出 | 双位错误:表示ECC解码器检测到一个双位错误,并且FIFO IP中的数据已损坏。 |

| injectsbiterr | 输入 | 如果使用了ECC特性,则会输入单个比特错误。 |

| injectdbiterr | 输入 | 如果使用了ECC特性,则会出现双位错误。有关详细信息, |

| sleep | 输入 | 动态关机节能。如果休眠状态处于激活状态,则FIFO将处于省电模式。注:仅适用于内置的UltraScale设备的FIFOs |

| wr_rst_busy | 输出 | 当生效时,该信号表示写入域处于重置状态。 仅适用于UltraScale设备内置的FIFOs,以及具有同步重置的公共时钟块RAM/分布式RAM/移位寄存器FIFOs。 |

| rd_rst_busy | 输出 | 当生效时,该信号表示读取域处于重置状态。仅适用于UltraScale设备内置的FIFOs,以及具有同步重置的公共时钟块RAM/分布式RAM/移位寄存器FIFOs。 |

三、FIFO操作

1、写操作

当写使能生效,并且FIFO没有满的时候,输入总线(din)上的数据写入FIFO,写确认信号生效。如果FIFO被连续写入而没有被读取,那么它被写满。只有当FIFO未满时,写操作才会成功。当FIFO已满,再启动写入时,将忽略请求,生效溢出标志,并且FIFO的状态没有变化(FIFO溢出是非破坏性的)。

接下来我们通过一个例子来看看FIFO的写操作:

我们一步一步来看:

(1)图中①处:wr_en写使能信号低,未开始写操作.

(2)图中②处:wr_en拉高,开始写操作,此时的full为低,说明FIFO没有满,写操作有效。

(3)图中③处:首先发现wr_ack有效,说明上一个时钟周期的D1成功写入,本周期和上一周期一样正常写数据进FIFO。

(4)图中④处:基本同上一周期,但是发现almost_full信号拉高,说明FIFO将满了。

(5)图中⑤处:full拉高了,FIFO满,写数据失败,但是对FIFO内的数据没有影响。

(6)图中⑥处:wr_ack拉低,证明了上一个周期写失败,此时FIFO依然满。

(7)图中⑦处:同上

(8)图中⑧处:full拉低,almost_full拉高,说明FIFO有了一个写入的空间,此时写入数据D12

(9)图中⑨处:ack表示D12成功写入,从full看出FIFO此时可以正常写入数据。

2、读操作

当读使能有效,并且FIFO不空的时候,数据通过输出数据总线(dout)从FIFO中被读出,valid(有效)信号生效。如果FIFO被连续读取而没有被写入,则FIFO将清空。当FIFO不为空时,读取操作将会成功。当FIFO为空并请求读取时,将忽略读取操作,生效下溢出标志,并且FIFO的状态没有变化(下溢出FIFO是非破坏性的)。

2.1 Common Clock Note(同步FIFO一些值得注意的地方)

当FIFO空(empty生效)的时候,当同时进行写和读操作时,则接受写操作,忽略读操作。在下一个时钟周期中,empty失效,underflow生效。

2.2 读操作模式

FIFO Generator IP核支持两种读模式,标准读模式(standard read operation)和前显模式(FWFT,first-word fall-through)读操作。

标准模式也即是默认模式,发出一个指令,在一定的时间延迟后才会读到第一个数据。而前显模式在请求它的同一周期中提供用户数据。但是不是所有的FIFO都支持前显模式的:

看起来前显模式似乎更加好用,但是一般来说还是推荐使用标准模式,前显模式的特殊性会使得很多地方违反我们的常规认知。

(1)标准模式读操作

和读操作的原理其实差别不大,这里不做详细解读了,读者可根据波形自行分析。

(2)前显模式读操作

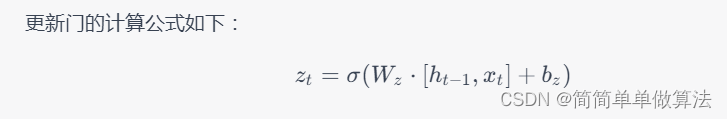

最初,FIFO不是空的,下一个可用的数据被放在输出总线(dout)上,有效信号(vaild)生效。当您生效rd_en时,在rd_clk的下一个上升时钟沿,将下一个数据字放到dout上。在最后一个数据字放在dout上后,一个额外的读取请求导致dout上的数据无效,如失效vaild和生效empty所示。任何进一步从FIFO读取的尝试都会导致下溢出状态。

与标准读取模式不同,第一个单词通过的空标志是在从FIFO读取最后一个数据之后生效的。当empty生效时,将失效vaild。在标准读取模式中,当empty生效时,vaild还将保持一个周期的有效。FWFT特性还增加了FIFO的有效读深度。

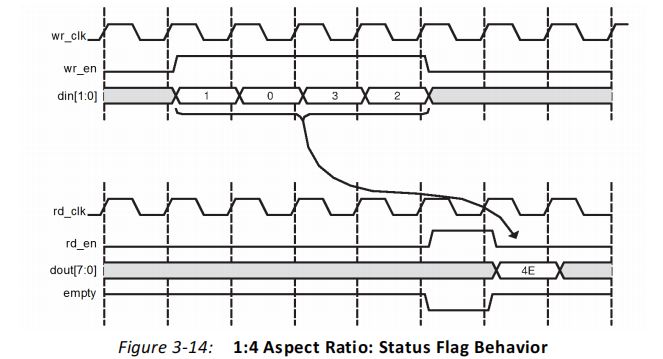

四、非对称读写位宽

1、写位宽<读位宽

接下来,我们来看一下输入信号,输出信号和握手信号之间的关系:

简单说就是empty(空信号)只有当FIFO内数据足以满足一次读才会失效。 (不难理解,空是要指示读的,都不满一个数据(这里就是8位)就读肯定是不行的)。

2、写位宽>读位宽

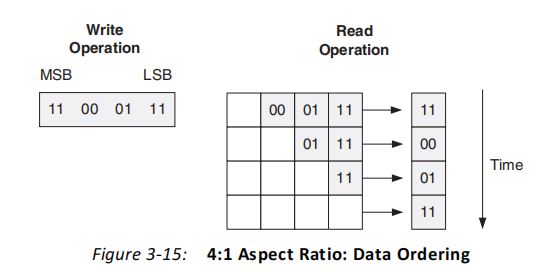

下图显示了一个高宽比为4:1的FIFO(写入宽度为8,读取宽度为2)。在本例中,执行单个写操作,之后执行四个读操作。写操作是11_00_01_11。当执行一个读取操作时,将数据被从左到右接收(MSB到LSB)。如图所示,第一次读取的结果为11,其次是00、01,然后是11。

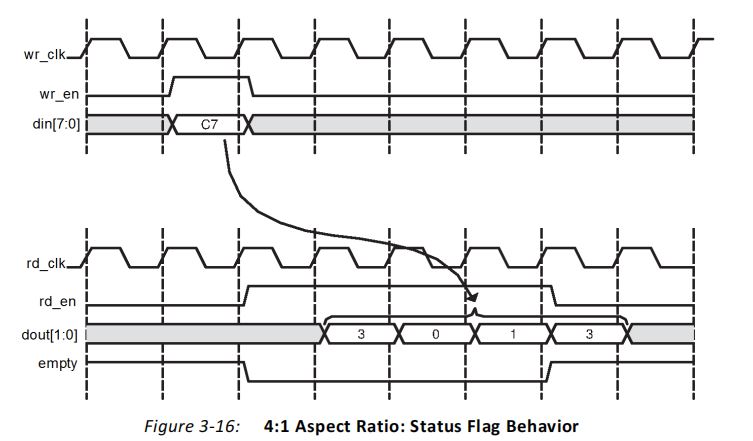

接下来,我们来看一下输入信号,输出信号和握手信号之间的关系:

这里就是empty信号还是要满足有能够读的数据就不为空,这里是2位不是8位。

其实都是符合我们常规认知的,很容易想通。

五、总结

本文对于xilinx的FIFO Generator IP核进行了一个简单的介绍,解释了IP核中各个类型信号的具体功能。介绍了FIFO的读写操作,其中读操作又可以分成2种模式,推荐使用标准模式,最后介绍了FIFO的非对称读写位宽。关于这个IP核的具体使用和示例操作,将在后续的文章中带来。

![【Android】 No matching variant of com.android.tools.build:gradle:[版本号] was found](https://img-blog.csdnimg.cn/18061ff5584843479c428b044d21a99c.png#pic)