synchronous & asynchronous

在静态时序分析中,有一个很重要的概念是同步和异步

如果 launch clock 与 capture clock 有固定的相位差,那就是同步时序

如果两者没有固定的相位差,那就是异步时序

一般情况下,STA 只检查同步时序,不用检查异步时序

同步时序又分为以下几种情况:

a) launch 和 capture 的周期相同:

这种情况最简单,launch clock 发出的数据被一个周期后的capture clock 锁存,setup check 和 hold check 如下图:

b) launch 和 capture 的周期不同,且 launch 周期小于 capture 周期

这是典型的快时钟域到慢时钟域,此时有多个上升沿发出的数据可能被同一个capture 上升沿采集到,如下图:

那么在这种情况下,STA 工具会选择哪些边沿来做时序分析呢?

首先,launch 的周期是10ns,capture 的周期是 15ns,可以看出每隔30ns形成一个循环,所以只需要考虑30ns 以内的情况,后面的都是无限重复

工具会从这 30ns 内找出最苛刻的时钟边沿来做时序分析,对于 setup 来说,从 10ns 到 15 ns 这组的时序是最严格的,所以工具会选择这组来做 setup check; 而对于 hold, 从 0ns 到 0ns 这组的时序最严格,所以选择这组做 hold check,保证从 0ns 发出的数据不会干扰到capture edge 在 0ns 采集上一组数据

c) launch 和 capture 的周期不同,且 launch 的周期大于 capture 的周期

这是慢时钟域到快时钟域,那么此时又该选择哪些边沿来做时序分析?

首先,launch 的周期是 15, capture 的周期是10, 两者的最小共同周期就是 30ns, 而在 30ns 内,对于 setup 最严格的时序是从 15ns 到 20ns 这一组,所以工具会选择这组做 setup check,而对于hold, 最严格的依然是从 0ns 到 0ns, 所以选择这组做 hold check

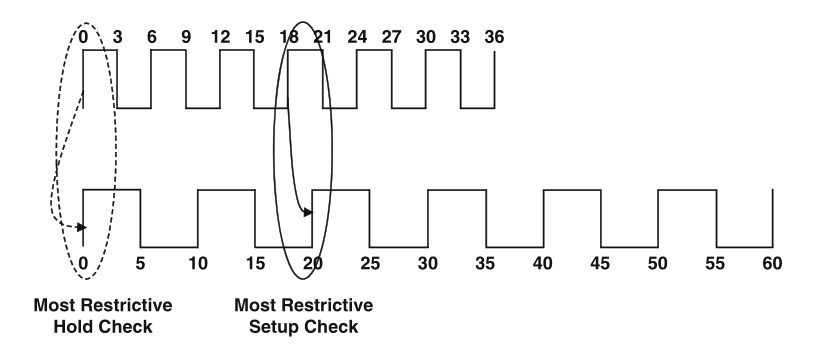

总之,对于 launch 和 capture 周期不同的同步时序电路,只要先找出两者的最小共同周期,然后在这个周期内找到最苛刻的那组时钟沿,就可以快速分析出用来做 setup check 和 hold check 的时钟沿;比如下面这个例子,launch clock 的周期是6ns,capture 的周期是10ns,那么两者的最小周期就是 30ns,在这 30ns 内,最严格的 setup 是从 18ns 到 20ns,而最严格的 hold 依然是从 0ns 到 0ns 。

对于异步时序来说,由于无法确定launch 和 capture 的最小共同周期,各个时钟边沿之间也没有固定的时间差,所以是无法做时序分析的,对于跨时钟域的异步电路,需要在设计阶段就做好防护,采用多级 register、异步 FIFO 等方法确保数据的准确传输。