双稳态触发器

双稳态触发器是一种具有记忆功能的逻辑单元电路,它能储存一位二进制码。

特点

- 有两个稳定状态“0”态和“1”态;

- 能根据输入信号将触发器置成“0”或“1”态;

- 输入信号消失后,被置成的“0”或“1”态能保存下来,即具有记忆功能。

RS触发器

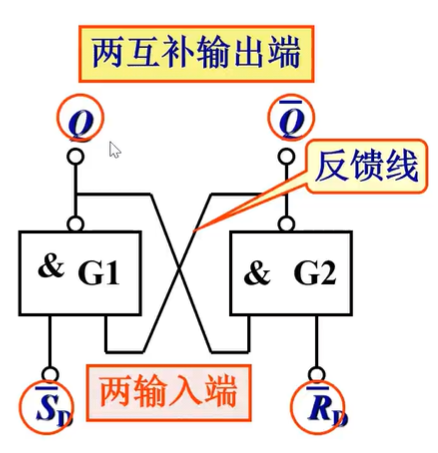

基本RS触发器

输入低电平有效

正常情况下,两输出端的状态保持相反。通常以Q端的逻辑电平表示触发器的状态,即\(Q=1, \overline{Q}=0\),时,称为“1”态。反之为“0”态。

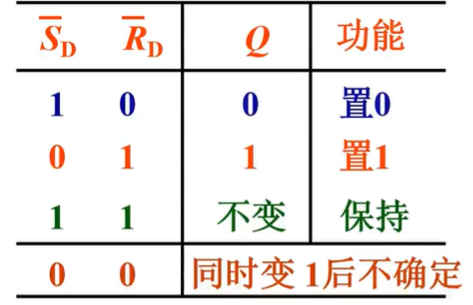

基本R-S触发器状态表

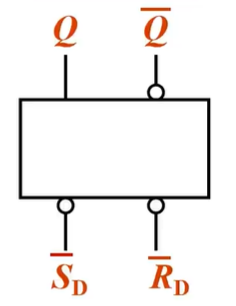

逻辑符号表

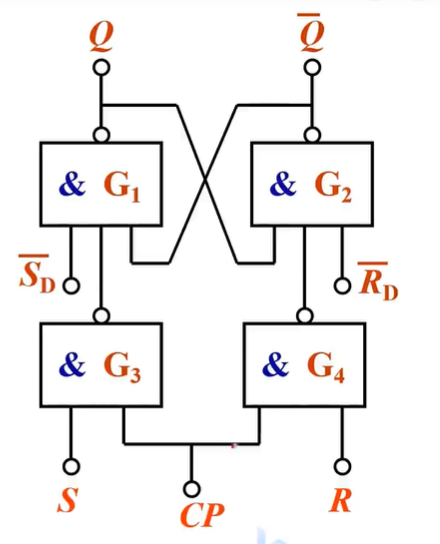

可控RS触发器

\(\overline{S},\overline{R}\),用于预置触发器的初始状态,工作过程中应处于高电平,对电路工作状态无影响。

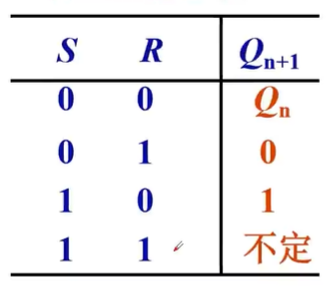

可控RS触发器状态表

\(Q_n\)-时钟到来前触发器的状态

\(Q_{n+1}\)-时钟到来后触发器的状态

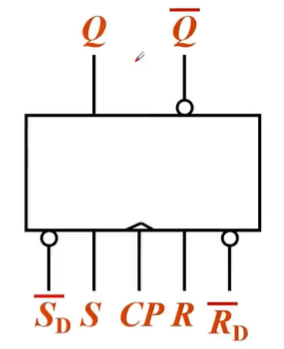

逻辑符号表

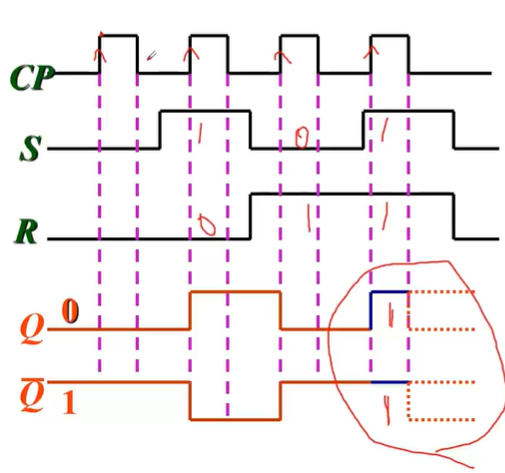

例题

画出可控R-S触发器的输出波形

存在问题

时钟脉冲不能过宽,否则出现空翻现象,即在一个时钟脉冲期间触发器翻转一次以上。

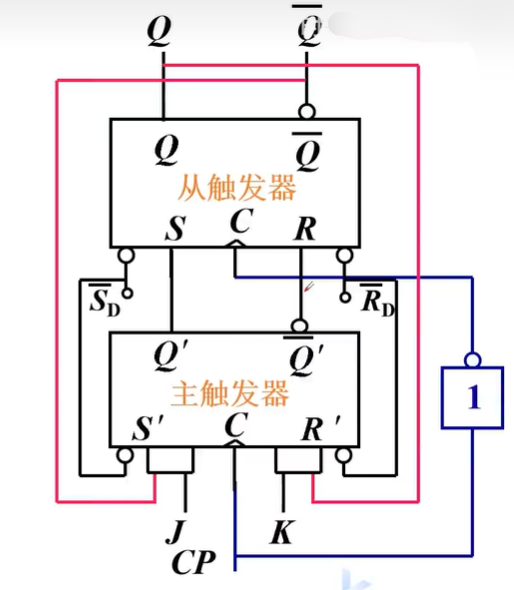

主从JK触发器

电路结构

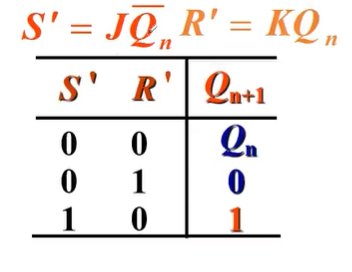

\[S' = J\overline{Q}

\]

\[R' = {K}Q

\]

工作原理

- CP高电平时触发器接收信号并暂存(即主触发器状态由J、K决定,从触发器状态保持不变)。

- CP下降沿降沿(L)触发器翻转(主、从触发器状态一致)。

- CP低电平时,主触发器封锁,J、K不起作用

- 要求CP高电平期间J、K的状态保持不变。

逻辑功能

- CP高电平时主触发器状态由J、K决定,从触发器状态不变。

- CP下降沿(L)触发器翻转(主、从触发器状态一致)

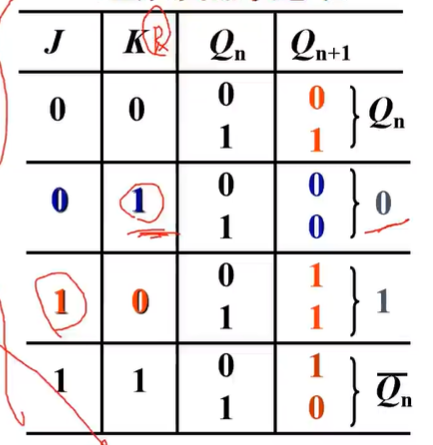

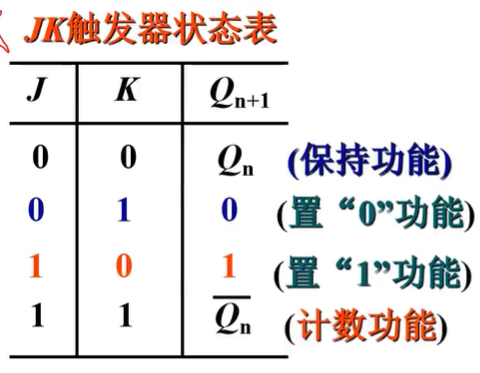

JK触发器状态表

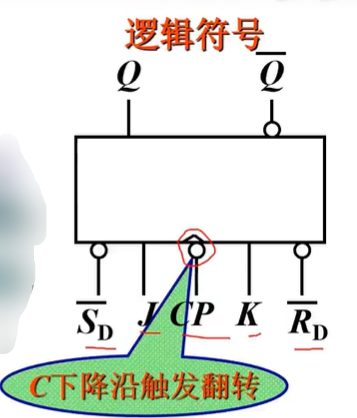

逻辑符号表

\(\overline{S},\overline{R}\),为直接置 1、置0端,不受时钟控制,低电平有效,触发器工作时\(\overline{S},\overline{R}\)应接高电平

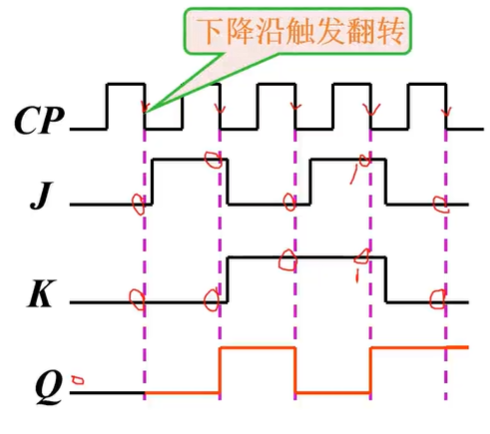

例题

JK触发器输出波形

触发器逻辑功能转换

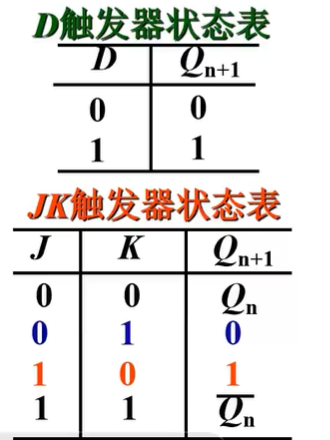

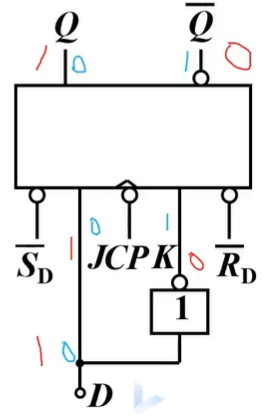

将JK触发器转换为D触发器

当$J=D,\overline{K}=D时,两触发器状态相同

状态表

逻辑符号表

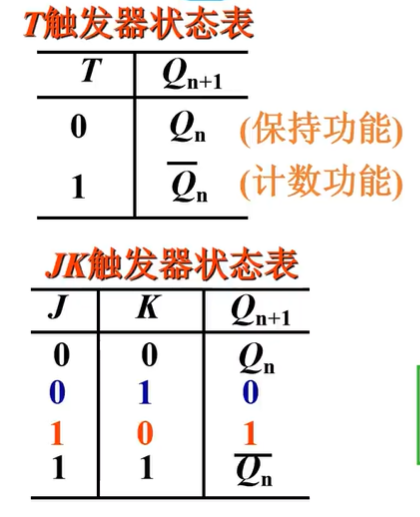

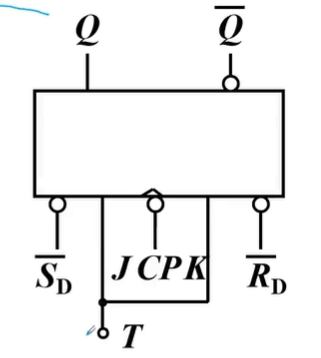

将JK触发器转换为T触发器

当J=K时,JK触发器为T触发器

状态表

逻辑符号表

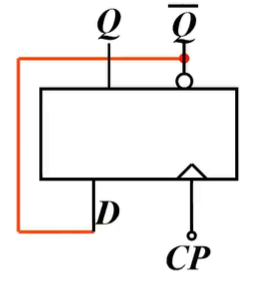

将D触发器转换为T'触发器

T'触发器仅具有计数功能,即要求来一个CP触发器就翻转一次。

逻辑符号表