AXI 总线概述

AXI协议是一种高性能、高带宽、低延迟的片内总线,具有如下特点:

1、总线的地址/控制和数据通道是分离的;

2、支持不对齐的数据传输;

3、支持突发传输,突发传输过程中只需要首地址;

4、具有分离的读/写数据通道;

5、支持显著传输访问和乱序访问;

6、更加容易进行时序收敛

在ZYNQ中支持三种AXI总线,有三种AXI接口,用的都是AXI协议。分别为:

1、AXI4:主要面向高性能地址映射通信的需求,是面向地址映射的接口。

2、AXI4-lite:轻量级的地址映射单次传输接口,占用很少的逻辑单元。(简化版的AXI4接口)

3、AXI4-Stream:面向高速数据流数据传输;去掉了地址项,允许无限制的数据突发传输规模。

AXI4总线和AXI4-Lite具有相同的组成部分:

(1)读地址通道,包含ARVALID, ARADDR, ARREADY信号;

(2)读数据通道,包含RVALID, RDATA, RREADY, RRESP信号;

(3)写地址通道,包含AWVALID,AWADDR, AWREADY信号;

(4)写数据通道,包含WVALID, WDATA,WSTRB, WREADY信号;

(5)写应答通道,包含BVALID, BRESP, BREADY信号;

(6)系统通道,包含:ACLK,ARESETN信号。

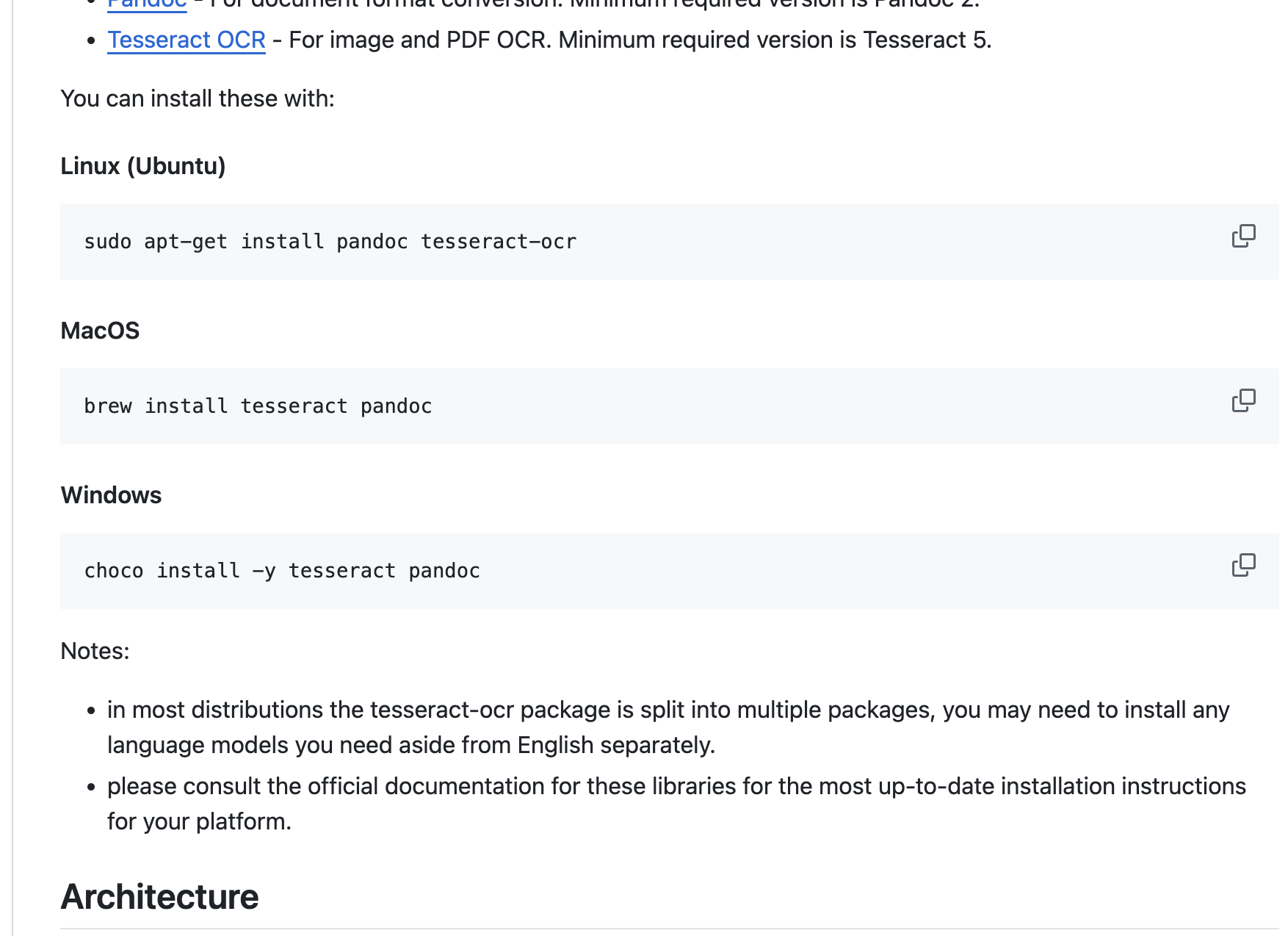

AXI4-Stream总线的组成有:

(1)ACLK信号:总线时钟,上升沿有效;

(2)ARESETN信号:总线复位,低电平有效;

(3)TREADY信号:从机高速主机做好传输准备;

(4)TDATA信号:数据,可选宽度32,64,128,256bit;

(5)TSTRB信号:每一bit对应TDATA的一个有效字节,宽度为TDATA/8;

(6)TLAST信号:主机告诉从机该次传输为突发传输的结尾;

(7)TVALID信号:主机告诉从机本机传输有效;

(8)TUSER信号:用户自定义信号,宽度为128bit。

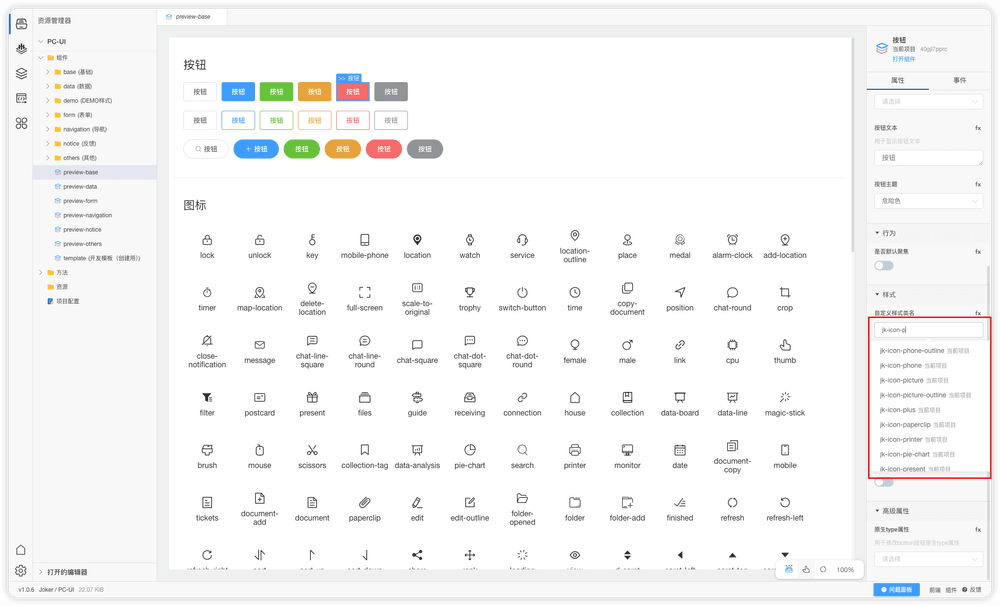

AXI接口介绍

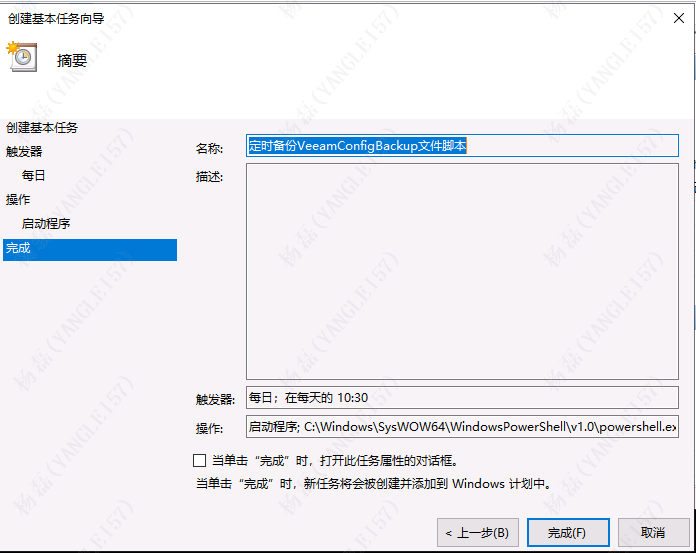

三种接口分别是:

AXI-GP接口(4个):是通用的AXI接口,包括两个32位主设备接口和两个32位从设备接口,用该接口可以访问PS中的片内外设。

AXI-HP接口(4个):是高性能/带宽的标准的接口,PL模块作为主设备连接(从下图中箭头可以看出)。主要用于PL访问PS上的存储器(DDR和On-Chip RAM)

AXI-ACP接口(1个):是ARM多核架构下定义的一种接口,中文翻译为加速器一致性端口,用来管理DMA之类的不带缓存的AXI外设,PS端是Slave接口。

AXI总线协议的两端可以分为主、从两端,他们之间一般需要一个AXI Interconnect 相连接,作用是提供将一个或多个AXI主设备连接到一个或多个AXI从设备的一种交换机制。

AXI协议-握手协议

AXI4 所采用的是一种 READY,VALID 握手通信机制,简单来说主从双方进行数据通信前,有一个握手的过程。传输源产生 VLAID 信号来指明何时数据或控制信息有效。而目地源产生 READY 信号来指明已经准备好接受数据或控制信息。

ACLK为时钟信号,在AXI协议中,所有的输入信号都在是ACLK的上升沿采样,所有的输出信号必须在ACLK的上升沿之后才能改变。需要注意的是,一旦VALID拉高,源端必须保持其处于有效状态,直至成功握手(在时钟上升沿检测到VALID和READY同时为有效状态)。

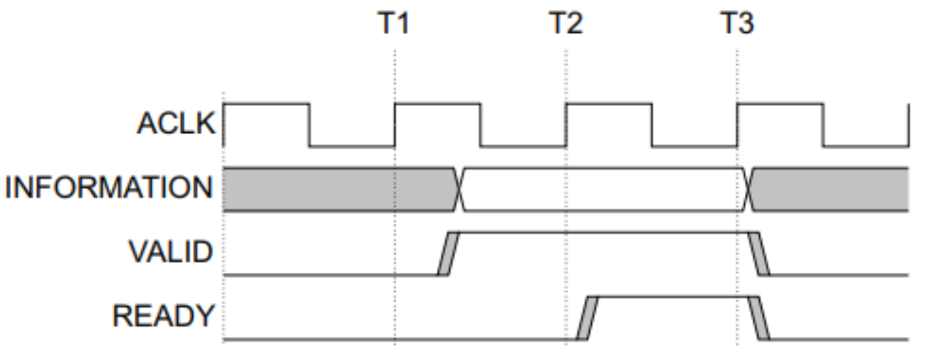

传输发生在 VALID和 READY 信号同时为高的时候。VALID 和 READY 信号的出现有三种关系。1、VALID比READY提前拉高

信息在T3时刻发生传输。

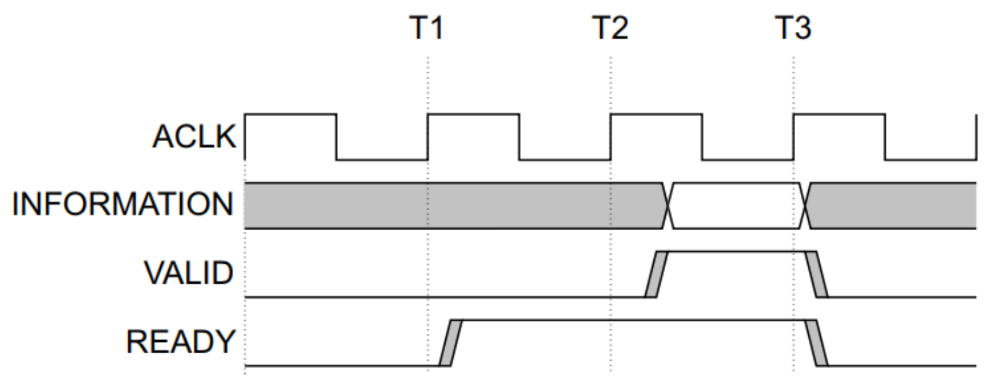

2、READY比VALID提前拉高

信息在T3时刻发生传输。

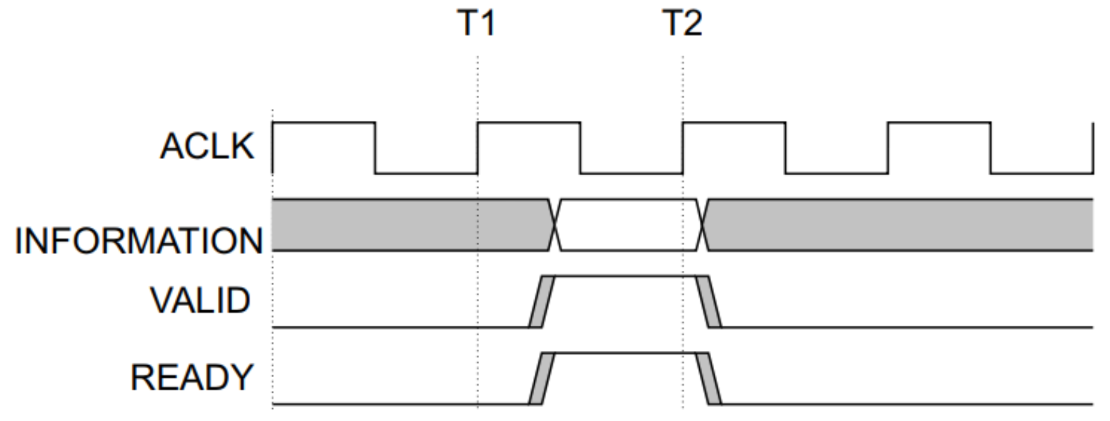

3、READY比VALID同时拉高

信息在T2时刻发生传输。

在AXI协议中地址、读、写和写响应通道之间的关系是灵活的。例如,写数据可以出现在接口上早于与其相关联的写地址。也有可能写数据与写地址在一个周期中出现,但是两种关系必须被保持:

(1)**读数据必须总是跟在与其数据相关联的地址之后。**

(2)**写响应必须总是跟在与其相关联的写事务的最后出现。**