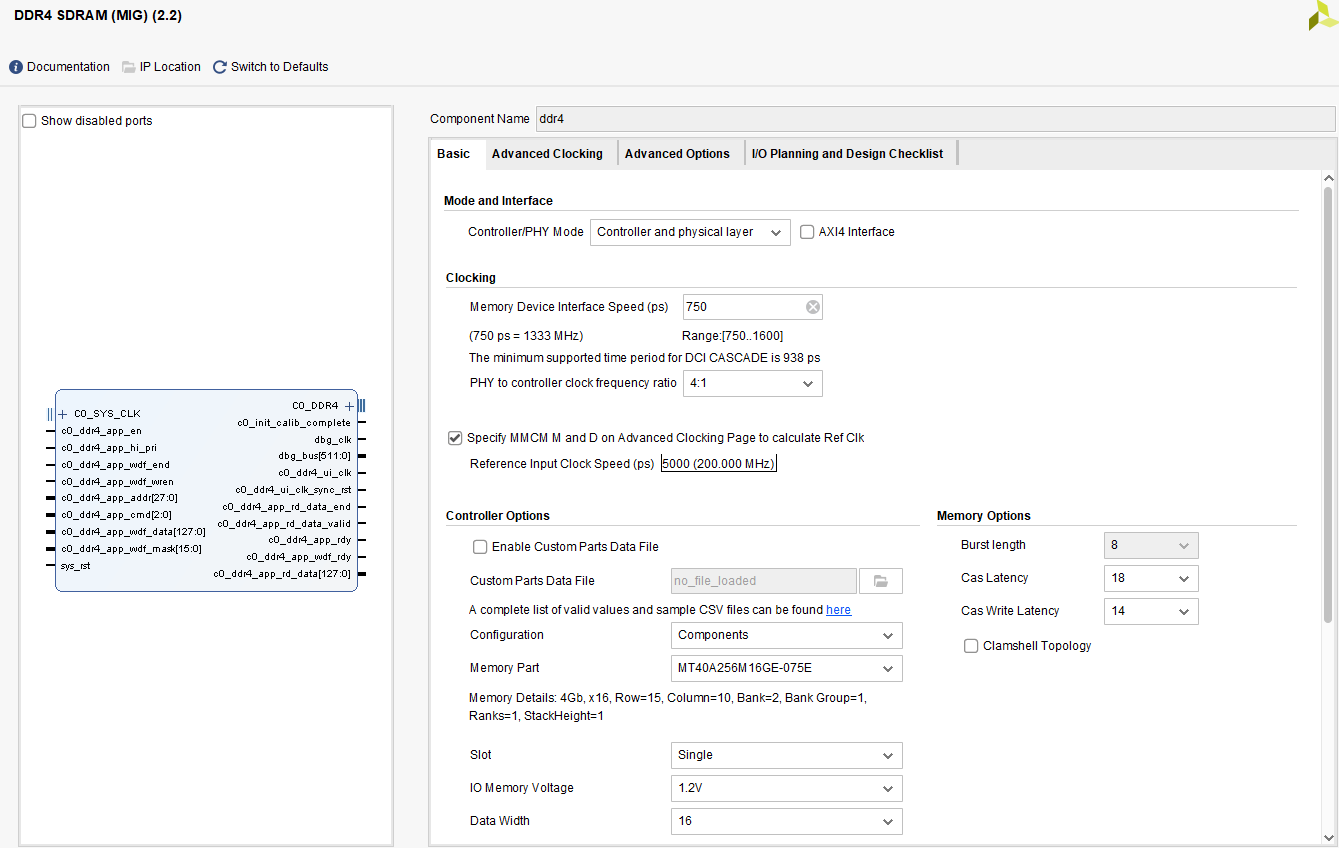

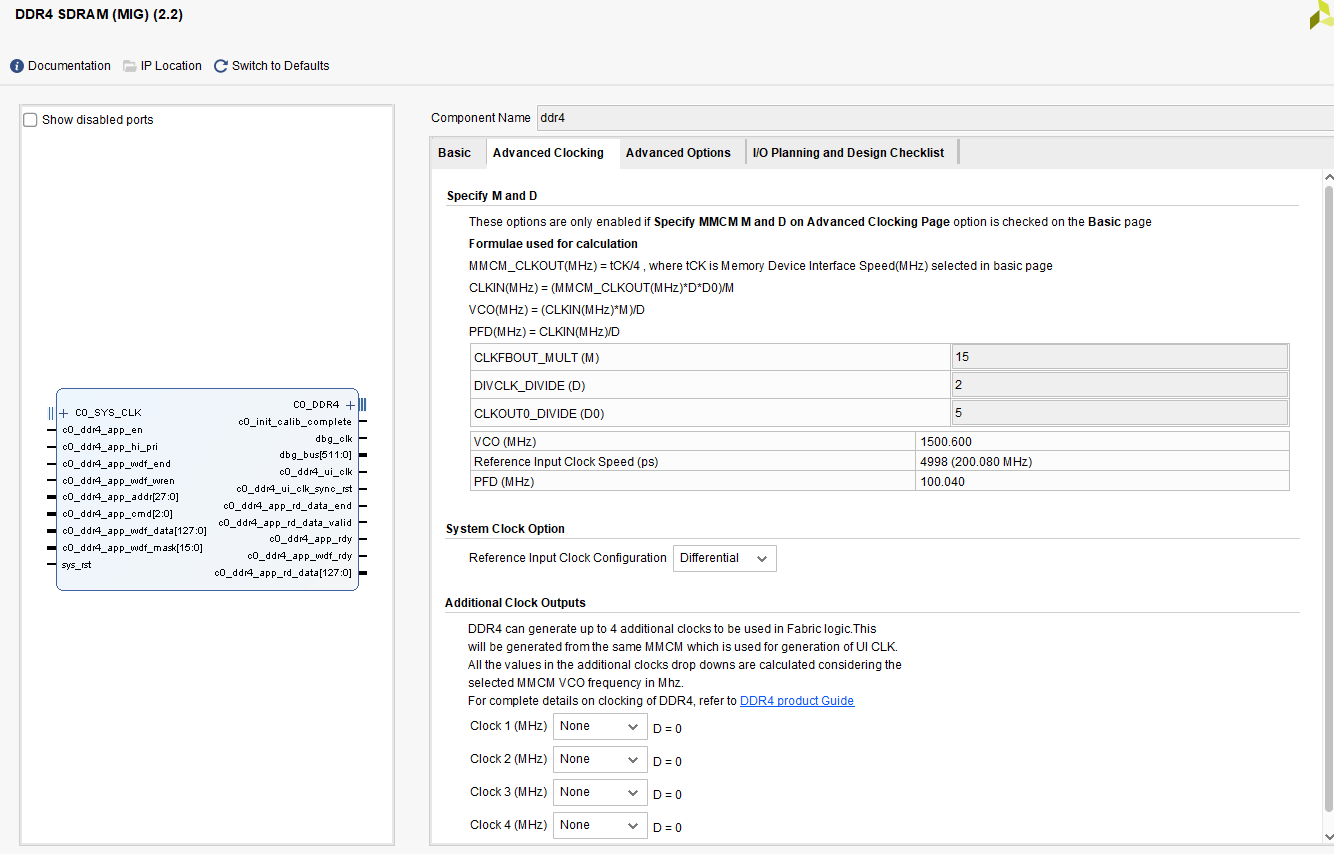

第一种配置方法如下。按最高2666MHz配置,这边输入的参考时钟看个人板卡情况,我这边输入是200MHz。

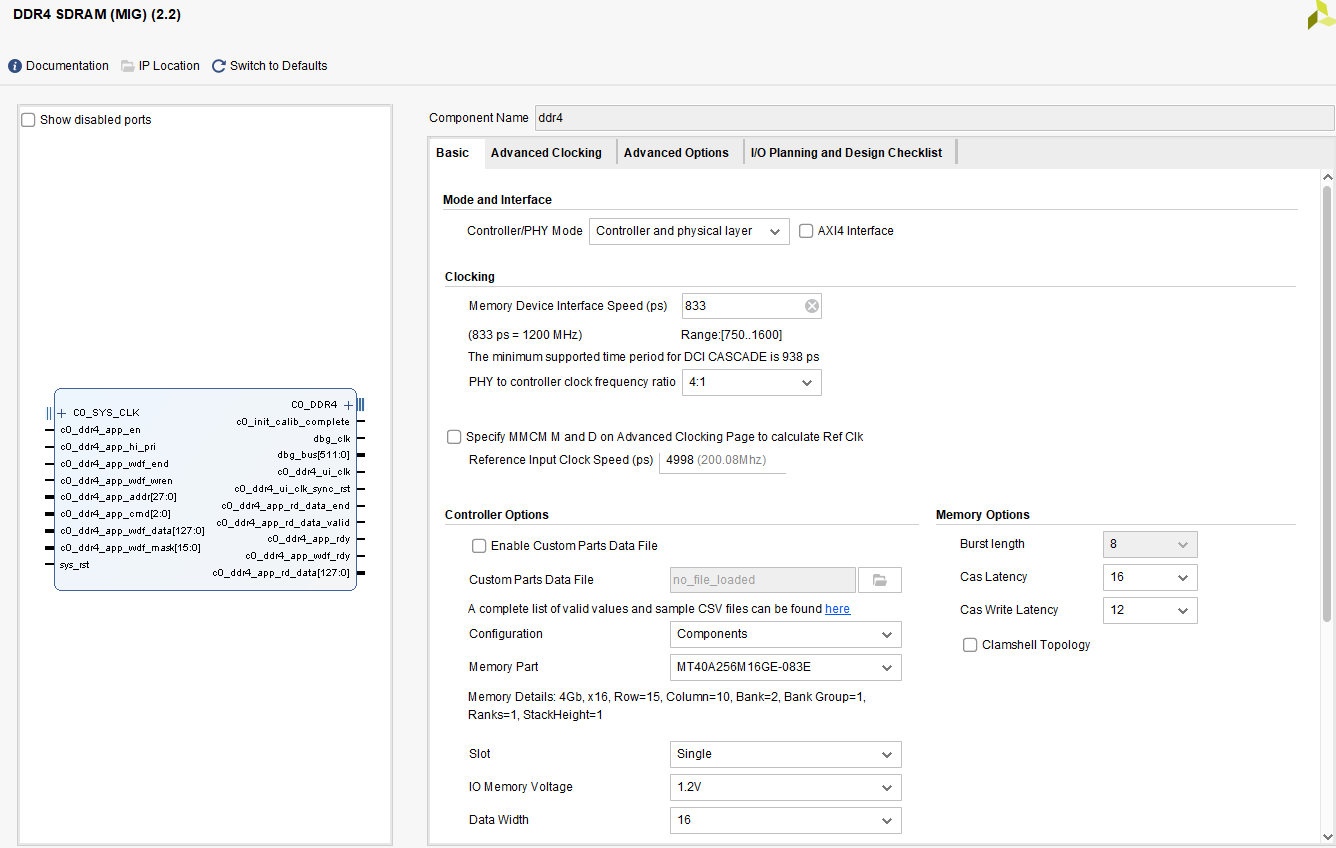

第二种配置方法如下。按2400MHz配置(需要换芯片型号),这边输入的参考时钟看个人板卡情况,我这边输入是200MHz。

这边是输入时钟设置及输出时钟设置。我这边输入是差分时钟,且不需要再要其他时钟。

配置好之后,打开example design,切换仿真平台至modelsim,点击simulation开始仿真。

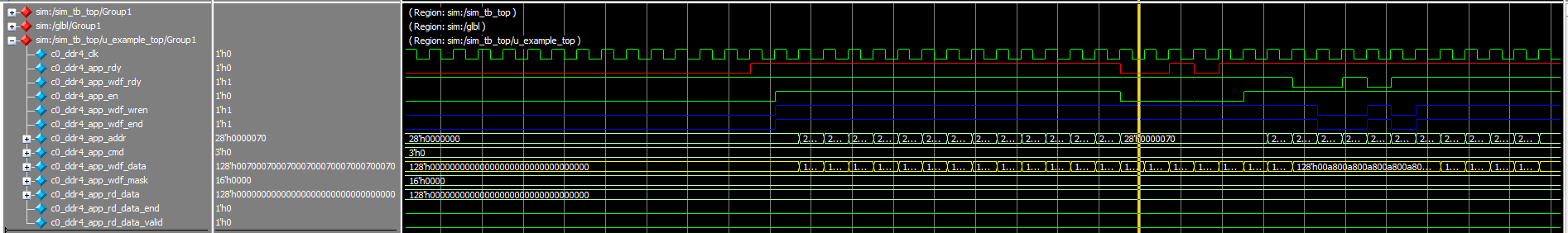

在wave窗口中加入MIG IP核用户端的信号,查看时序。

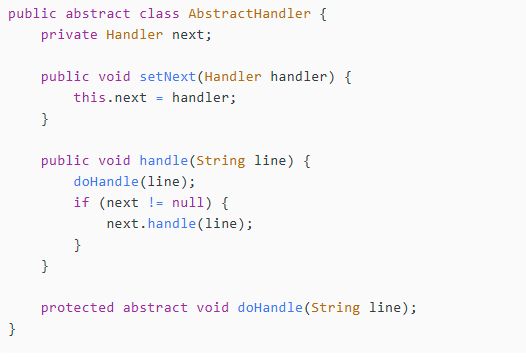

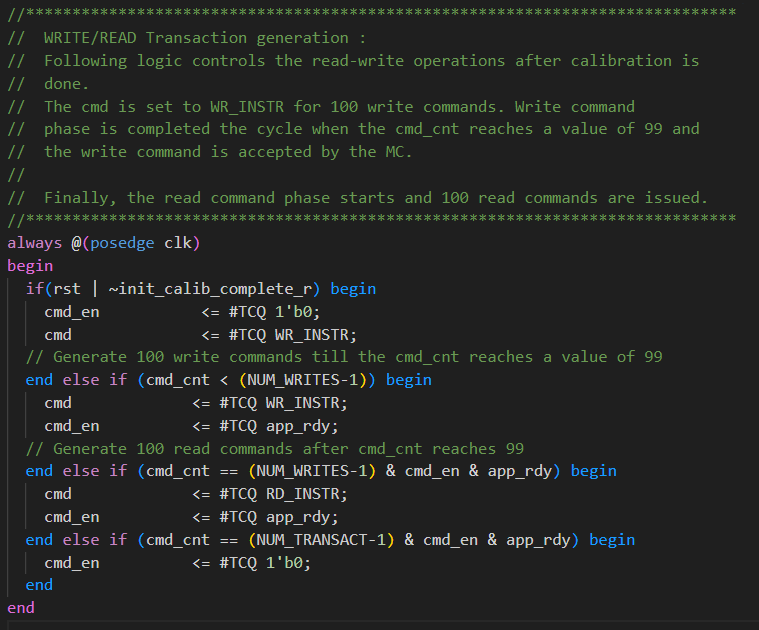

先看app_en的逻辑部分,assign app_en = cmd_en & (app_rdy) ;其中cmd_en为下图。

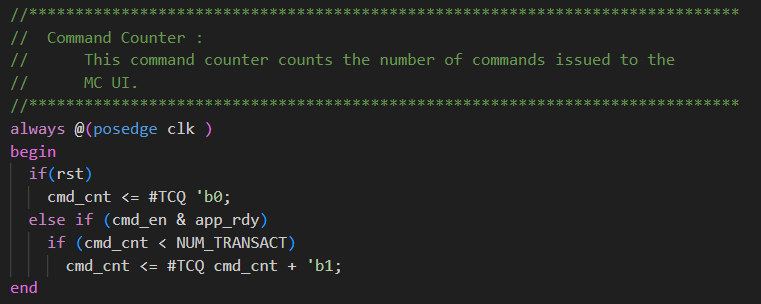

再看什么时候才能算一次读和写的时序。

从上面两部分代码可以知道,cmd_en是app_rdy的延迟一拍信号,而一次完整可被记录的读和写时序必须要两个周期app_rdy的信号。后面cmd_en一直为1是因为当完成写的个数之后,会一直保持为自身,未有其他赋值。

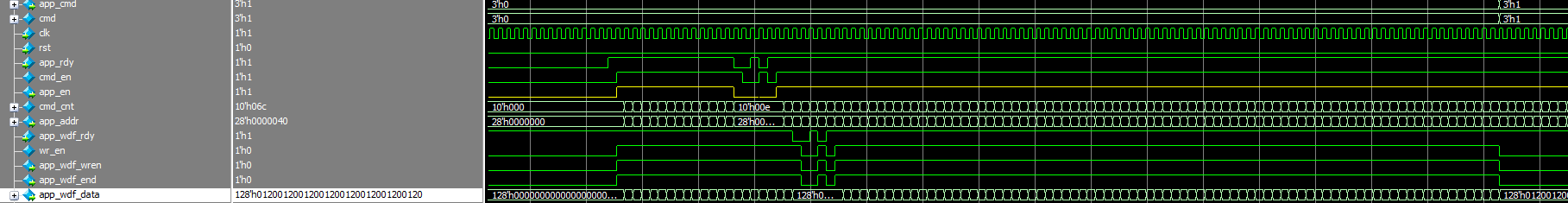

再来看app_en和app_addr以及cmd_cnt的波形。

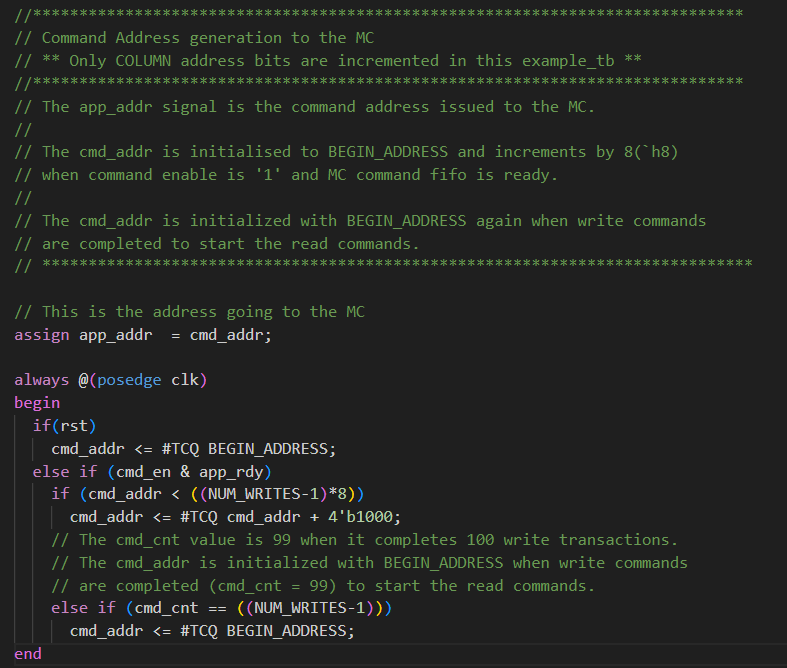

app_addr的代码如下。逻辑很明显,不再详述。

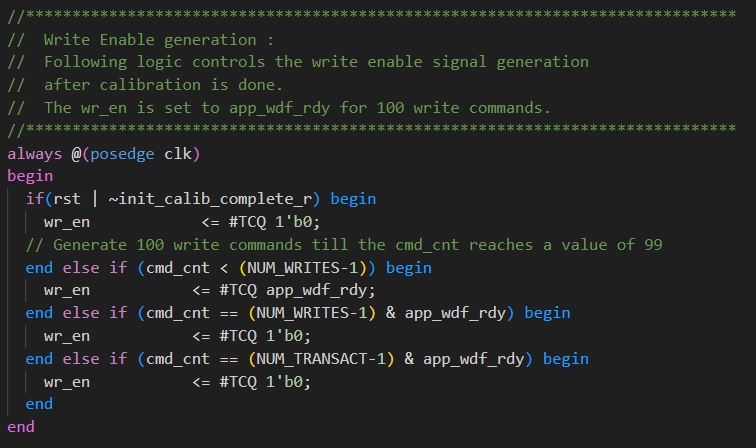

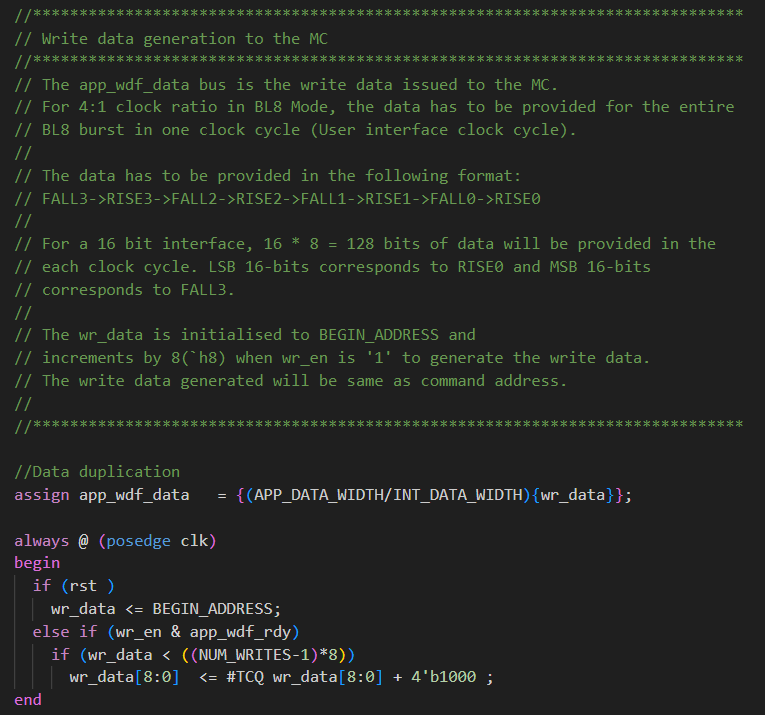

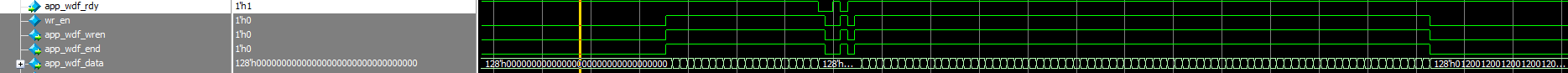

app_wdf_data、app_wdf_wren和app_wdf_end以及所涉及的wr_en代码及波形如下,逻辑很明显,不再详述。

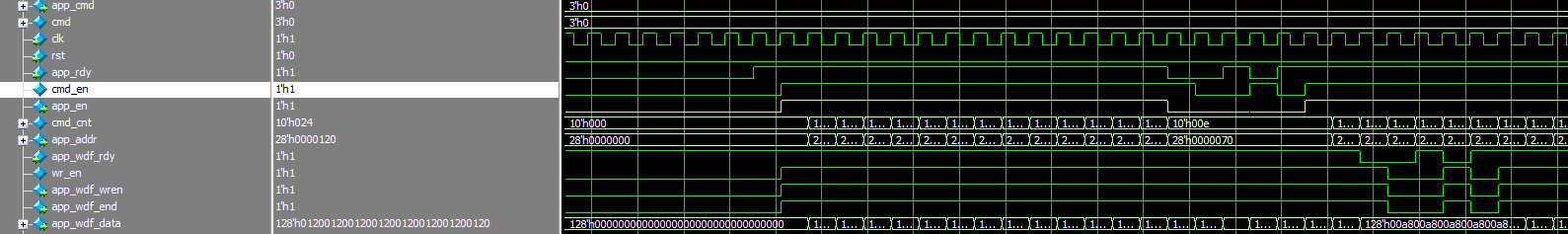

整体上的写时序波形如下。仔细观察会发现,写入的地址和数据在个数上是相同的,但是两个分别有了五个周期的停摆现象。但是不影响最后的结果。

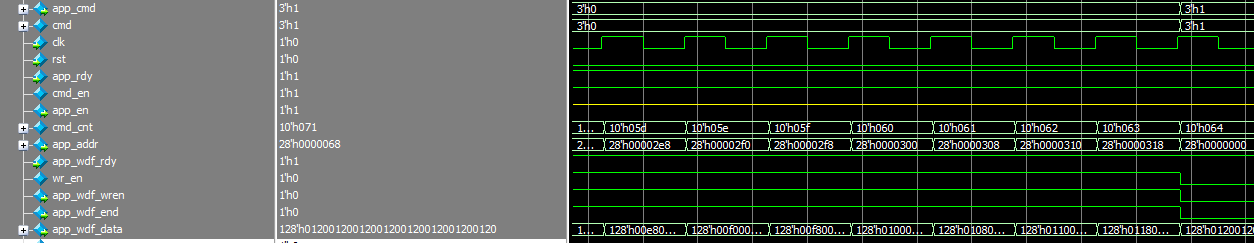

前面和最后面放大看一下。

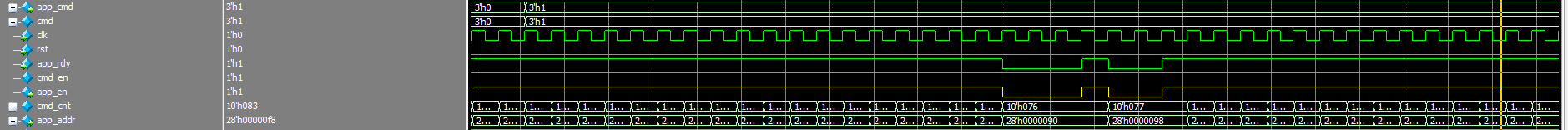

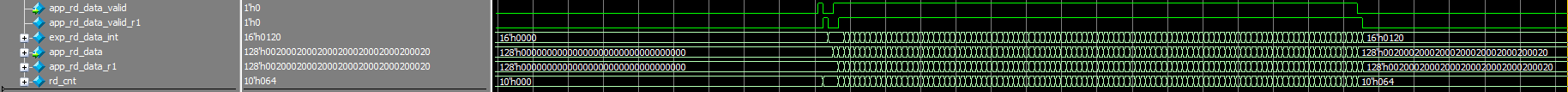

然后我们来看读时序,读时序紧接着写时序,开头就在上面的图,这边不再截新图。中间阶段如下,app_en只与app_rdy有关,且地址只在为1的时候更新。写入命令个数从10'h64到10'h0c7,共100个读命令,对应地址从28'h0到28'h318。

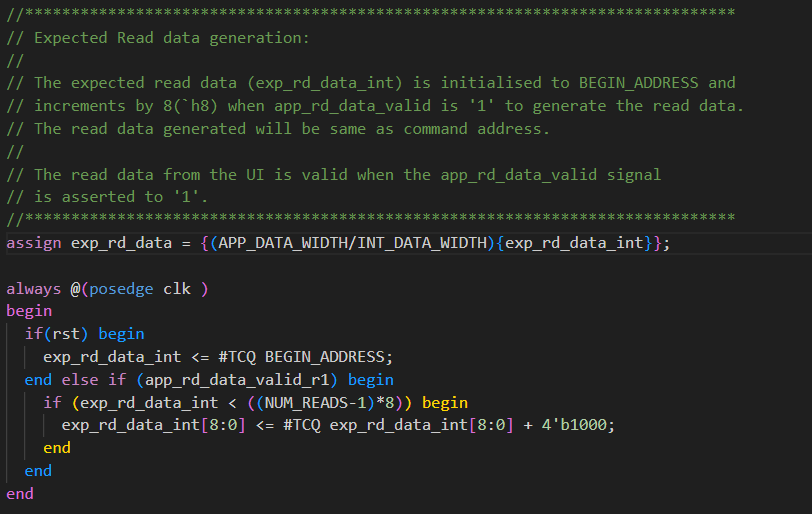

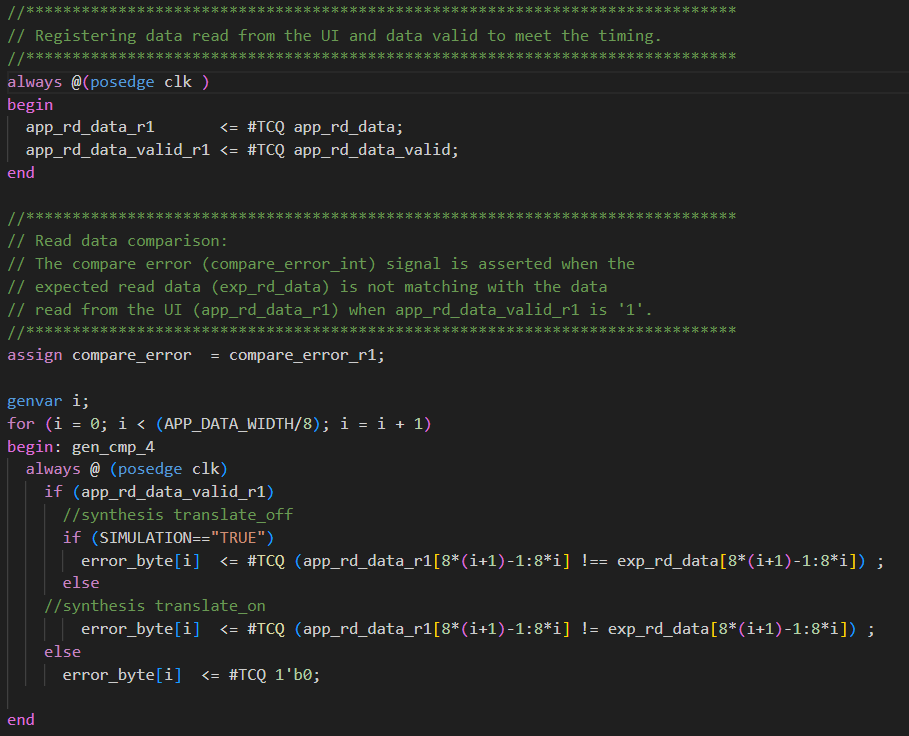

最后是验证的代码和波形图,大家可以自行查看。

PL端DDR4的MIG IP核配置及example design分析(个人记录)

本文来自互联网用户投稿,该文观点仅代表作者本人,不代表本站立场。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如若转载,请注明出处:http://www.hqwc.cn/news/890879.html

如若内容造成侵权/违法违规/事实不符,请联系编程知识网进行投诉反馈email:809451989@qq.com,一经查实,立即删除!相关文章

Linux上部署deepseek-r1:7b模型

通过ollama在debian上安装部署deepseek-r1:7b模型。一、安装ollama框架

访问 ollama 官网,点击下载,选择 Linux,复制安装命令执行即可。二、下载并运行模型

选择 deepseek:7b 模型,复制安装命令执行即可。

(这里的模型参数大小,可根据自己的显存大小选择,可简单安装 0.5b…

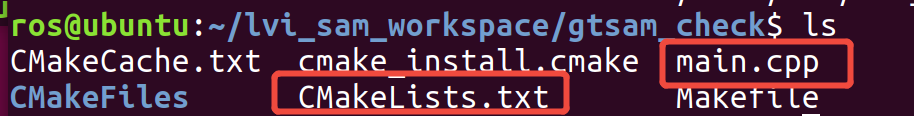

LVI_SAM虚拟机安装复现(二)

0. 前言

前一篇文章里面,已经完成了 Ubuntu 18.04 和 ROS Melodic 的安装。

还没有安装好的读者,可以回去看这一篇文章。

前情概要:

LVI_SAM虚拟机安装复现(一)

本文主要记录了GTSAM源码编译安装过程中经历的坑

警告:并非从零开始零基础教你安装 GTSAM 哦

GTSAM是一个开源…

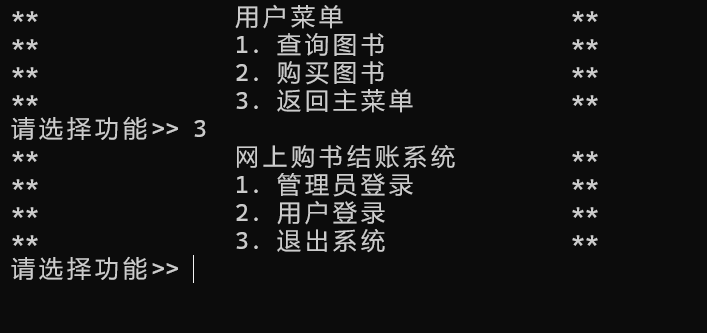

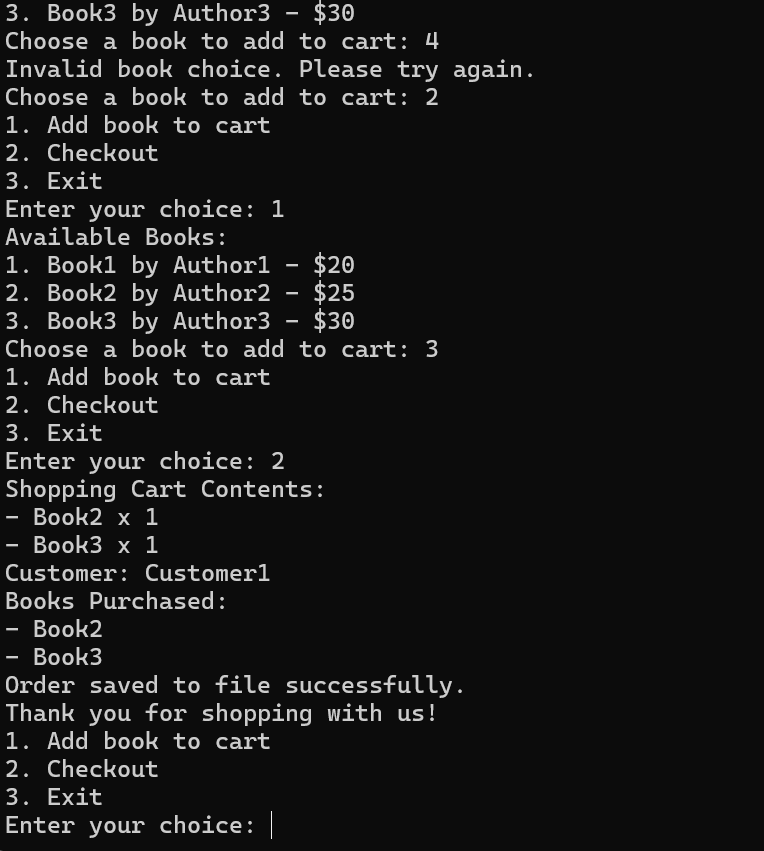

逆向软件设计—网上购书结账系统

一、作业要求找一个已有的项目(同学、高年级同学、网络下载),阅读分析,找出软件尚存的缺陷, 改进其软件做二次开发,并将这个过程整理成一份博客。

二、原项目介绍

本次课程设计我逆向开发的软件是一个使用c++编写的网上购书结账系统,原作者是22软工2班的熊知宇学长,学号…

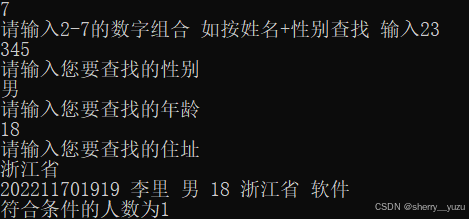

学生管理系统二次开发与优化实践

在软件开发中,对现有项目进行优化和二次开发是一种常见的任务。本次实验中,我选择了一个基于C++开发的学生管理系统作为优化对象。该系统实现了学生信息的增删改查功能,并支持学号排序和模糊查找等功能。通过分析原项目,我发现了几个可以改进的地方,并对系统进行了优化。以…

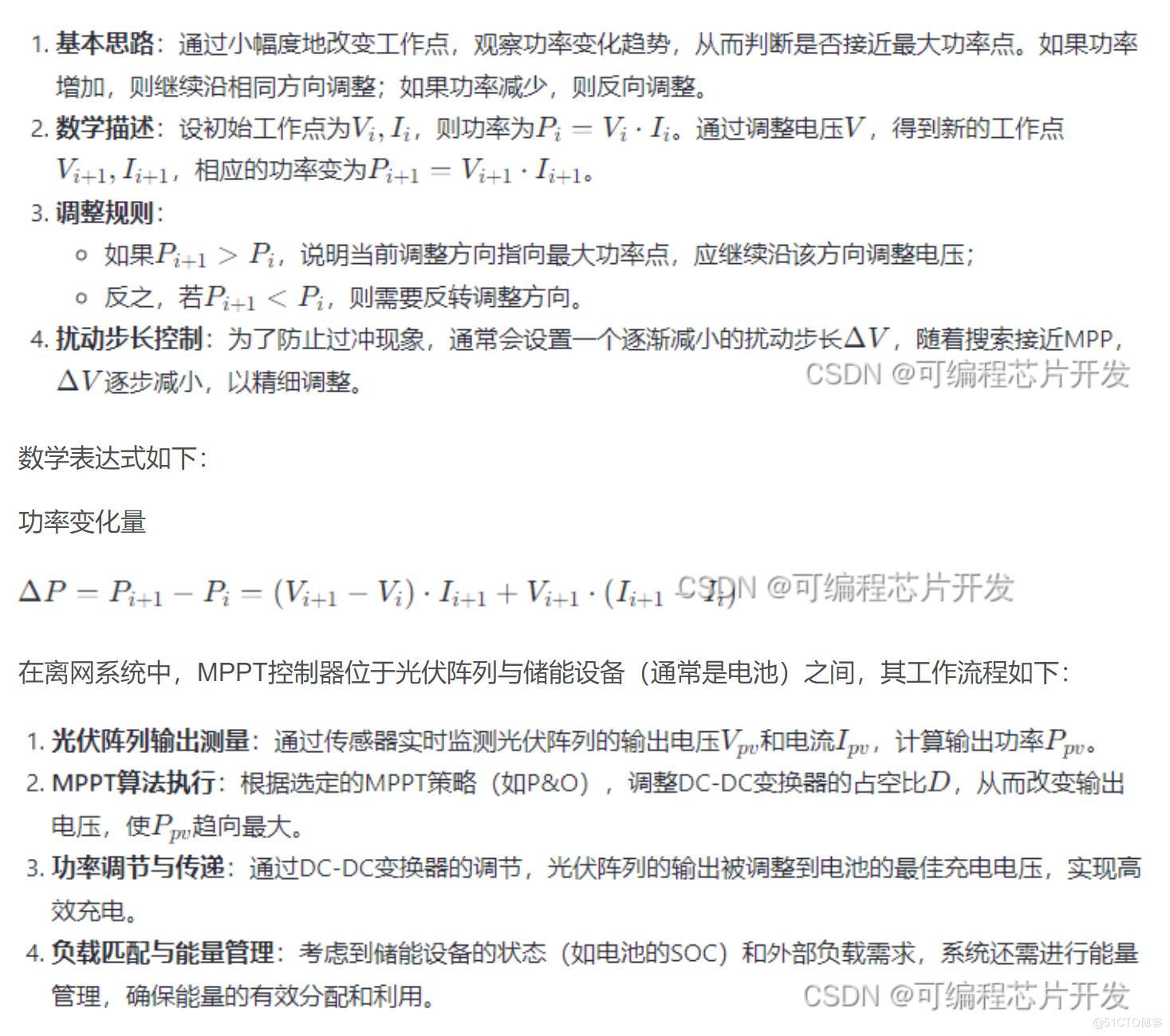

基于MPPT最大功率跟踪的离网光伏发电系统Simulink建模与仿真

1.课题概述

基于MPPT最大功率跟踪的离网光伏发电系统Simulink建模与仿真。2.系统仿真结果

(完整程序运行后无水印)3.核心程序与模型

版本:MATLAB2022a4.系统原理简介基于最大功率点跟踪(Maximum Power Point Tracking, MPPT)的离网光伏发电系统是利用太阳光直接转换为电能…

[Black Watch 入群题]PWN(栈迁移)

先检查一下保护,32位的分析一下代码,发现buf距离ebp为0x18(24),但是read只溢出0x20(32),也就是只溢出8个字节,刚好覆盖到ret。

第一个read读取0x200到s(.bss段)两个write会打印m1和m2,点击m1,m2查看因为溢出不够,这时候我们可以考虑栈迁移expfrom pwn import *

f…

WC Java 实现

一.来源

WC Java 实现(Pramy)

https://www.cnblogs.com/pramy/p/9607743.html

二.运行环境及运行结果

运行环境:Visual Studio Code

运行结果截图:*

三.主要问题

1.异常处理不够详细:

在处理文件时,如果文件不存在或无法读取,程序会抛出异常,但没有提供详细的错误信息或…

docker实现的基本原理

Docker 实现容器的基本原理依赖于 Linux 内核的三大核心机制:命名空间(Namespaces)、控制组(cgroups) 和 联合文件系统(UnionFS),也是 Docker 能够出现的最重要原因。

1. 命名空间(Namespaces)

作用:实现资源的隔离,使容器内的进程无法感知或干扰宿主机的其他进程或…

将DeepSeek接入人类大脑会怎样??

昨天在与同事聊起最近大火的DeepSeek,

突然,有一个不切实际的想法,如果DeepSeek或人工智能AI能以某种形式接入人类大脑,

比如,通过芯片不侵入式连接大脑 或者 外带什么眼镜、 隐形眼镜之类的,

能人类有DeepSeek一样的知识量以及响应速度,那得多好,整个世界、人类将会变…

gh-ost工具介绍及使用

💖简介

gh-ost 是一款由GitHub开发的在线DDL(Online Data Definition Language)变更工具,专门用于MySQL数据库。它允许在不锁定表的情况下执行数据库模式变更,从而避免了传统ALTER TABLE命令可能带来的长时间锁表问题,这对于高可用性要求严格的生产环境尤为重要。

它通过…

![[Black Watch 入群题]PWN(栈迁移)](https://img2024.cnblogs.com/blog/3546944/202502/3546944-20250227205302185-1047388964.png)