1.算法仿真效果

本文是之前写的文章:

《基于FPGA的1024QAM基带通信系统,包含testbench,高斯信道模块,误码率统计模块,可以设置不同SNR》

的硬件测试版本。

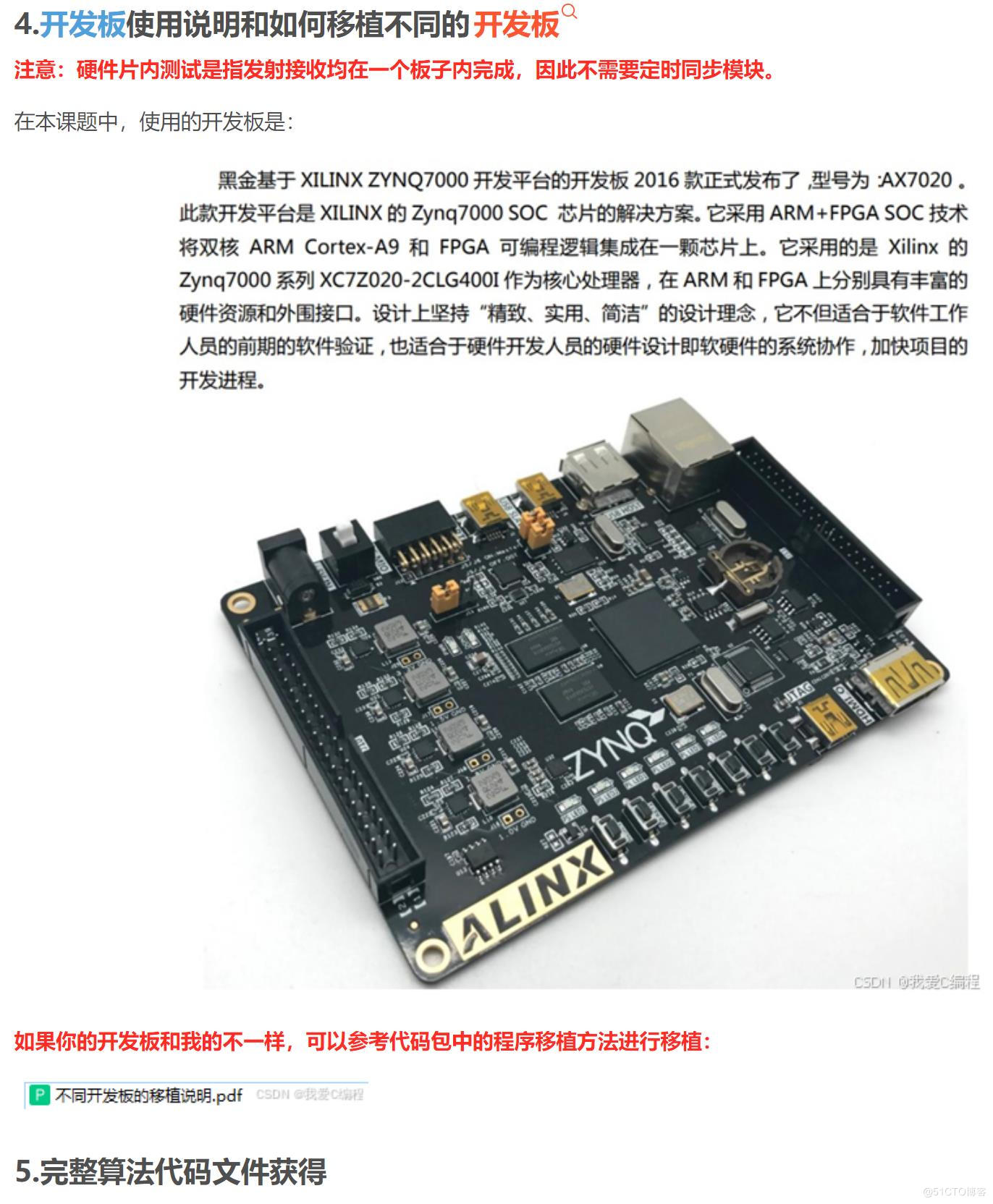

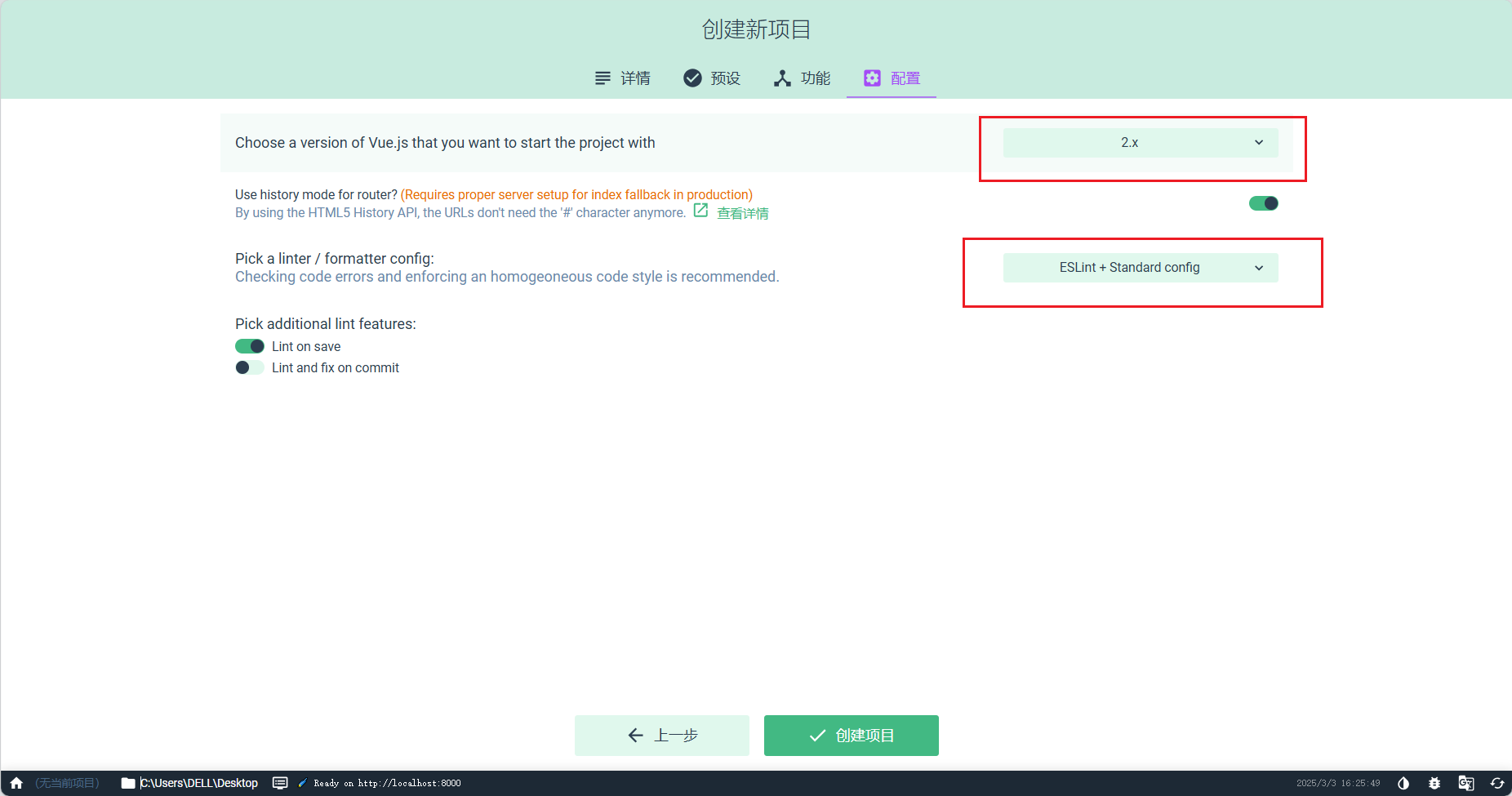

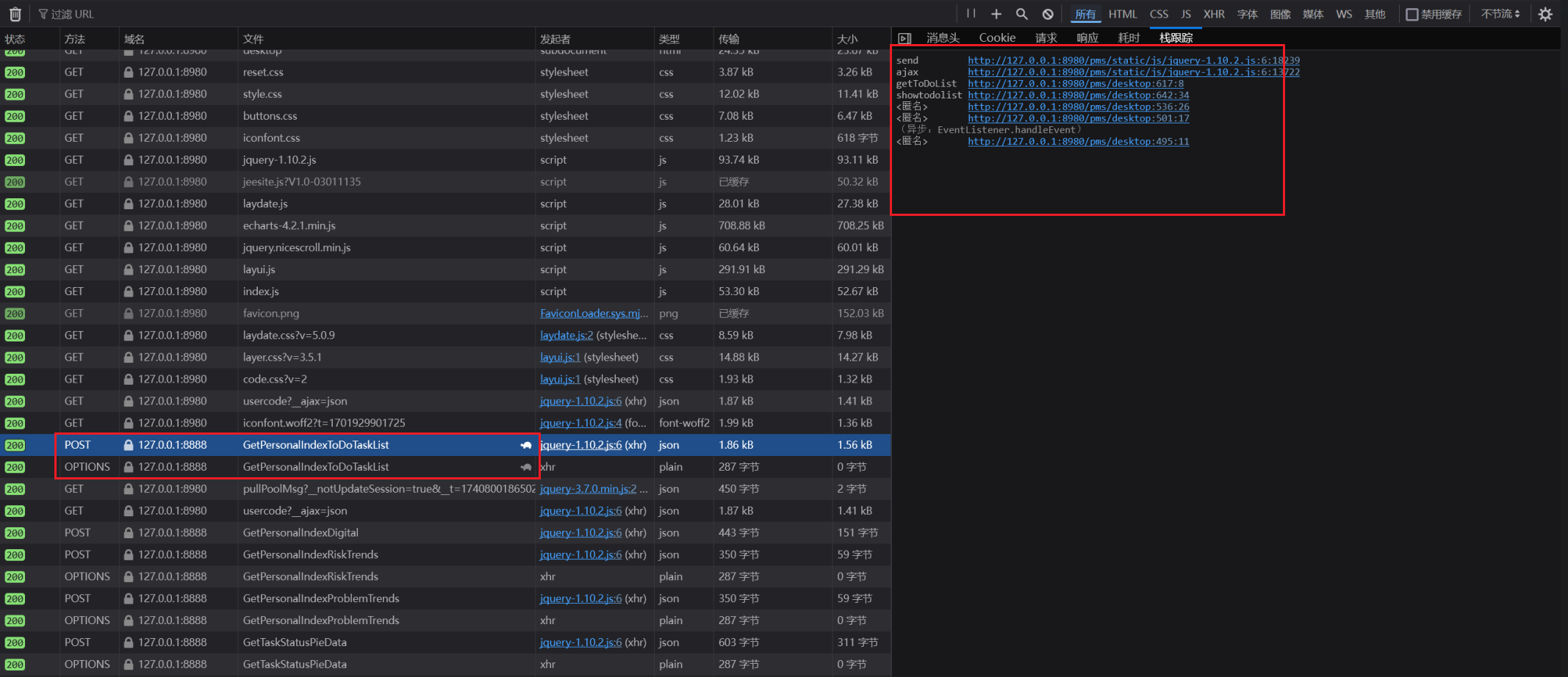

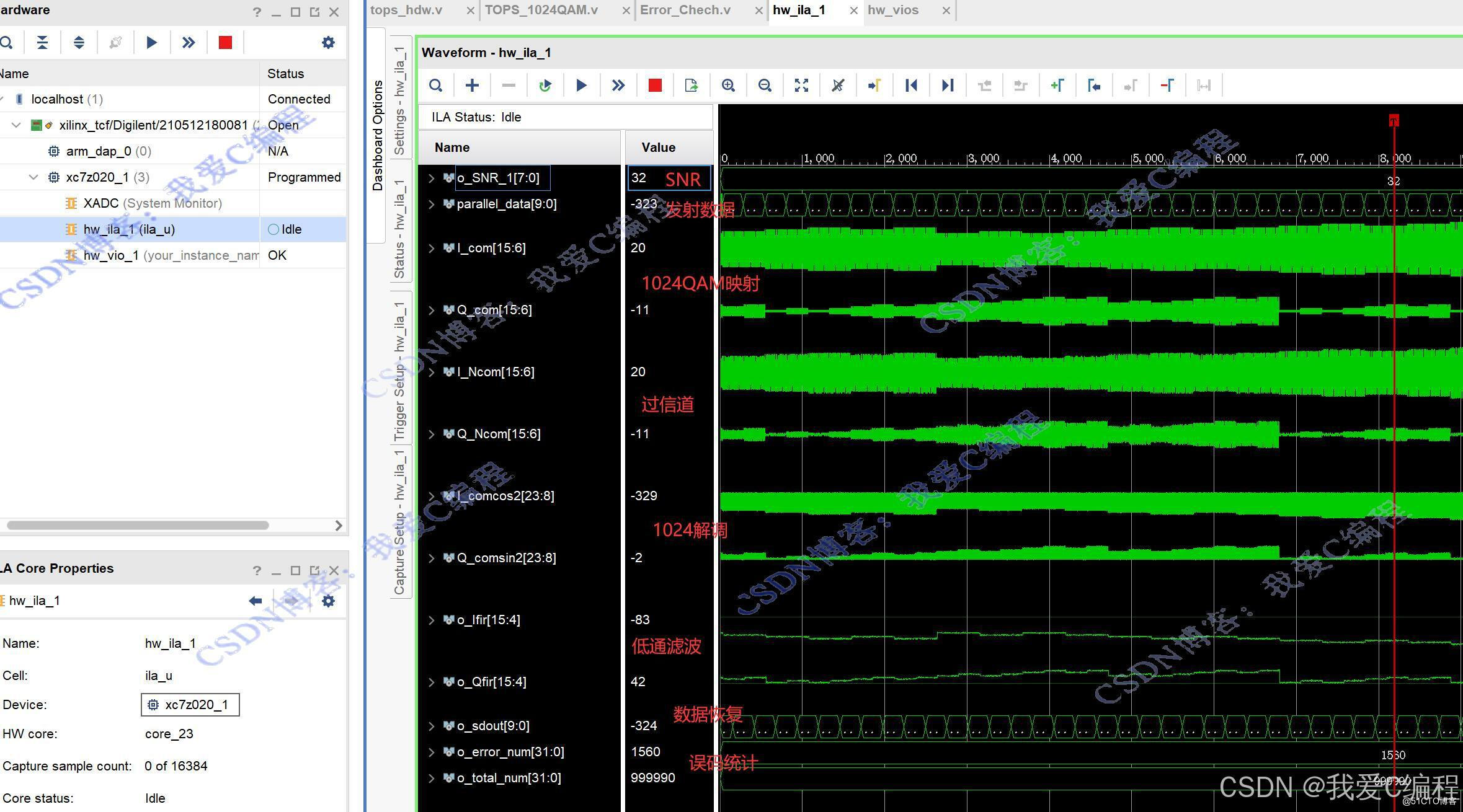

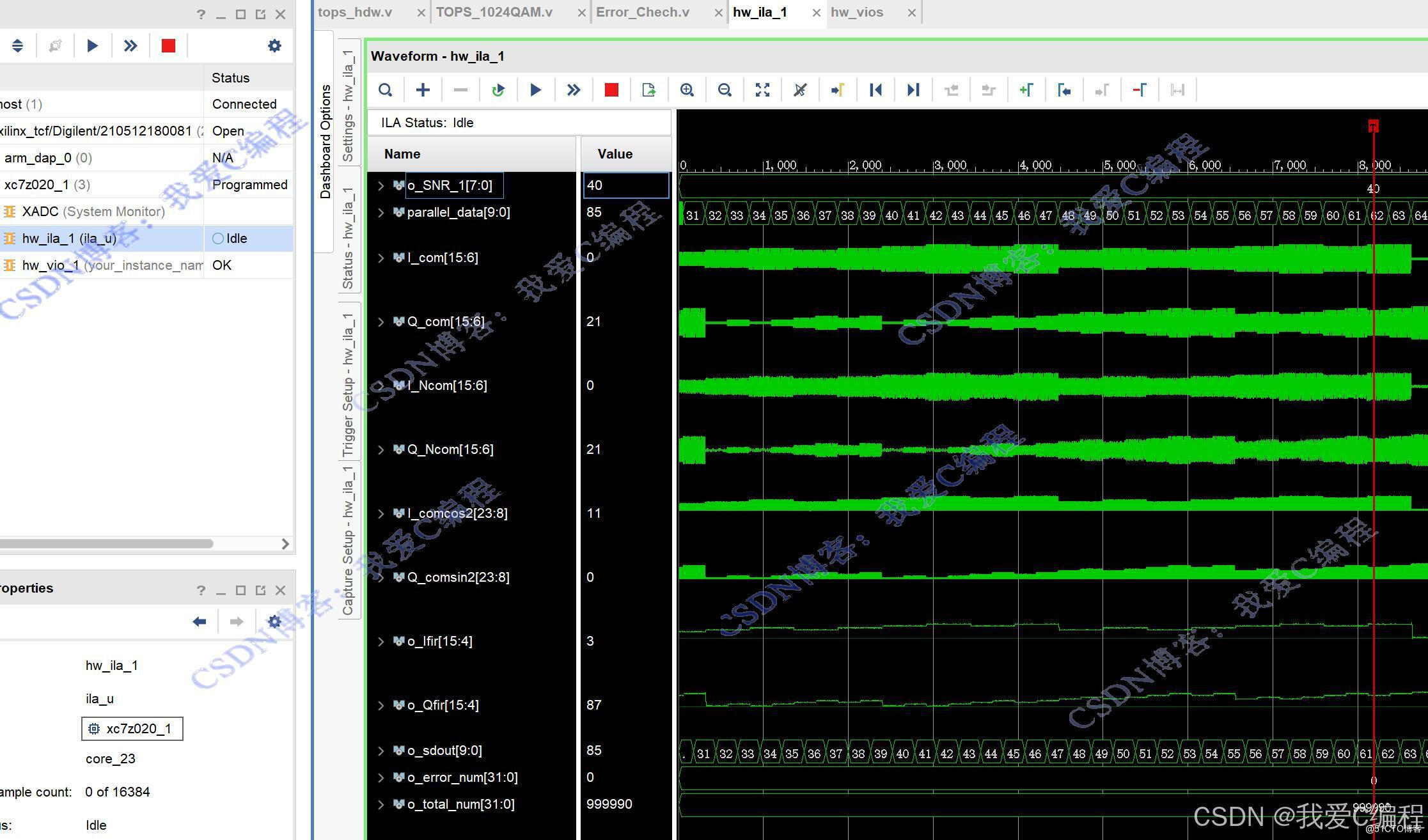

在系统在仿真版本基础上增加了ila在线数据采集模块,vio在线SNR设置模块,数据源模块。硬件ila测试结果如下:(完整代码运行后无水印):

vio设置SNR=32db

vio设置SNR=40db

硬件测试操作步骤可参考程序配套的操作视频。

2.算法涉及理论知识概要

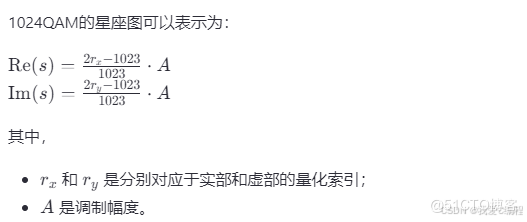

1024QAM是一种高级调制方式,可以携带更多的信息位(10比特/符号),从而实现更高的数据传输速率。然而,这也带来了更高的误码率(BER)要求和更复杂的信号处理需求。FPGA由于其可编程性和高性能,成为实现这种复杂调制的理想平台。1024QAM调制将输入的10比特映射到一个复数平面上的1024个不同的星座点之一。每个星座点的位置由输入比特决定,且分布在二维平面上。

基于FPGA的1024QAM基带通信系统通常包含以下几个模块:

数据接口:负责数据的输入输出。

串并转换:将串行数据转换为并行数据。

星座映射:将输入数据映射到星座点。

调制器:生成IQ信号。

解调器:从接收到的信号中恢复IQ信号。

星座检测:检测最接近的星座点。

并串转换:将并行数据转换为串行数据。

3.Verilog核心程序

`timescale 1ns / 1ps

//

// Company:

// Engineer:

//

// Create Date: 2024/12/04 15:36:43

// Design Name:

// Module Name: tops_hdw

// Project Name:

// Target Devices:

// Tool Versions:

// Description:

//

// Dependencies:

//

// Revision:

// Revision 0.01 - File Created

// Additional Comments:

//

//module tops_hdw(input i_clk,

input i_rst,

output reg [3:0] led

);//设置SNR

wire signed[7:0]o_SNR;

vio_0 your_instance_name (.clk(i_clk), // input wire clk.probe_out0(o_SNR) // output wire [7 : 0] probe_out0

);wire [9:0] parallel_data;

wire signed[15:0]sin;

wire signed[15:0]cos;

wire signed[15:0] I_com;

wire signed[15:0] Q_com;

wire signed[15:0]I_Ncom;

wire signed[15:0]Q_Ncom;

wire signed[23:0]I_comcos2;

wire signed[23:0]Q_comsin2;

wire signed[15:0]o_Ifir;

wire signed[15:0]o_Qfir;

wire [9:0] o_sdout;

wire signed[31:0]o_error_num;

wire signed[31:0]o_total_num;TOPS_1024QAM TOPS_1024QAM_u(

.clk (i_clk),

.rst (i_rst),

.start (1'b1),

.i_SNR (o_SNR),

.parallel_data (parallel_data),

.sin (sin),

.cos (cos),

.I_com (I_com),

.Q_com (Q_com),

.I_Ncom (I_Ncom),

.Q_Ncom (Q_Ncom),

.I_comcos2 (I_comcos2),

.Q_comsin2 (Q_comsin2),

.o_Ifir (o_Ifir),

.o_Qfir (o_Qfir),

.o_sdout (o_sdout),

.flag_reg (),

.o_error_num (o_error_num),

.o_total_num (o_total_num)

);//ila篇内测试分析模块

ila_0 ila_u (.clk(i_clk), // input wire clk.probe0({ o_SNR,//8I_com[15:6], Q_com[15:6],I_Ncom[15:6],Q_Ncom[15:6],//40I_comcos2[23:8],Q_comsin2[23:8],o_Ifir[15:4],o_Qfir[15:4],//52parallel_data,o_sdout,//20o_error_num,o_total_num//64}));endmodule