简单做个summary手册,方便后面查阅以及组里统一规范。

全定制电路Flow手册

编写人:袁易扬

联系方式:2861704773@qq.com

| 文档版本 | 编写日期 | 说明 |

|---|---|---|

| v1.0 | 2024.3.27 | 初次发布 |

1. 工具链

原理图:

Cadence Virtuoso IC617/618(用于22nm及以上的平面CMOS工艺)

Cadence Virtuoso ICADV(用于16nm及以下的Finfet先进工艺)

仿真:

Cadence Spectre(模拟仿真)

Cadence AMS(数模混仿)

版图:

Cadence Virtuoso IC617/618(用于22nm及以上的平面CMOS工艺)

Cadence Virtuoso ICADV(用于16nm及以下的Finfet先进工艺)

后仿真:

Calibre xRC/xACT

Cadence QRC

物理验证:

Calibre DRC/LVS

2. 全定制电路基本流程

设计文档编写->原理图绘制->原理图仿真验证->版图Floorplan->版图Placement->版图Route->版图DRC/LVS->后仿验证

3. 文档规范

原始文档建议使用markdown进行编辑,markdown编写软件推荐使用Typora(可以下载免费版,也可以购买付费版),也可以使用vscode安装markdown插件后作为markdown编辑器使用。

设计文档格式可参考《设计文档模板》,内容需要包括:

- 模块/芯片功能描述(描述模块/芯片整体功能)

- 模块/芯片架构描述(包含框图以及子模块功能基本描述)

- 模块/芯片端口(使用表格进行描述,表格中需要包含以下内容:Port 端口名;Width 端口位宽;Direction 端口方向; Function 功能描述)

如果存在模块/芯片存储器和存储器也需要进行描述:

- 模块/芯片寄存器(使用表格进行描述,表格中需要包含以下内容:Address 地址;Name:寄存器名;Type:功能(读写/只读/只写); Function 功能描述;Reset Value 复位值)

- 模块/芯片存储器(使用表格进行描述,表格中需要包含以下内容:Start Address 起始地址; End Address 终止地址;Size 存储器尺寸;Name 存储器名;Function 功能描述)

验证文档格式可参考《验证文档模板》,内容需要包括:

- 验证说明描述(描述要验证的模块,验证的方案,验证的工具,待验证的功能目标)

- 验证平台架构(包含框图以及子模块基本功能描述)

- 验证模块/芯片端口(使用表格进行描述,表格中需要包含以下内容:Port 端口名;Width 端口位宽;Direction 端口方向; Function 功能描述)

- 验证计划(使用表格进行描述,表格中需要包含以下内容:Test Name 测试名;Test Method 测试方法;Test Target 测试目标)

- 验证用例(使用表格进行描述,表格中需要包含以下内容:Case Name 用例名;Description 用例描述; Implementation 用例的验证激励和验证响应)

测试文档格式可参考《测试文档模板》,内容需要包括:

- 测试说明描述(描述要测试的模块,测试的方案,测试的工具,待测试的功能目标)

- 测试平台架构(包含框图以及子模块基本功能描述)

- 测试模块/芯片端口(使用表格进行描述,表格中需要包含以下内容:Port 端口名;Width 端口位宽;Direction 端口方向; Function 功能描述)

- 测试计划(使用表格进行描述,表格中需要包含以下内容:Test Name 测试名;Test Method 测试方法;Test Target 测试目标)

- 测试用例(使用表格进行描述,表格中需要包含以下内容:Case Name 用例名;Description 用例描述; Implementation 用例的测试激励,预期响应和实际响应)

此外文档需要注明以下信息:

- 文档作者

- 作者联系方式

- 文档版本

- 文档编写日期

若文档存在历史版本,需要说明各版本修改信息。

4. 设计规范

4.1 原理图设计

- 采用层次化设计,优先实现晶体管直接构成的低层级模块电路,高层次模块尽可能使用低层次模块组合完成,注意模块复用性

- 注意原理图中Component的布局,摆放位置、数据流向等需要能够反映layout中的布局情况

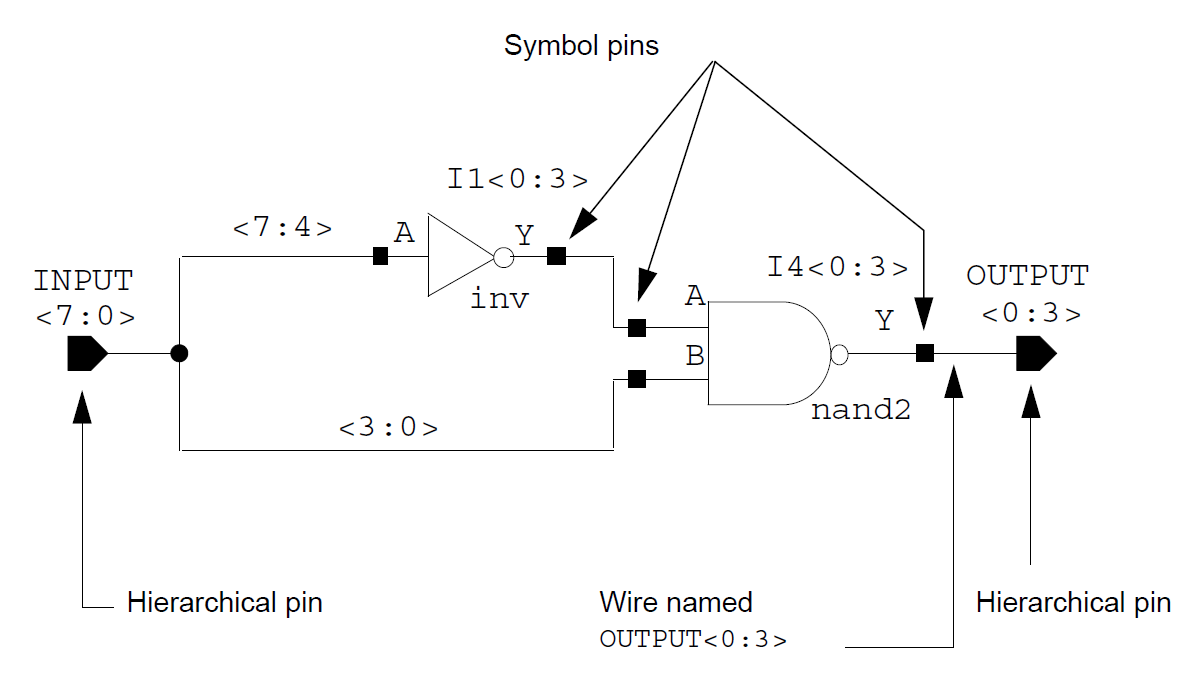

- 大位宽总线/端口优先考虑采用向量表达式声明的方式来实现,例如

A<0:127>,索引一般固定采用低位在前高位在后的方式。小位宽总线可以使用Attach to multiple wires来实现 - 需要大量重复的Component可以使用迭代实例声明的方式来实现重复例化,例如

Ix<0:127>,索引一般固定采用低位在前高位在后的方式 - 使用声明创建总线和Componet时一定要注意匹配连接关系,避免出错,一个例子可参考下图,图中的电路的功能实现了将

INPUT<7:0>的高4位按位取反后,与低四位进行与非,并将输出顺序比特倒序输出,即OUTPUT<0>=!(INPUT<3>&(!INPUT<7>)),OUTPUT<1>=!(INPUT<2>&(!INPUT<6>)),OUTPUT<2>=!(INPUT<1>&(!INPUT<5>)),OUTPUT<3>=!(INPUT<0>&(!INPUT<4>))

- 尽管Virtuoso支持复杂的总线向量声明方式,如下表所示,但在使用时需要高度谨慎,需要考虑到走线时的实现情况,原理图中可以简单实现的大量乱序连接,在版图中实现可能是非常困难的

- 注意原理图完成时进行Save & Check,若无特殊情况,完成的原理图进行Save & Check时不应有Warning/Error

- 积极使用Net Highlighting功能检查连线情况,避免出现漏连/误连

- 管子参数设置时,需要考虑Layout的匹配以及便捷性,避免设置极端的宽长比,可以通过增大finger或者multiplier来增大total width

4.2 版图设计

- 优先使用Layout XL进行版图绘制

- 版图绘制开始前需要进行Floorplan,依次规划:电路形状;电路出Pin;电源连接

- Floorplan时需要重点关注电路出Pin的层次与方向问题,优先考虑大位宽线的走线,尽可能的处理成可以直接竖直或水平出线的情况,从而规避做大规模绕线的工作量

- Placement阶段,管子级电路的布置注意对称性和匹配,版图中添加的dummy需要向原理图中更新

- 模块需要注意高度和关键层次的对齐,尽可能将模块电路都设计成标准单元高度的倍数,从而方便在全定制电路中使用标准单元以及和半定制电路进行集成

- Route时,Metal层尽量采用一层horizen一层vertical的方式进行走线,走线层次注意与其他电路,尤其是半定制电路部分保持一致。此外重点避免在低层金属走折线,以降低DRC风险和避免走线资源浪费

- 确保金属线走在线道(track)上,偏离track会引发走线资源的浪费,导致走线密度下降,track由Metal层最小pitch决定,需要根据工艺规则提前确定

- 混合信号电路,高速电路等关键电路注意添加Guard Ring

5. 电路检查

- 在绘制电路时,优先采用先DRC后LVS的方式,在检查顶层电路时,优先采用先LVS后DRC的方式

- 可在绘制模块电路的每个小步骤完成后进行一次DRC检查,尤其是批量的重复性操作,避免需要修DRC返工

- 进行LVS检查时需要检查LVS Option,一般在进行top最终检查时需要特别注意关闭掉虚拟链接的选项

- 大型电路积极使用Black Box功能进行层次化的检查,便于多个电路绘制工作的并行推进

![[Tools] 使用 HammerDB 对 SQL Server 执行负载测试](https://img2024.cnblogs.com/blog/207361/202504/207361-20250401222114671-276194852.png)