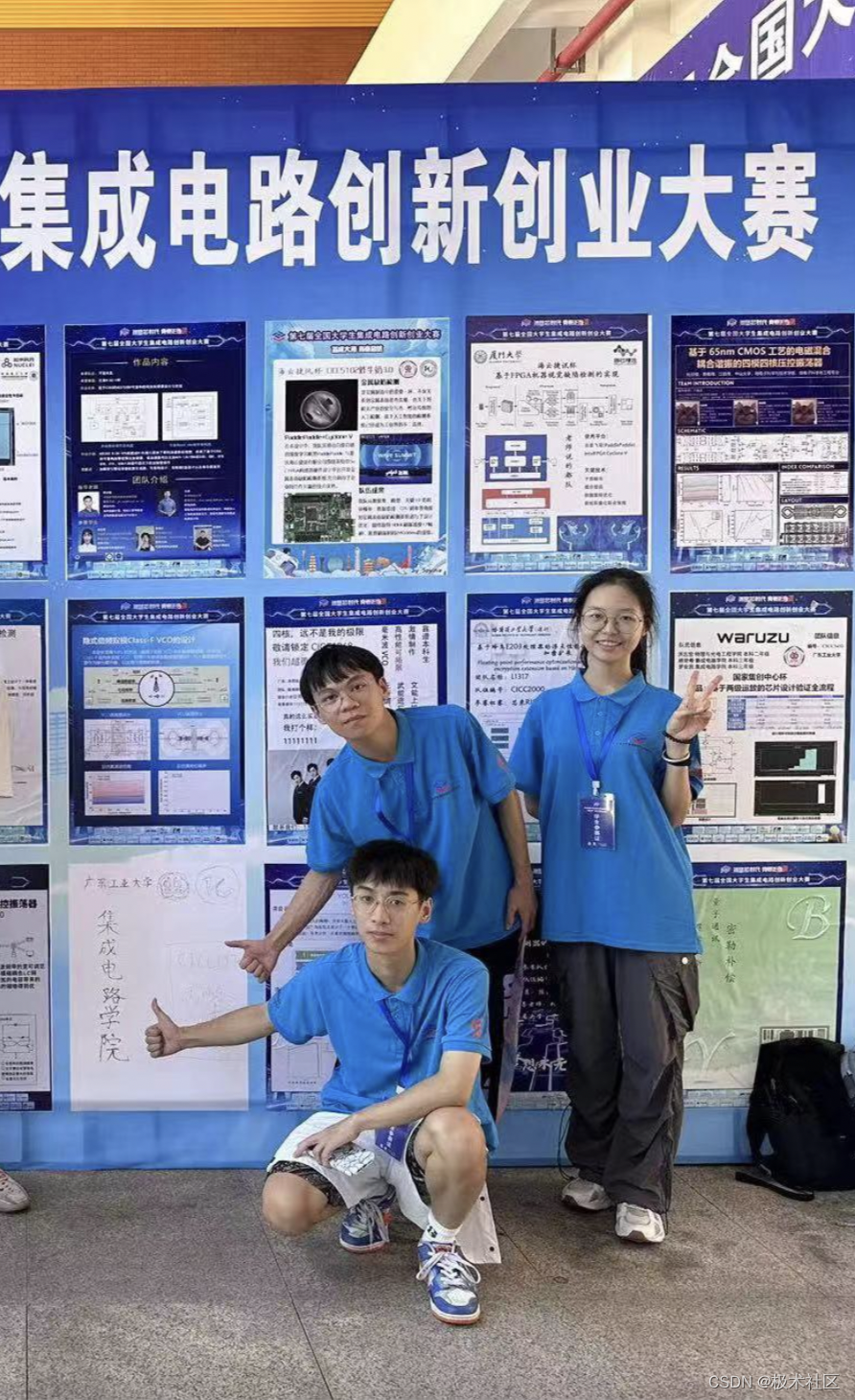

本文为2023年第七届全国大学生集成电路创新创业大赛(“集创赛”)国家集创中心杯三等奖作品分享,参加极术社区的【有奖征集】分享你的2023集创赛作品,秀出作品风采,分享2023集创赛作品扩大影响力,更有丰富电子礼品等你来领!

1.团队介绍

团队院校:广东工业大学

团队名称:Ωranzon

指导老师:张志浩

团队成员:刘鸿宗 程炜 罗锦然

获奖情况:华南赛区一等奖 全国三等奖

2.赛题介绍

以应用于数模混合信号芯片中的运算放大器为对象,完成芯片设计验证的全流程,包括运算放大器的电路和版图设计、设计阶段的前仿和后仿验证、以及对PDK的验证全流程实验。

3.设计要求

- 使用0.18μm工艺进行设计

- 电源电压:1.8V±10%

- 工作温度:①25℃,②0℃至50℃,③-20℃至85℃,④-40℃至+125℃

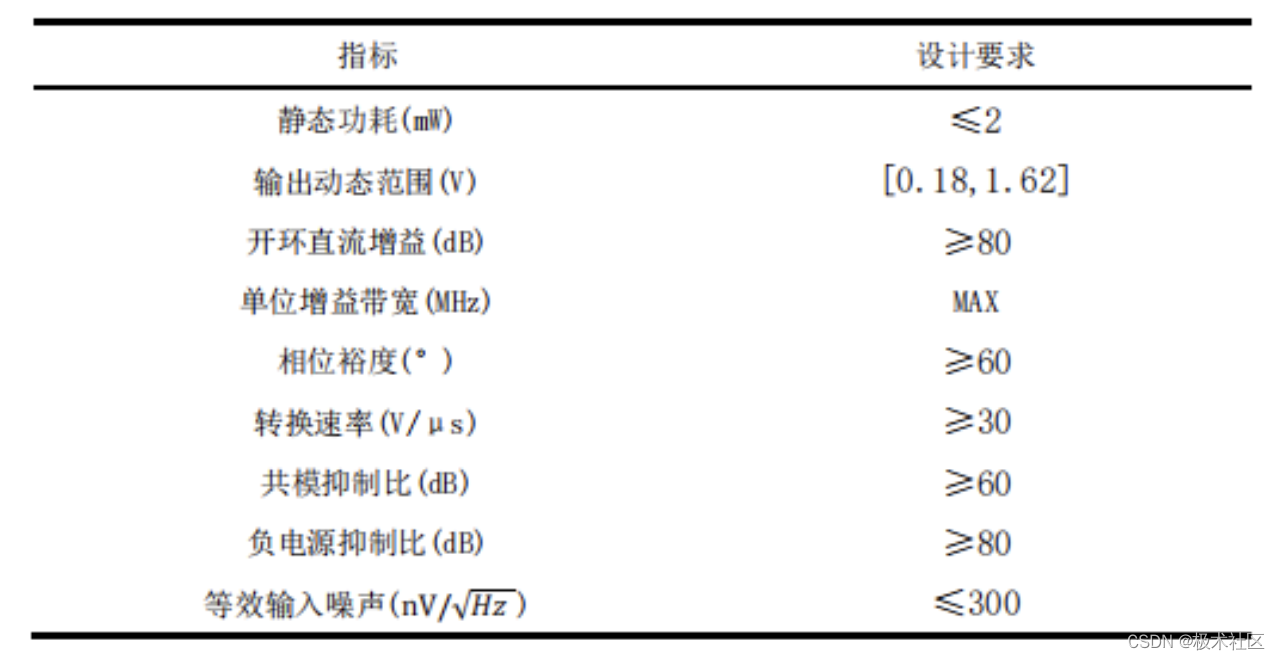

- 详细指标要求:

4.作品特色

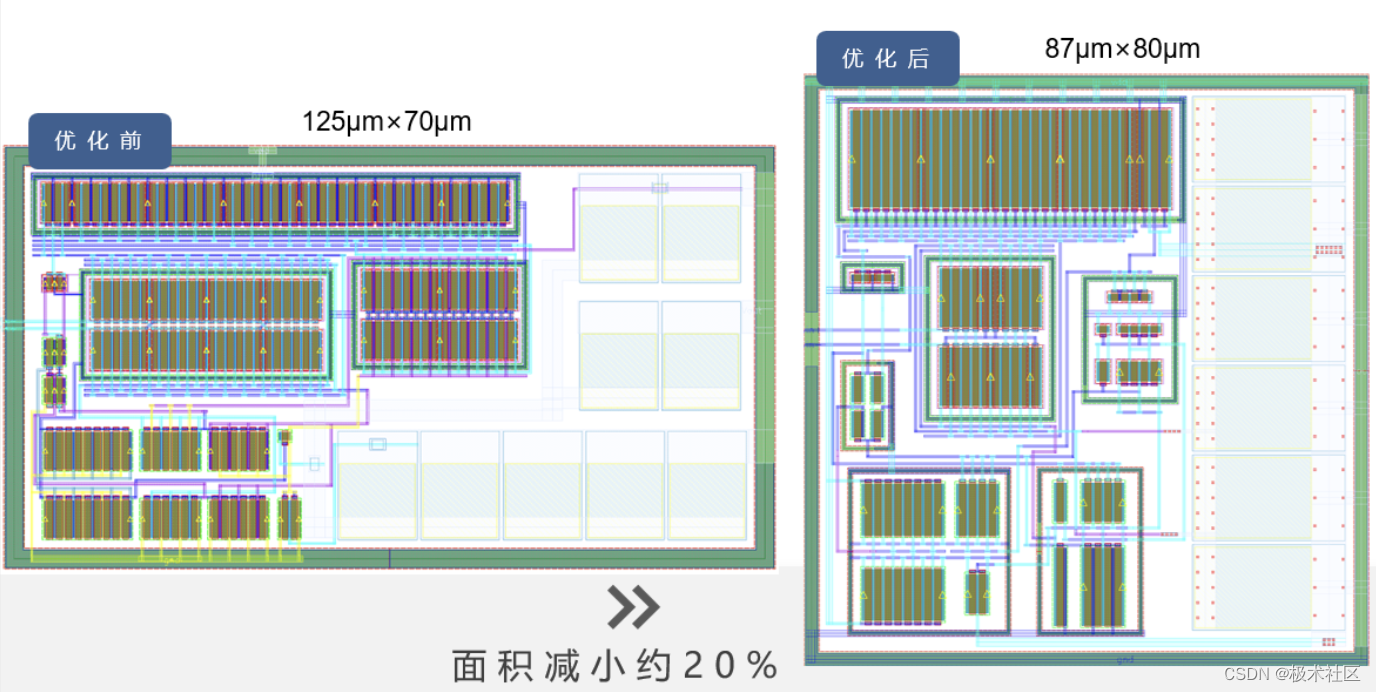

本作品在差分输入单端输出的共源共栅运算放大器基本架构的基础上,大胆尝试了一种新的设计架构,即故意失配的不对称结构。与常规的对称结构相比,节省了大约20%的版图面积以及10%的静态功耗。

5.作品介绍

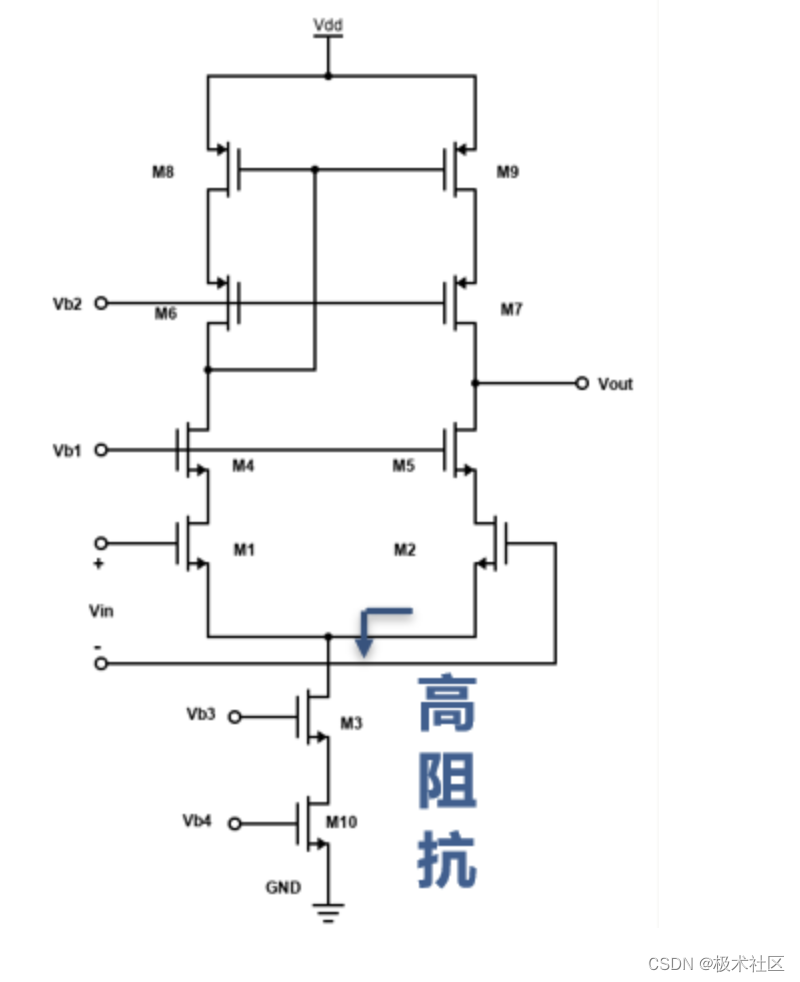

5.1 不对称结构

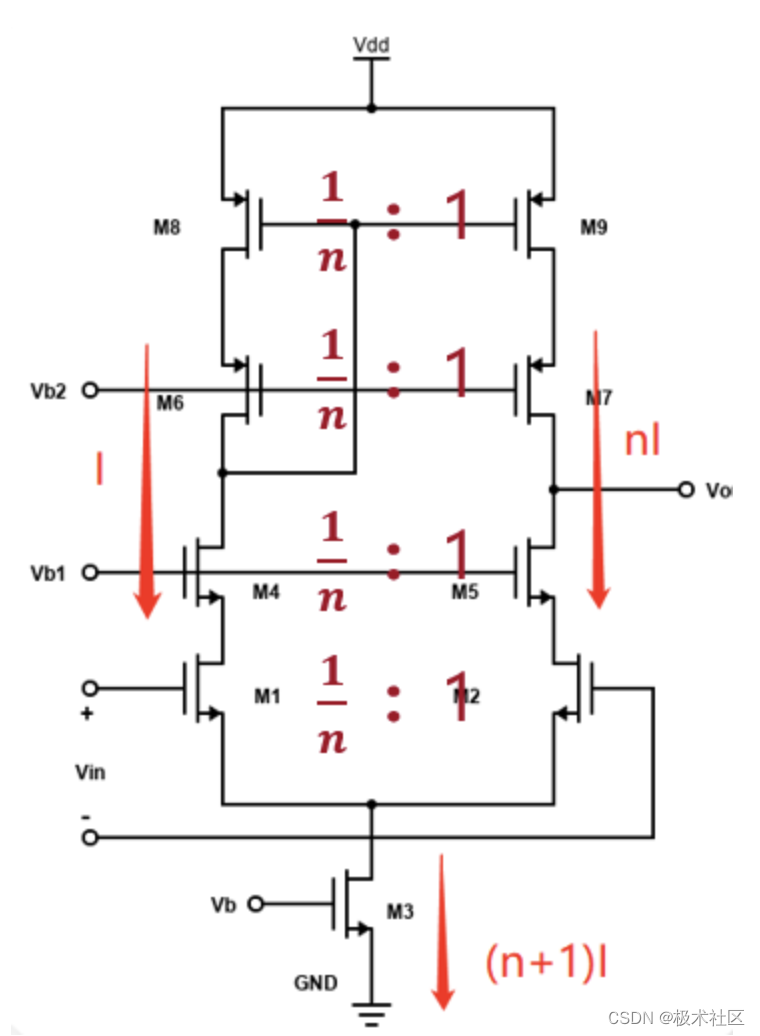

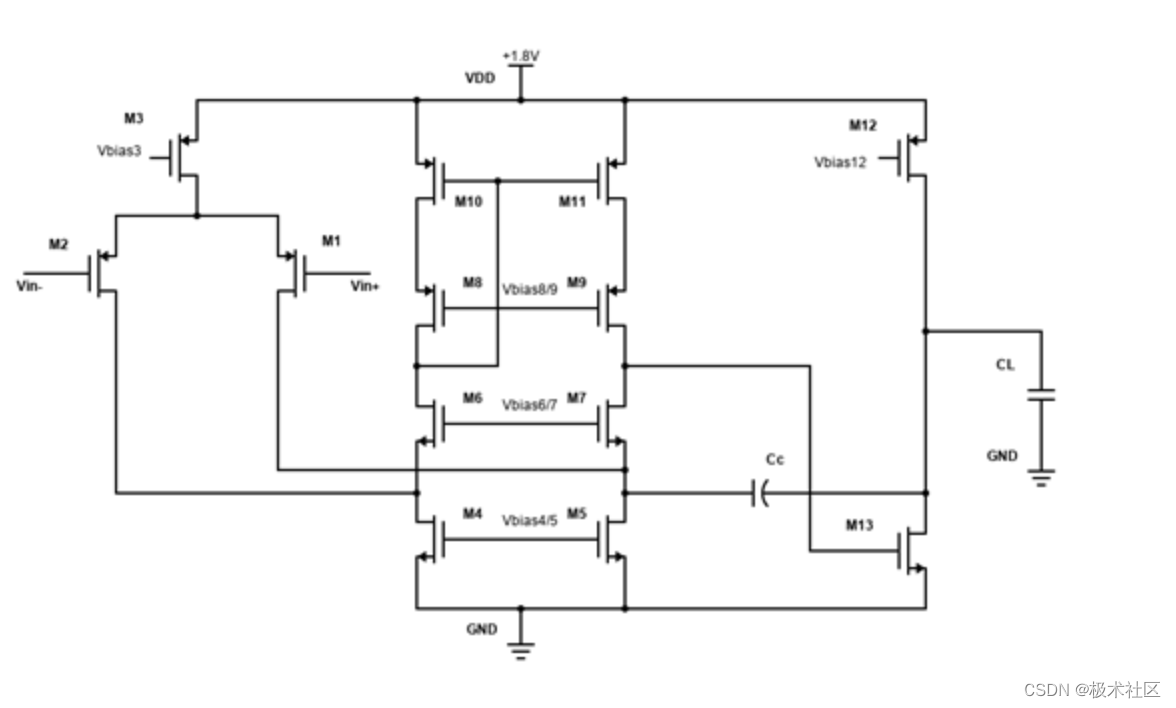

如上图,为运算放大器的主体部分结构。**输出侧采用较大尺寸MOS,非输出侧采用较小尺寸的MOS,**两侧尺寸之比n:1,形成故意失配结构,两侧电流之比也为n:1。

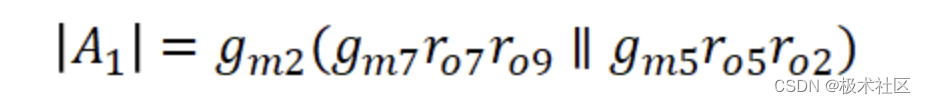

增益由输出侧视入电阻、输入对管跨导确定:

_

_

此表达式与对称结构完全一致!

节省了非输出侧的版图面积以及静态功耗,同时能实现对差分信号的处理。

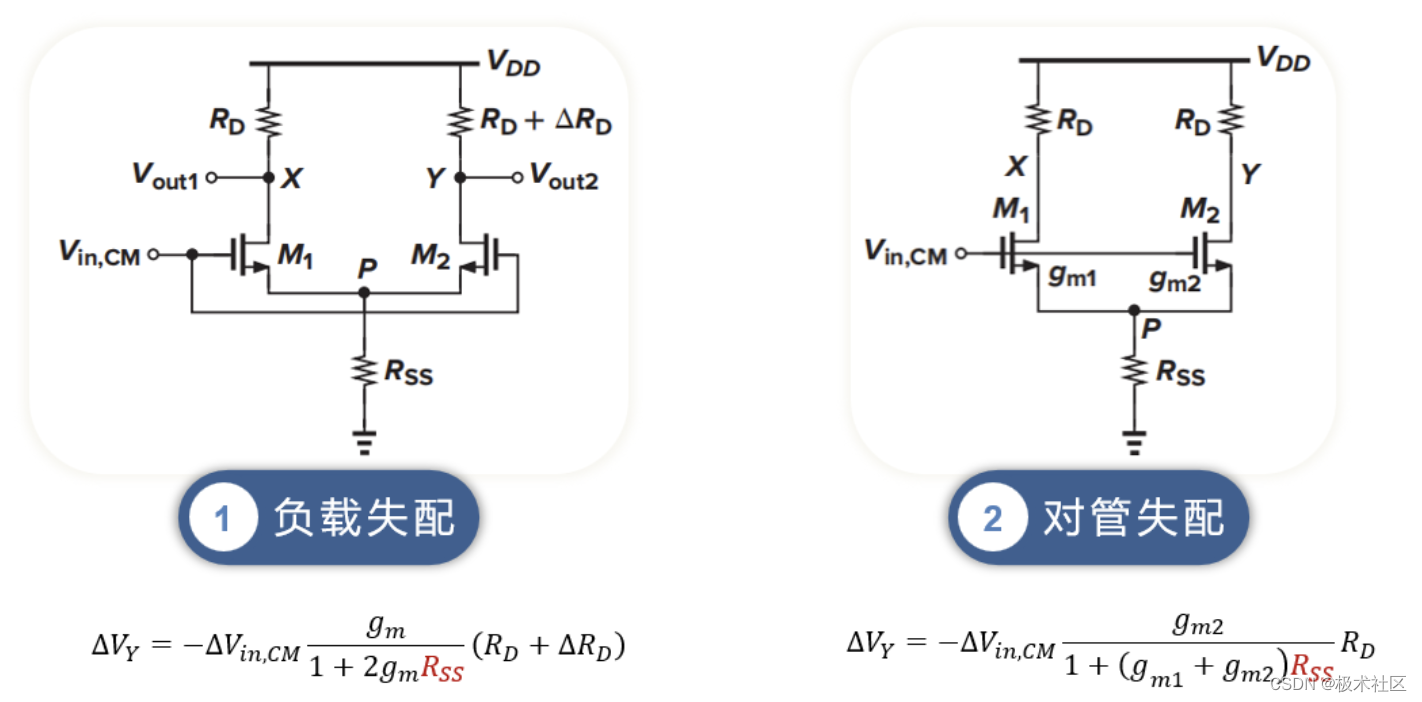

5.2 高等效视入电阻电流源解决共模抑制比的恶化

为了解决故意失配的不对称结构造成的共模抑制比恶化的问题,本团队改进了尾电流源,采用双管堆垛的电流源结构。尾电流源等效视入电阻增加gmro倍,从而同时优化了负载失配以及输入对管失配造成的从共模到输出结点的电压变化。

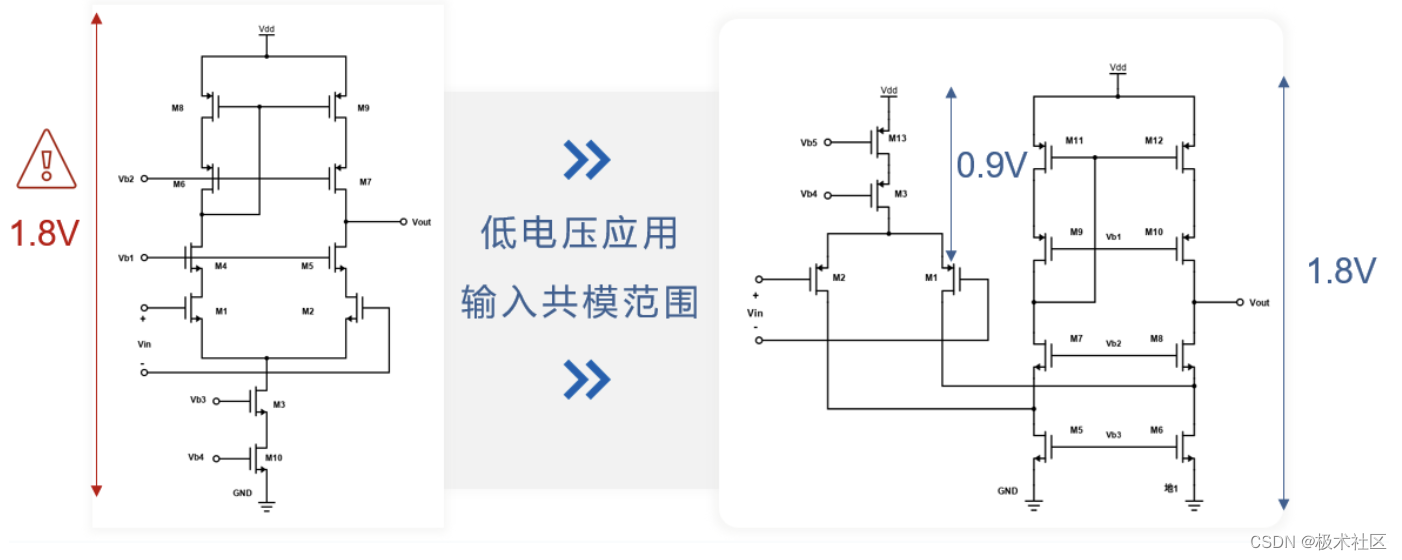

5.3 折叠式结构解决多管堆叠造成的偏置困难

由于采用了共源共栅架构以及上述的双管堆垛的高等效视入电阻尾电流源架构,运算放大器主体部分单条支路上多达6个晶体管,造成偏置困难、工作不稳定的问题。因此,必须采用折叠式输入设计,本团队对运算放大器主体部分做了下图改进。

5.4 Cascode补偿提高带宽

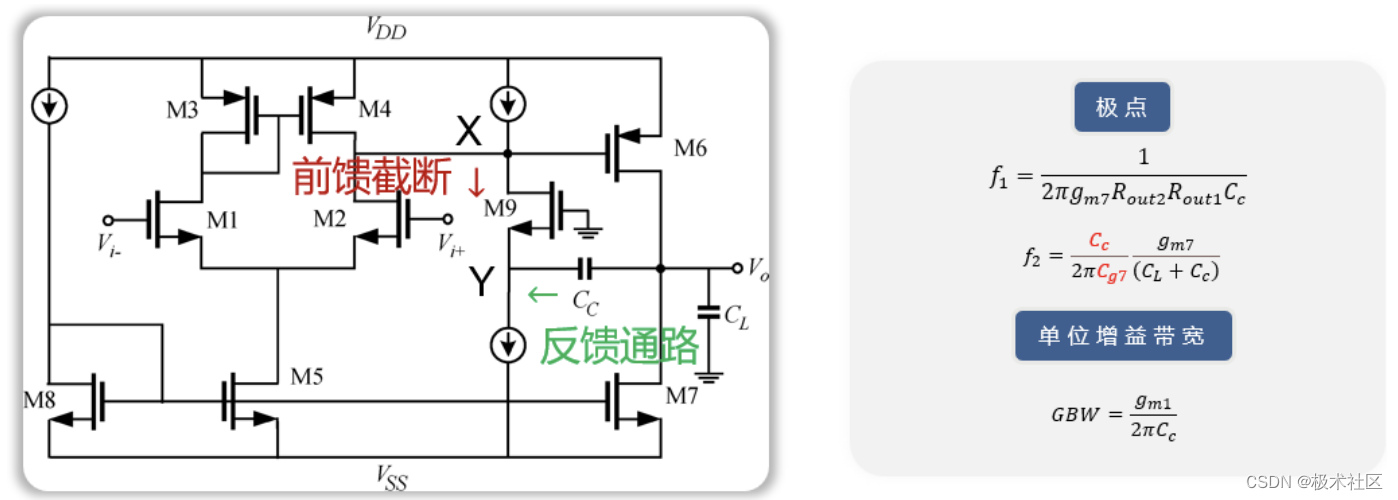

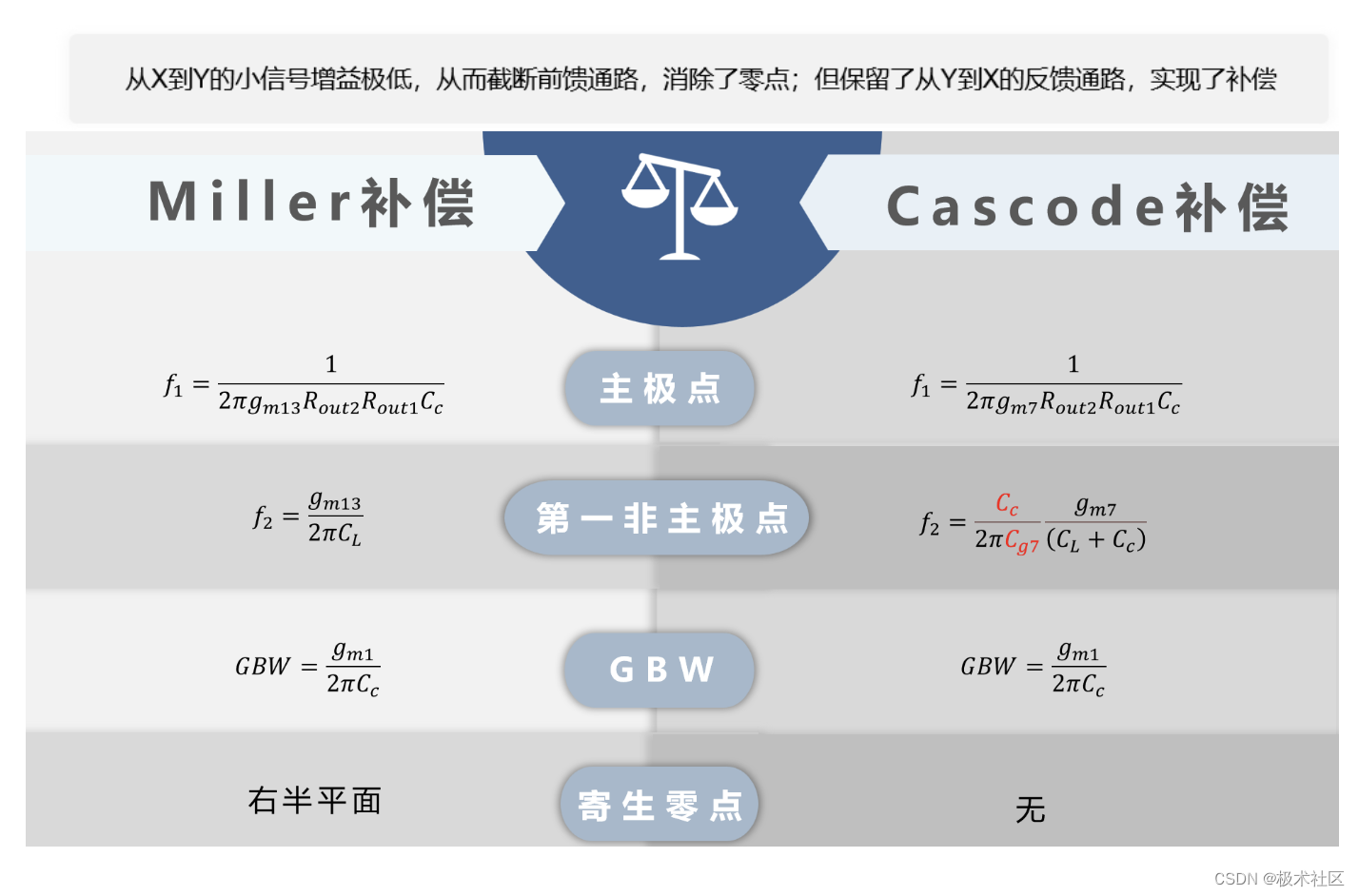

5.4.1 Cascode补偿介绍

Cascode补偿基本结构如下图。与Miller补偿相比,M9截断了从结点X到结点Y的前馈通路,从而消除了零点。同时,与Miller补偿相比,次极点位置也移至更高频率,使得用更小的补偿电容,也具有相当的补偿效果,带宽从而得以提升。

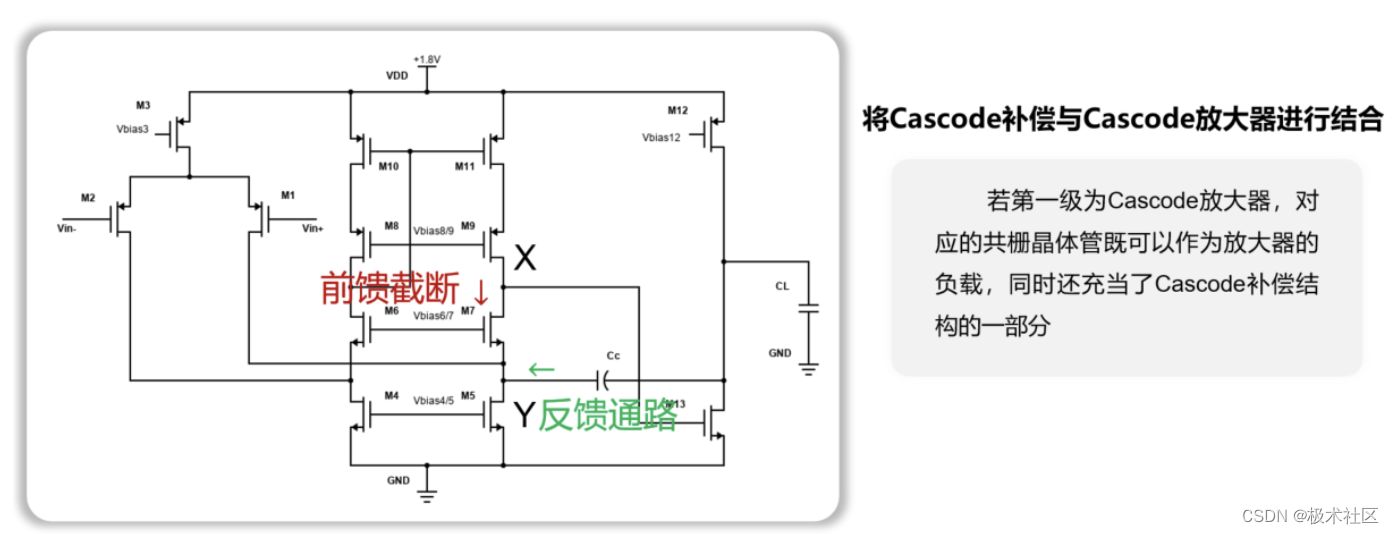

5.4.2 Cascode补偿与共源共栅放大器的结合

结合到运算放大器主体的共源共栅放大器中,Cascode补偿MOS管可以作以下结合:

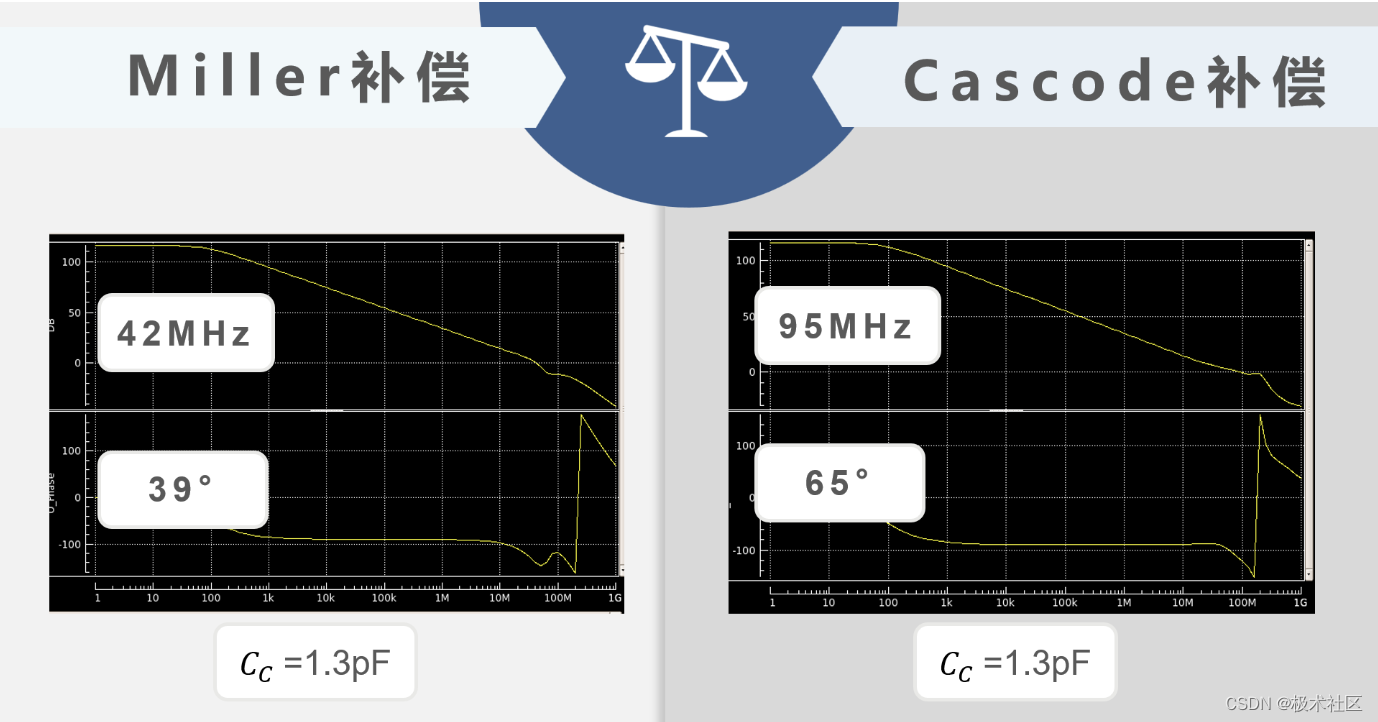

Miller补偿与Cascode补偿仿真对比如下:

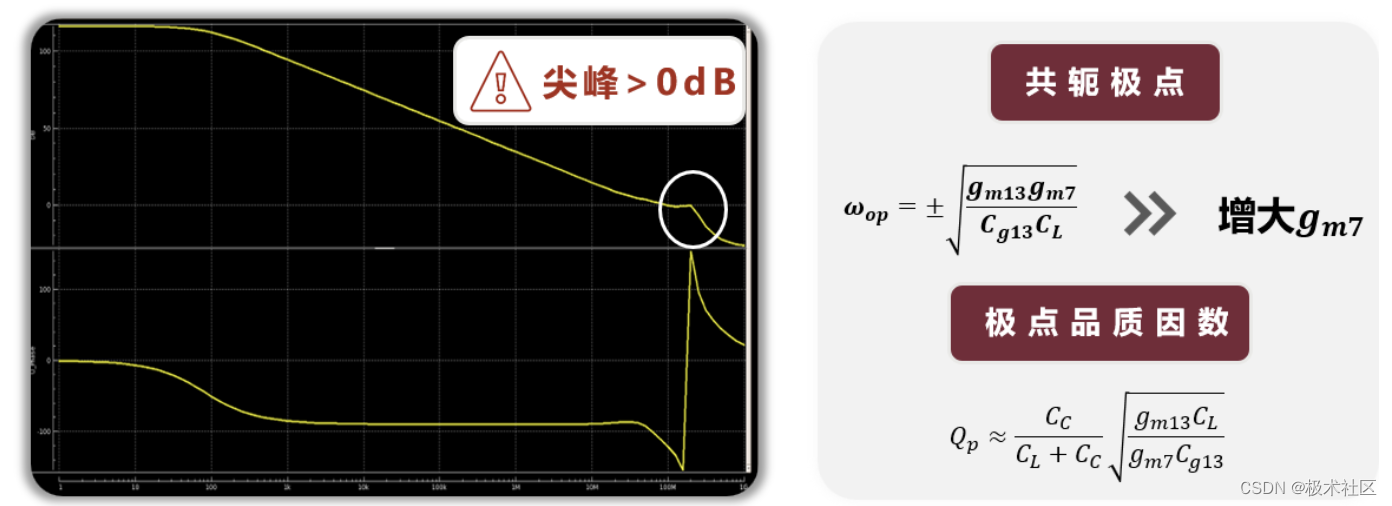

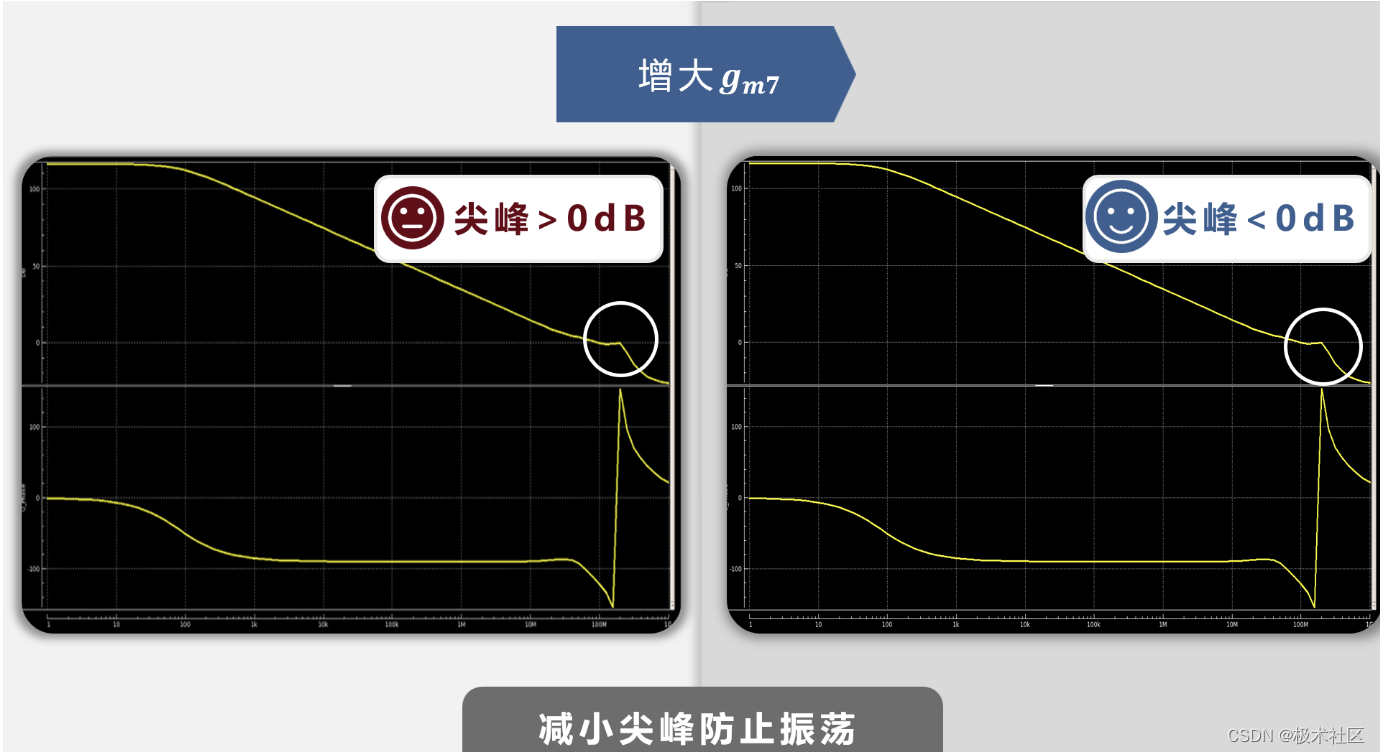

5.4.3 尖峰问题

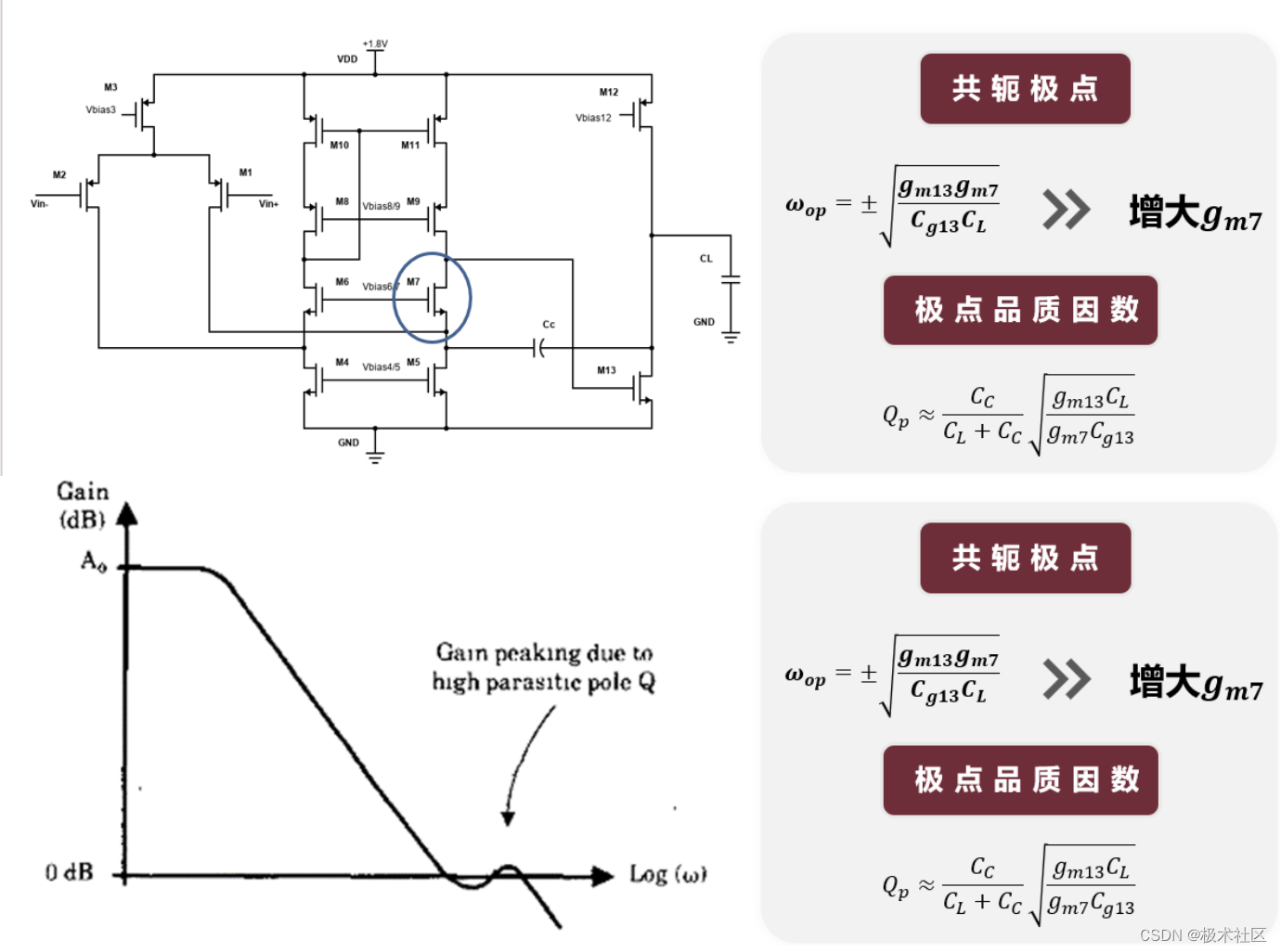

仿真结果显示,Cascode补偿在单位增益带宽外较近的位置产生了尖峰,主要原因是Cascode补偿MOS管M7等效视入电阻并不是无穷大。

由于共轭极点十分靠近单位增益频率,产生的尖峰对系统稳定性影响十分严重,因此需要减小共轭极点产生的尖峰,这需要减小共轭极点的品质因数𝑄𝑝,较小的𝒈𝒎𝟏𝟑/𝒈𝒎𝟕 可以减小𝑸𝒑,从而减小尖峰,因此需要适当增加了M7的栅宽。

改进后尖峰将不再影响运算放大器的稳定性。

6.电路总原理图(省去了偏置电路)

7.版图设计

本作品采用了故意失配的结构,因此讨论版图设计造成的失配没有意义,主要考虑尽可能减小版图面积。与对称结构相比,版图面积减小了约20%。

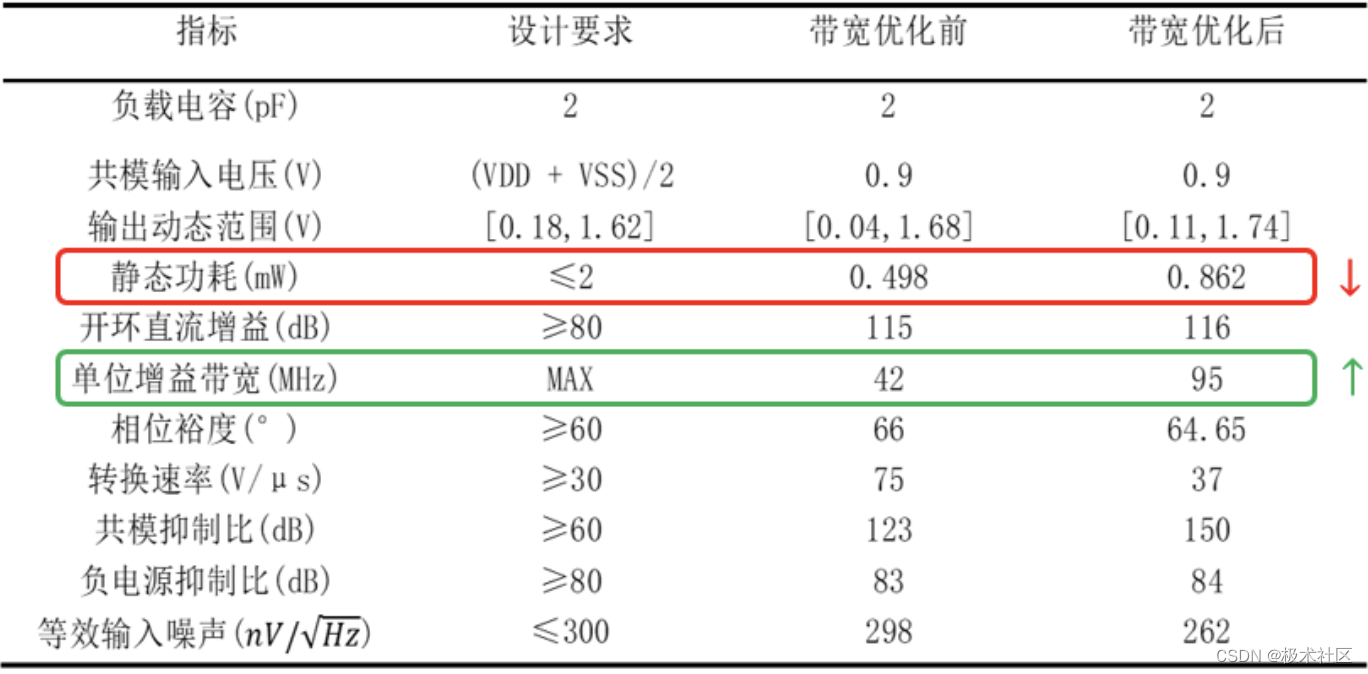

8.指标结果

如下表格给出了运算放大器的后仿指标(在考虑工艺角、工作温度下,只给出了最差指标)

9.问题总结

本作品故意失配的不对称设计暂时无法通过蒙特卡洛仿真,并且本作品的不对称设计在同时考虑取得的收益与产生的代价下在工程上参考意义不大。本作品更多的是展现了一种新的思路,给出了在发现问题的过程中不断解决问题的实践经验。本团队后续将继续总结经验,展现更好的作品。

10.写在最后

笔者水平有限,本文难免存在不当或欠妥之处,请各位读者批评指出。问题交流可通过邮箱1538949225@qq.com或添加微信联系方式:

参加极术社区的【有奖征集】分享你的2023集创赛作品,秀出作品风采,分享2023集创赛作品扩大影响力,更有丰富电子礼品等你来领!

更多集创赛分享作品请关注IC技术竞赛作品分享。