本节不去讨论同步复位与异步复位以及异步复位的reset_release,这些问题可参考:

芯片设计进阶之路——Reset深入理解——cy413026

本机主要回答一下几个问题。

1.片外的reset信号特别是按键reset怎么防止错误抖动的影响?

常见的处理方法包括两种:

- 使用斯密特触发器做IO输入,斯密特触发器有一定的防抖动功能

- 使用de-bounce电路

de-bounce电路原理就是检测到IO输入的信号翻转之后 在多次间隔一定时间检测信号值稳定才会输出这个变化

2.常见soc设计为何把reset_release放在子系统来做?

应该从两个方面来考虑,一个是逻辑设计和软件使用方面;另一个方面从reset网络的物理实现上考虑

对于逻辑设计和软件来讲有几个方面:

- release的时钟太多了,在系统级release就需要把所有的clk拉过去,有些clk甚至是子系统内部的时钟

- 在reset同步的时候 一般会加上软件复位,系统级不方便加这么多软复位,软件也难控制,需要软件知道所有子系统甚至子IP的软件复位时序

对于物理实现来说:

- 把所有系统clk集中放在一个模块 就会有问题,时钟间相互干扰,timing都有问题

- soc这么大的系统来说复位放在一个地方走线到各个复位寄存器也有问题【但本人并不能说明物理实现上的详细影响】

3.异步复位到底要不要时钟和时钟稳定有啥关系

异步复位本身和时钟没有关系,而且没有时钟的时候,直接复位还没有recovery/remove的时序问题,那么为什么要做同步释放?

首先没有时钟的时候,直接异步复位 确实没有recovery/remove的问题,但是不能保证复位的时候没有时钟。

为何很多情况下复位流程是这样的【上电复位】:

- 要求先复位

- 然后打开时钟

- 等到时钟输出稳定在解复位

这里面有几个考虑:

- 首先即使先解复位,由于没有时钟,复位同步电路输出也是不会变的

- 先解复位,后打开时钟,时钟开启不论是门控时钟还是PLL时钟都需要一定的稳定时间,在不稳定的时候不能确认复位同步输出会不会有问题,而且时钟不稳定时候有些数字和模拟逻辑也会出现错误

- 系统中还存在很多无复位寄存器,在复位时候打开时钟,这些无复位寄存器经过几拍时间也会稳定到一定状态

- 考虑EDA仿真,会出现如果解复位之后 在打开clk的情形可能会直接报出寄存器的x态并传播导致后续仿真跑飞

无复位寄存器有些是可以在有clk就可以翻转,复位有效时,经过几拍capture有复位寄存器的复位值就达到了稳定。有clk但受控制信号限制的无复位寄存器,在有了clk后虽然不能capture数据,但经过一段时间自身也会停留在稳定状态。

有一个问题就是系统上电复位的时候PLL还没起来或者lock还需要一段时间,此时如何打开时钟呢? 有些做法就是在这段时间把PLL输出clk mux到晶振输出。

是否一定在异步复位的时候要打开时钟?

其实根据上面的描述,如果不打开时钟对功能没有影响也是可以不开时钟的。

一些观点来自下面论坛。

上电复位同步释放问题 - SOC讨论区 - EETOP 创芯网论坛 (原名:电子顶级开发网) -

4.异步桥,异步fifo该怎样复位

异步FIFO设计与使用

这篇资源中详细写了异步fifo的复位。对于复位或者flush/clear都有相似的要求。如果是对afifo及其相关的外围逻辑都进行复位的话是比较简单的,此时无论afifo是否是空状态,指针是否为0,大家一起复位就是没问题的。

关键在于有些时候 只要求复位afifo本身,下面给出了异步FIFO的flush/clear/reset的一些实现。这几个手段是通用的,但是一般情况下复位不会单独去做逻辑,所以都是靠flush/clear信号来完成的。

4.1 afifo flush/clear

可以考虑为 FIFO 提供单一的清空信号或独立的清空信号(push_flush、 pop_flush)。flush 信号的实现通常为置 FIFO 读写指针的值,使 FIFO 处于 EMPTY 状态下。由于 flush 操作的特殊性,我们通常是根据应用的实际情况考虑 flush 的实现,例如可以规定 flush 操作前后的一些动作。事实上,在实际应用中,当 需要发生 flush 操作时,经常可以满足某些条件,例如 flush 操作前若干个周期不 能有 push 或 pop 操作,flush 操作维持若干个周期等。

4.1.1 一种先从读时钟域flush的操作

AFIFO 的 rflush 的实现仅仅是简单的将 rgnext 赋为 rwptr2 的值,从而可以在 下一个周期有效 empty 信号输出。然后,读指针将通过两级寄存后到达到写时钟 域,输出正确的写时钟域信号。应该注意的是,在 flush 过程中应该保证写时钟 域没有 push 操作,而且 flush 操作需要维持三个慢时钟周期,以确保信号正确的 传递到了写时钟域。代码如下:

if (rflush) rgnext = rwptr2;

else rgnext = (rbnext>>1) ^ rbnext;4.2 afifo 复位

可以考虑实现单一复位信号或独立复位信号。如果实现单一复位信号,则该 复位信号为 FIFO 控制器内部所有寄存器的异步复位信号,同时复位两个时钟域 的寄存器。由于复位信号为完全异步信号(不与任一时钟同步)或与其中一个时 钟同步,无论何种情况,当复位信号有效/无效时,至少有一个时钟域内的寄存 器可能产生 recovery/removal timing violation(即复位信号在该时钟上升沿附近变 化),由此可能产生复位时的不稳定状态。 因此,更合理的做法是分别为两个不同时钟域提供独立的复位信号,或者在内部将某个时钟域的复位信号同步到另一个时钟域后再使用

4.2.1 先clr写时钟域

有一种比较稳妥的做法是 只用一个clr信号输入,然后在另外一个clk domain输出一个clr_done表示clr完成。在这段时间内保证外围逻辑不去读写afifo。

- 输入wrclk的wr_clr信号

- 用wr_clr信号clr本时钟域逻辑,同时产生wr2rd_clr信号并同步至rd_clk

- rd_clk域检测到同步过来的clr信号开始clr

- wrclk检测到从rdclk同步过来的rd_ptr==0,说明rdclk已经完成clr,此时清除wr2rd_clr

- rdclk检测到wr2rd_clr的同步信号已经清零且wr_ptr==0 就认为afifo已全部clr完毕,输出clr_done信号

实际上从上面的描述来看clr信号是从wrclk输入还是rdclk输入,都可以完成clr操作。这一段描述明显要求不能再clr期间操作afifo

5.部分逻辑复位会不会影响外围逻辑

这个其实就是典型的RDC问题。常见在总线模块对某些master逻辑复位,不能影响其他master的通路

一般这种情况下会有一个reset保护电路,把边界信号clamp到不影响别的通路值。其实无论这个边界有没有做异步处理,都需要做clamp,因为这部分电路的复位会产生两个影响:

- 毛刺

- 不满足外围逻辑的setup/hold的信号翻转

6.RDC reset domain cross要做什么

什么是reset domain cross?

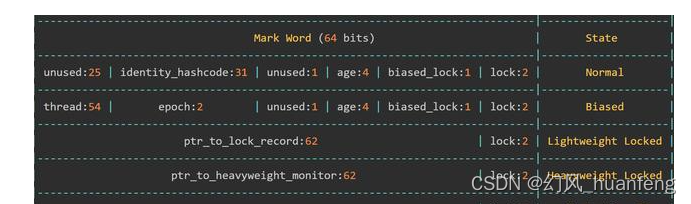

经过reset_0_n复位的信号被其他复位域 reset_1_n的寄存器capture的时候就会出现亚稳态的风险

这种情况的常见处理方式如下:

- reset assert order---也就是通过控制reset的顺序能够解决很多问题

- reset-clamp----复位钳位,在复位之前把cross的path输出钳位到需要的值,也就是isolation和不同power domain边界isolation作用一致

- clk 隔离----就是把会受到影响的复位域的寄存器的clk关掉

具体可参考另外一篇文章:

RDC(reset domian cross)复位跨域-CSDN博客

7.异步复位树是什么样的结构

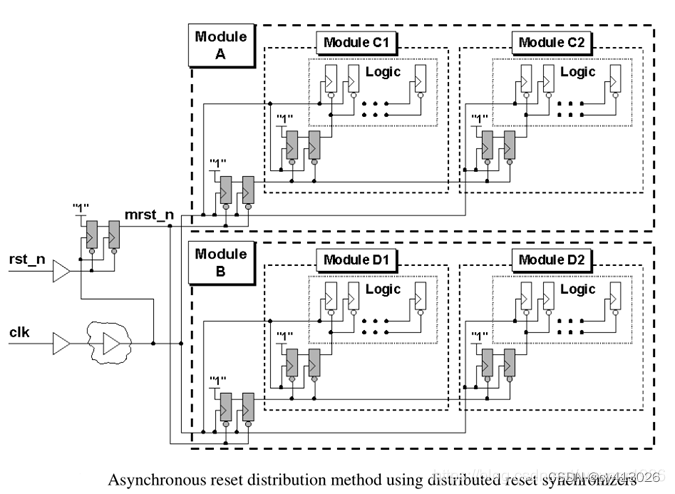

异步复位树是由一级一级的复位同步逻辑构成的,即每个层级都加上一个异步复位同步器。如下图所示: