接上一部分,AD9361 数字接口CMOS &LVDS&SPI

目录

- 一、LVDS模式数据路径和时钟信号

- LVDS模式数据通路信号

- [1] DATA_CLK

- [2] FB_CLK

- [3] Rx_FRAME

- [4] Rx_D[5:0]

- [5] Tx_FRAME

- [6]Tx_D[5:0]

- [7] ENABLE

- [8] TXNRX系列

- 二、LVDS最大时钟速率和信号带宽

一、LVDS模式数据路径和时钟信号

LVDS MODE DATA PATH AND CLOCK SIGNALS

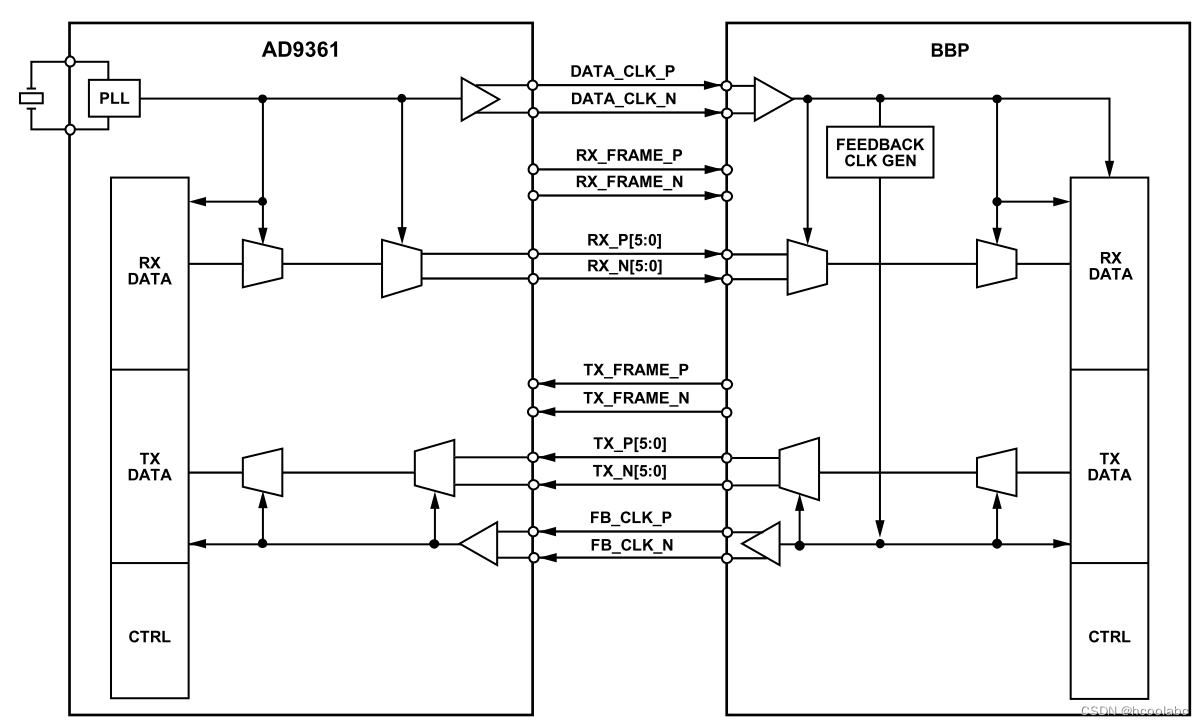

以下介绍AD9361数据路径在低压差分信号(LVDS)模式(ANSI-644)下的工作情况。AD9361数据通路接口使用并行数据总线(P0和P1)在AD9361和BBP之间传输采样数据。总线传输使用简单的硬件握手信号进行控制。在LVDS模式下,两条总线均遵循差分LVDS信号。

AD9361使用 LVDS接口方便的连接到具有LVDS接口的ASIC或FPGA。LVDS接口通常用于系统在嘈杂环境中需要卓越的开关性能以及比标准CMOS接口更高的数据速率的情况。使用LVDS模式时,建议将所有走线长度保持在不超过30厘米,并使差分走线紧密相连且长度相等。

LVDS模式数据通路信号

LVDS MODE DATA PATH SIGNALS

数据接口由以下信号组成。

[1] DATA_CLK

DATA_CLK是在AD9361中产生的差分LVDS信号,并作为Rx数据路径的主时钟提供给BBP。BBP使用此主时钟作为接口数据传输和采样数据基带处理的时序参考。DATA_CLK在接收操作期间为 Rx_D[5:0] 信号提供源同步时序和 DDR 操作。

SDR 在 LVDS 模式下不可用。

DATA_CLK频率取决于系统架构(射频通道数、过采样程度和带宽模式)。该频率通过SPI写入AD9361来设置。

AD9361可以在接口空闲期间停止DATA_CLK(响应来自BBP的SPI事务),以降低功耗。如果禁用DATA_CLK,则与非切换状态的转换必须符合电气层对干净信号转换的要求,并且AD9361必须始终驱动有效电平。

[2] FB_CLK

FB_CLK是由BBP驱动的差分LVDS信号,是DATA_CLK的反馈(回环)版本。 FB_CLK在Tx突发期间为Tx_D[5:0]信号提供源同步时序和双边沿捕获。

FB_CLK可在接口空闲期间由BBP停止,以降低功耗。如果是这样,则与非切换状态之间的转换必须遵守干净信号转换的电气层要求,并且必须始终由BBP驱动有效电平。

[3] Rx_FRAME

Rx_FRAME是由AD9361驱动并提供给BBP的差分LVDS信号,用于对AD9361提供的采样数据进行成帧。上升沿表示帧的开始。Rx_FRAME可以设置为突发开始时的单个高电平转换,并在整个突发过程中保持高电平,也可以设置为在每帧开始时具有上升沿的脉冲序列(50% 占空比)。

[4] Rx_D[5:0]

Rx_D[5:0] 是由 6 个差分对组成的差分 LVDS 数据总线。它通过接收到的数据从AD9361驱动至BBP。数据在该总线上以成对的数据字传输,以创建 12 位数据总线。

[5] Tx_FRAME

Tx_FRAME是由BBP驱动的差分LVDS信号,并提供给AD9361,以对BBP提供的采样数据进行成帧。上升沿表示帧的开始。Tx_FRAME可以接受突发开始时的单个高电平转换,该跳变在整个突发期间保持高电平,或者接受在每帧开始时具有上升沿的脉冲序列(50% 占空比)。

AD9361发送零数据(全部为零),直到第一个Tx_FRAME指示有效数据。当 Tx 路径在 FDD 独立模式下完成传输操作并且数据路径不会自动刷新时,这是一个有用的功能。在这种情况下,可以将TX_FRAME引脚保持低电平以完成数据刷新操作。有关详细信息,请参阅“启用状态机指南”部分。

请注意,Rx_FRAME 和 Tx_FRAME 都是接口正常运行所需的信号。

[6]Tx_D[5:0]

Tx_D[5:0]是由六个差分对组成的差分LVDS数据总线。它从BBP驱动至AD9361,数据通过发送器输出。数据在该总线上以成对的数据字传输,以创建 12 位数据总线。

[7] ENABLE

ENABLE从BBP驱动至AD9361,以在TDD模式下提供数据传输突发控制(以及TXNRX)。ENABLE 由 BBP 断言至少一个DATA_CLK周期,以指示每个突发的开始。随后,在至少一个DATA_CLK周期内第二次置位,以指示每次突发的结束。

AD9361在内部跟踪ENABLE脉冲序列,以便将每个脉冲正确解释为每个突发的开始或结束。ENABLE信号也可以配置为电平模式,在这种模式下,信号的状态(非脉冲)决定了ENSM何时在状态之间移动。在LVDS模式下,数据端口始终处于活动状态。在TDD模式下,BBP和AD9361都会忽略非活动方向的数据。开始和结束延迟(AD9361采样的ENABLE脉冲与总线上存在第一个和最后一个有效数据采样之间的延迟)因数据路径配置而异。Rx_FRAME和Tx_FRAME信号分别用于确定BBP和AD9361的有效数据。FB_CLK信号用于对该输入进行采样。

在FDD模式下,ENABLE信号用作单个控制输入,以确定ENSM的状态。还有另一种FDD模式,在这种模式下,ENABLE信号可以重新定义为RxON,这是ENSM的直接硬件控制输入,用于控制Rx功能。在这种模式下(称为FDD独立控制模式),BBP独立控制Rx功能,可以节省功耗。

[8] TXNRX系列

TXNRX从BBP驱动至AD9361,并在ENSM处于TDD模式时提供数据传输突发控制(以及ENABLE)。当AD9361对ENABLE进行高电平采样以启动突发时,也会对TXNRX上的电平进行采样以确定数据方向。在 TDD 模式下,TXNRX 采样高电平表示发送突发,TXNRX 采样低电平表示接收突发。

TXNRX信号电平必须在整个数据传输突发期间保持(有效的逻辑电平)。TXNRX信号可以在对ENABLE起始脉冲进行采样之前建立任意数量的周期(≥ 0),也可以在对ENABLE结束脉冲进行采样后更改任意数量的周期(≥ 0)。需要注意的是,TXNRX信号只有在ENSM处于ALERT状态时才应改变状态,因为TXNRX上升沿和下降沿直接在TDD模式下对相应的频率合成器进行上电和断电。

在正常FDD模式下,TXNRX信号被忽略,但必须保持在有效的逻辑电平。还有另一种FDD模式,在这种模式下,TXNRX信号可以重新定义为TxON,这是ENSM的直接硬件控制输入,用于控制Tx功能。在这种模式下(称为FDD独立控制模式),BBP独立控制Tx功能,从而节省功耗。

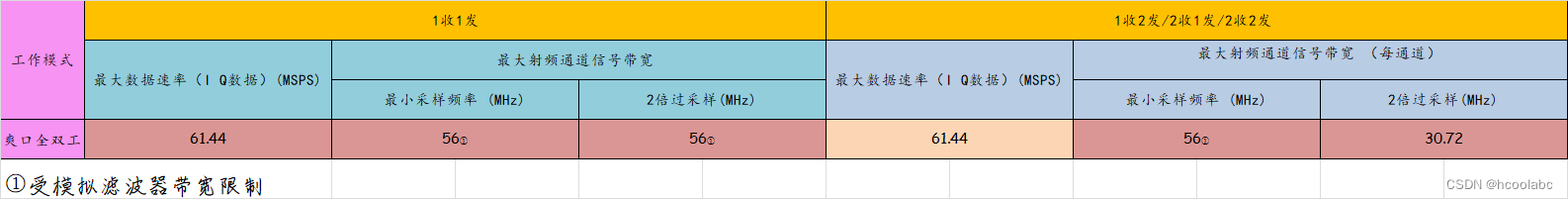

二、LVDS最大时钟速率和信号带宽

LVDS MAXIMUM CLOCK RATES AND SIGNAL BANDWIDTHS

下表列出的数据比较了LVDS数据总线配置在不同允许工作模式下的最大数据时钟速率和信号带宽。列出了两种情况下的最大射频带宽:使用避免混叠的最小采样率进行采样,以及使用 2× 过采样进行采样。每种模式的详细信息将在后续中给出。在LVDS模式下,最大DATA_CLK速率提高到245.76 MHz。该时钟和56 MHz最大模拟滤波器带宽限制了RF信道信号带宽。请注意,TDD 和 FDD 模式的数据总线时序是相同的,因为每条路径(发送和接收)都有一条专用总线。

参考源文件 :《UG-570 AD9361 Reference Manual 》

参考源文件 :《UG-671 AD9361 Register Map Reference Manual》

![[架构之路-246/创业之路-77]:目标系统 - 纵向分层 - 企业信息化的呈现形态:常见企业信息化软件系统 - 客户关系管理系统CRM](https://img-blog.csdnimg.cn/61af882f7b4d4b909da892621925d0d0.png)