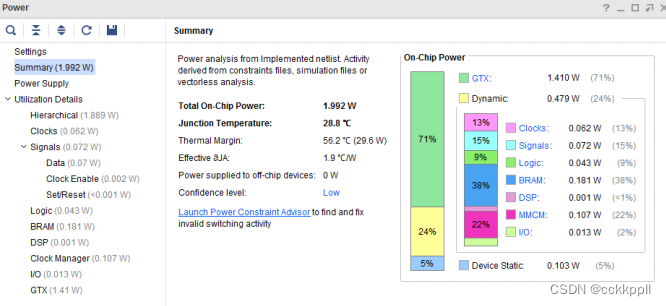

在布线后会生成“ Power Report ” ( 功耗报告 ), 它基于当前器件工作条件和设计的切换率来报告功耗详情。功耗分析要求网表已完成综合或设计已完成布局布线。

• set_operating_conditions 命令用于设置工作条件。

• set_switching_activity 命令用于定义切换活动。

当“综合后设计”或“实现后设计”打开时 , 即可使用“ Report Power ”命令。

“ Power Report ”可用于基于设计输入来估算功耗 , 包括 :

• 散热性能统计数据 , 例如 , 结温和环境温度值。

• 有关开发板选项的数据 , 包括开发板层数和板上温度。

• 有关设计所使用的气流和散热器资料的选择数据。

• 报告来自不同电源的 FPGA 电流要求。

• 支持执行详细的配电分析 , 提供省电策略相关指南 , 并减少动态功耗、散热功耗或片外功耗。

• 可使用仿真活动文件来提升功耗估算的准确性。

1、分析功耗报告

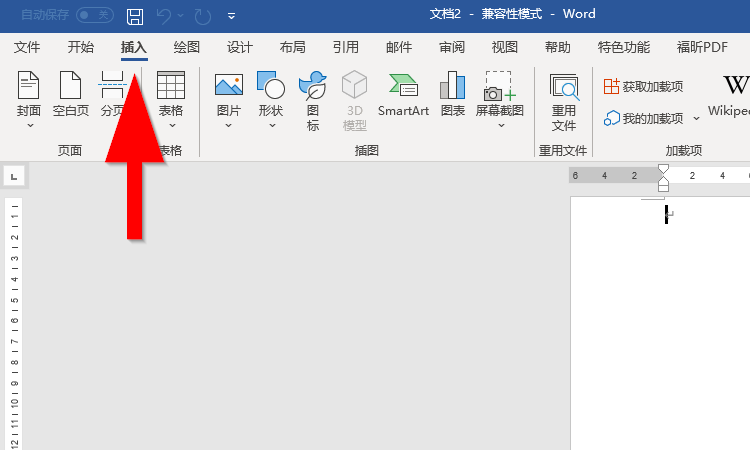

“ Report Power ” ( 功耗报告 ) 对话框 ( 请参阅下图 ) 可用于根据以下条件分析功耗 :

• 设置

• 总功耗

• 层级

• 电压轨

• 块类型

2、非工程流程中的功耗报告

在非工程流程中 , 完成 link_design 或 synth_design 后即可使用 report_power 。生成的报告使用可用布局布

线来提供更准确的功耗数值。要从 Tcl 控制台或脚本生成此报告 , 请运行 report_power 。

3、Report RAM Utilization

“ Ram Utilization ” ( RAM 使用率 ) 报告可帮助您分析专用 RAM 块 ( 例如 , URAM 和块 RAM ) 以及分布式 RAM 原 语的使用率。默认情况下, 此报告覆盖整个设计 , 但可通过 -cell 开关将其限制于特定层级。此报告可在综合后以及任意实现步骤后生成, 但只能通过 Tcl 命令行查看。

“ RAM Utilization ”报告对于由 Vivado 综合推断所得存储器最有效 , 因为您可将“ RTL Memory Array ” ( RTL 存储器阵列) 与 FPGA 中的实际物理实现进行比较。

此报告可显示如下内容 :

• 每个存储器原语的使用率

• 阵列大小和维度 ( 仅限推断 )

• 存储器的类型

• 存储器原语的使用率

• 所需的存储器性能

• ( 可选 ) 存储器的流水线使用率 ( 如适用 )

• 始于和止于存储器的最差情况逻辑路径

• 功耗效率数据 , 例如 , 级联和使能率

4、Report Control Sets

控制集表示时钟信号、时钟使能信号和置位 / 复位信号的唯一组合。每个 slice 都支持有限数量的控制集 , 以供位于其中的触发器组合使用。根据所使用的架构, 部分控制集允许在 slice 内共享。用户应熟悉目标系列的“ Configurable Logic Block” ( 可配置逻辑块架构 ) 才能理解兼容性规则。

报告主要包含以下 2 部分 :

1. 控制集的绝对数量。任意给定器件中控制集的有限数量。超出建议的控制集数量可能对 QoR 造成不利影响。

2. 控制器的负载剖析。需减少控制集时 , 减少包含少量负载的控制集数量最有效 , 因为这给设计增加的逻辑量最少。

5、Report High Fanout Nets

report_high_fanout_nets 命令用于分析网表并报告具有最高扇出的信号线。此命令可在综合后、布局后或布线后网表上运行。但在布局前, 此报告无法传递时钟区域和 SLR 信息。此报告可显示以下信息 :

• “ Fanout ” ( 扇出 )

• “ Driver Type ” ( 驱动程序类型 )

• “ Load Types ” ( 负载类型 )

• “ Clock Regions ” ( 时钟区域 )

• “ SLRs ” ( SLR )