CDC 拓扑结构的简化板级原理图

以下部分展示了 CDC 拓扑结构的简化板级原理图以及简要说明。在所有板级原理图中 , 源时钟信号线 ( 通常为 clk_a) 以蓝色高亮 , 目标时钟信号线 ( 通常为 clk_b ) 以橙色高亮。

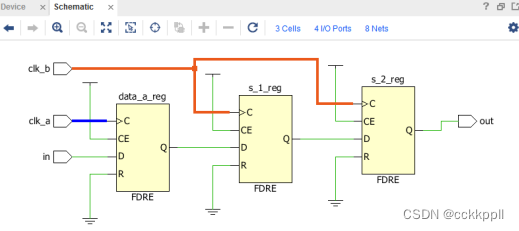

单比特同步器

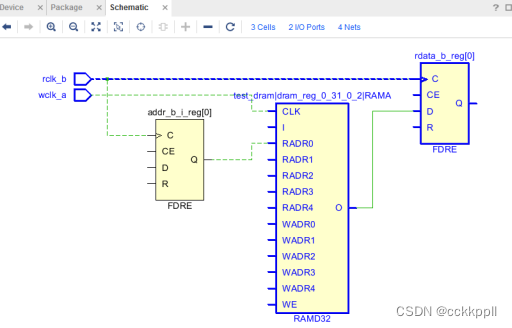

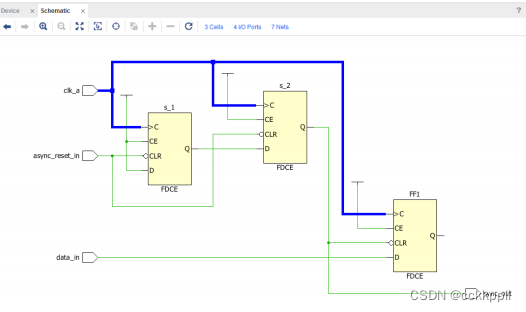

下图显示了单比特同步器的简化拓扑结构。 ASYNC_REG 属性必须至少设置在同步链的前 2 个触发器上。同步器深度由共享相同控制信号的已链接的触发器数量来定义。

如果触发器的 CLEAR 或 PRESET 管脚同时连接到异步源 , 那么此同步器在报告中仅显示为单比特同步器而非异步复位同步器。

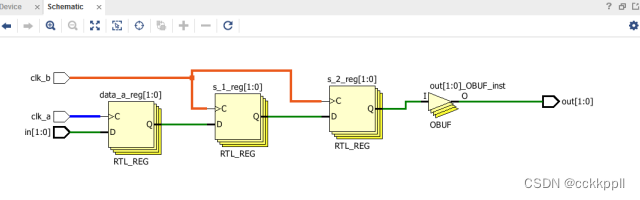

多比特同步器

检测到的多比特同步器等同于根据起点 / 端点名称和匹配的 CDC 规则将多个单比特同步器分组在一起。在此情况下 ,总线由起点和端点单元名称( 而不是信号线名称 ) 来定义。标准总线名称格式为 baseName[index] 。此外 , 起点与端点索引必须匹配。下图显示了位宽为 2 的多比特同步器示例。

如果 CDC 总线的某些位不匹配相同 CDC 规则 , 那么该总线将以单个位或总线分段的形式来报告 , 这些单个位或总线分段都具有匹配相同 CDC 规则的连续索引。必须明确的是, 在总线上采用基于寄存器的同步器并不能确保总线跨域的安全性。因此 , 鉴于工具无法判定拓扑结构是否足以满足设计, CDC 规则 CDC-6 归类为“ Warning ” ( 警告 ) 。 CDC 的安全性由设计人员判定。 如果总线采用格雷编码, 那么只要在总线上设置充足的时序约束以确保接收域每次最多只能捕获一项数据 , 在总线的所有位上使用基于寄存器的同步器的安全性即可得到保证。如果总线并未采用格雷编码, 则应改为使用其他同步器拓扑结构 , 例如 , CE 控制的 CDC 或 MUX 控制的 CDC 。

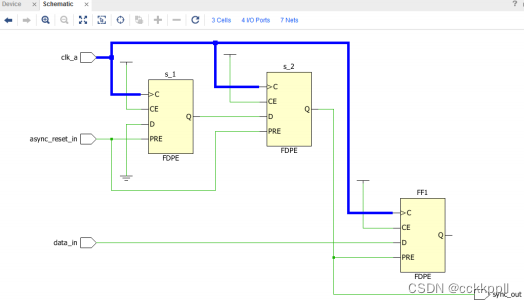

异步复位同步器

在下图中显示了基于 CLEAR 同步的异步复位同步过程 , 后一张图中显示了基于 PRESET 同步的异步复位同步过程。FF1 单元分别连接到已同步的清除 (CLEAR) 信号或预置 (PRESET) 信号 , 可根据 clk_a 以安全方式对这两个信号的断言无效进行时序约束。请注意, 在异步复位同步器内不得混用含 CLEAR 和 PRESET 的触发器。

通常建议避免在目标时钟域内包含多个复位信号的同步。这意味着从源时钟域到目标时钟域的复位不应存在任何扇出。此建议可防止目标时钟域在不同时间解复位从而导致设计处于未知状态。不遵循此建议会导致从发送触发器到目标时钟出现严重的 CDC-11 扇出违例。 但在某些涉及 FIFO Generator IP 的场景中 , 可在目标时钟域内安全进行多次复位信号同步。 FIFO Generator 将异步进入复位状态, 并脱离同步。它会对块 RAM 应用真正的同步复位 , 但 FIFO 会收到异步复位。只要设计使用逻辑的wr_rst_busy 信号来保持数据流 , 就不会出现部分逻辑解复位而部分逻辑仍处于复位状态的状况。AXI 接口使用 5 个 FIFO Generator IP 来同步每个目标时钟域中的复位 , 这也是构造安全的复位电路的另一个示例。在可放心对复位信号进行多次同步的场景中, 可忽略 CDC-11 违例。

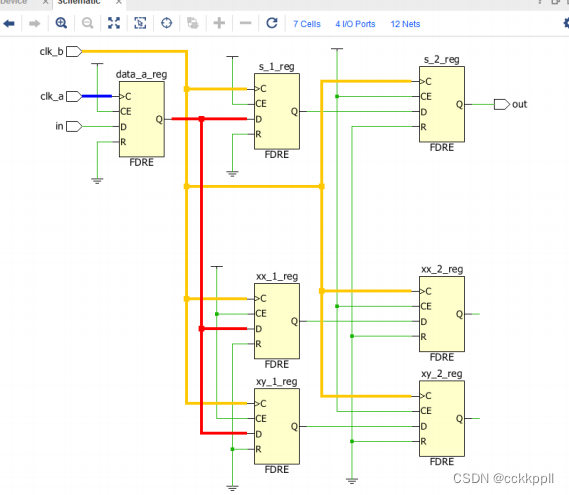

扇出

在下图所示简化的扇出示例中 , 源触发器用于驱动在 clk_b 域 ( 红色高亮 ) 中同步 3 次的信号线。不建议采用这种结构, 因为它可能导致在目标时钟域中出现数据一致性问题 , 原因在于穿过同步器的时延受到限制 , 但并不具备周期精确性。

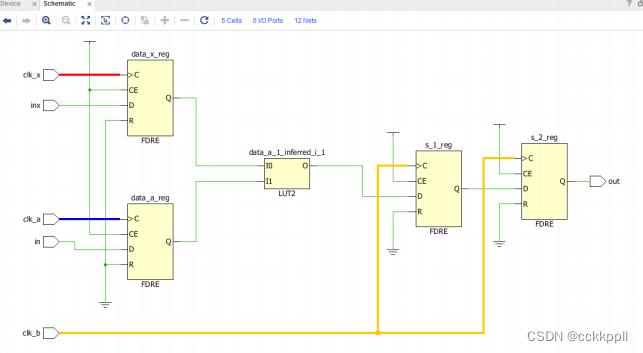

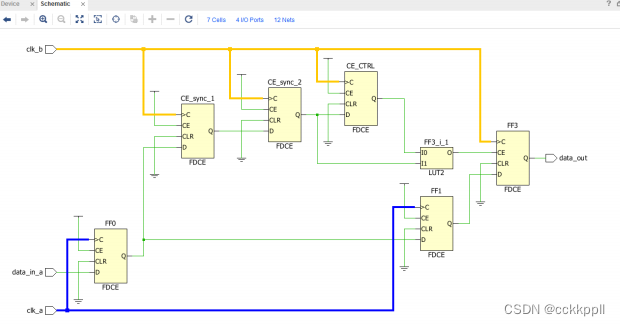

多时钟扇入

在下图所示“ Multi-Clock Fanin ” ( 多时钟扇入 ) 示例中 , clk_a 与 clk_x 正在同时通过组合逻辑 (LUT2) 将数据传输至 clk_b 域中的同步器电路。建议首先单独同步来自 clk_a 和 clk_x 的源数据 , 然后再通过某些互连逻辑或FPGA 逻辑将其组合在一起。这样可改善总体 CDC 结构的 MTBF 特性 , 并且可防止毛刺传输至目标时钟域。

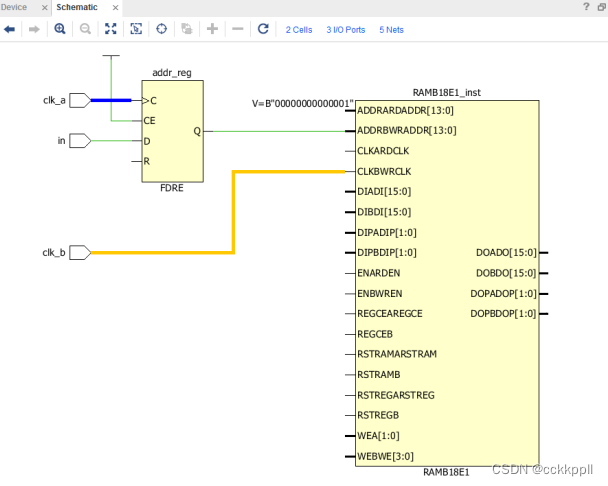

非 FD 原语

在下图所示“非 FD 原语”示例中 , 当 RAMB 原语内部不存在同步逻辑时 , 在 FDRE 与 RAMB 之间发生 CDC 。即使在 RAMB 前插入连接到 clk_b 的单阶触发器 , 受 FDRE 与 RAMB 单元之间的布线距离所限 , 此同步器仍被视为不足以满足要求。

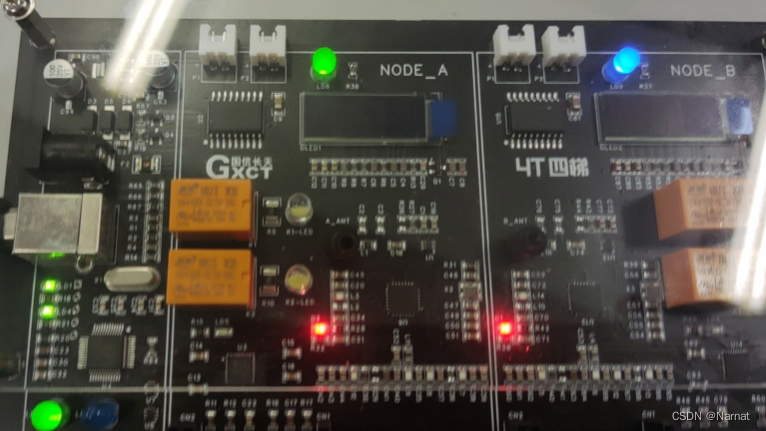

CE 控制的 CDC

在下图所示 CE 控制的 CDC 示例中 , 时钟使能信号在用于控制交汇触发器之前在目标 clk_b 域中已同步。

CDC 引擎仅检查连接到 FF3/CE 的信号是否同样由 clk_b 发送。在驱动 CE 管脚的电路上 , 对于时钟使能信号的同步方式不存在限制, 前提是将其作为安全的 CDC 路径单独报告即可。此外 , 您还负责约束从 clk_a 域到 FF3 的时延 , 这通常是通过 set_max_delay -datapath_only 约束来完成的。

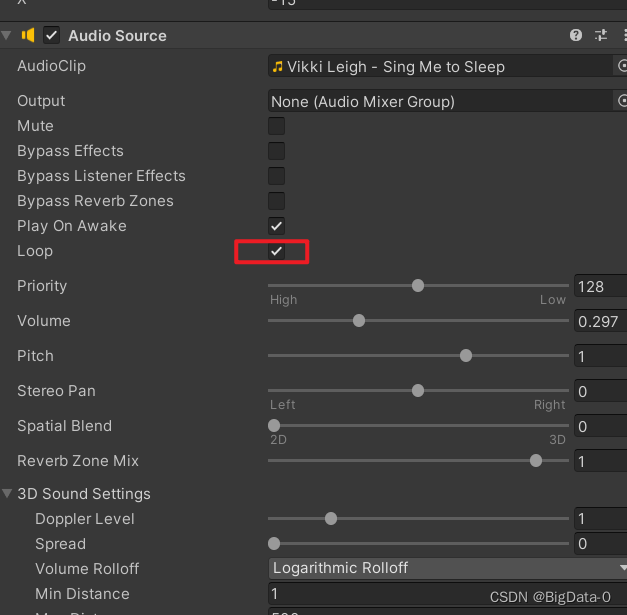

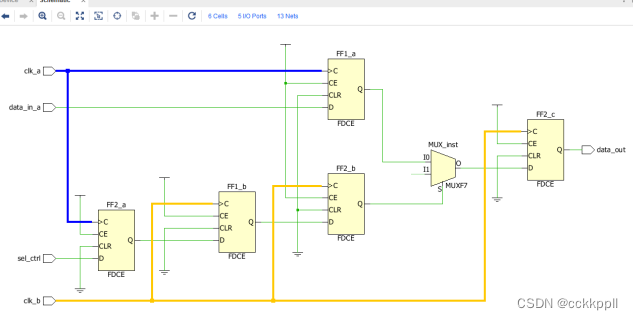

多路复用器控制的 CDC

在下图所示“多路复用器控制的 CDC ”示例中 , 多路复用器选择信号与目标时钟域 clk_b 同步。

与 CE 控制的 CDC 类似 , 对于选择信号的同步方式并无限制 , 前提是此信号单独报告为安全 , 并且用户负责约束FF2_c 上的交汇延迟。

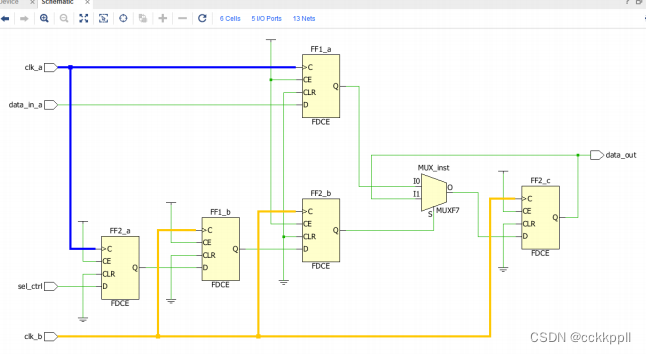

多路复用器数据保持 CDC

在下图所示的多路复用器数据保持 CDC 示例中 , 多路复用器的选择信号已同步到目标时钟域 clk_b , 而 data_out则馈送回多路复用器。

与 CE 控制的 CDC 类似 , 对于多路复用器选择信号的同步方式并无限制 , 前提是此信号单独报告为安全 , 并且用户负责约束 FF2_c 上的交汇延迟。

LUTRAM 读写潜在冲突

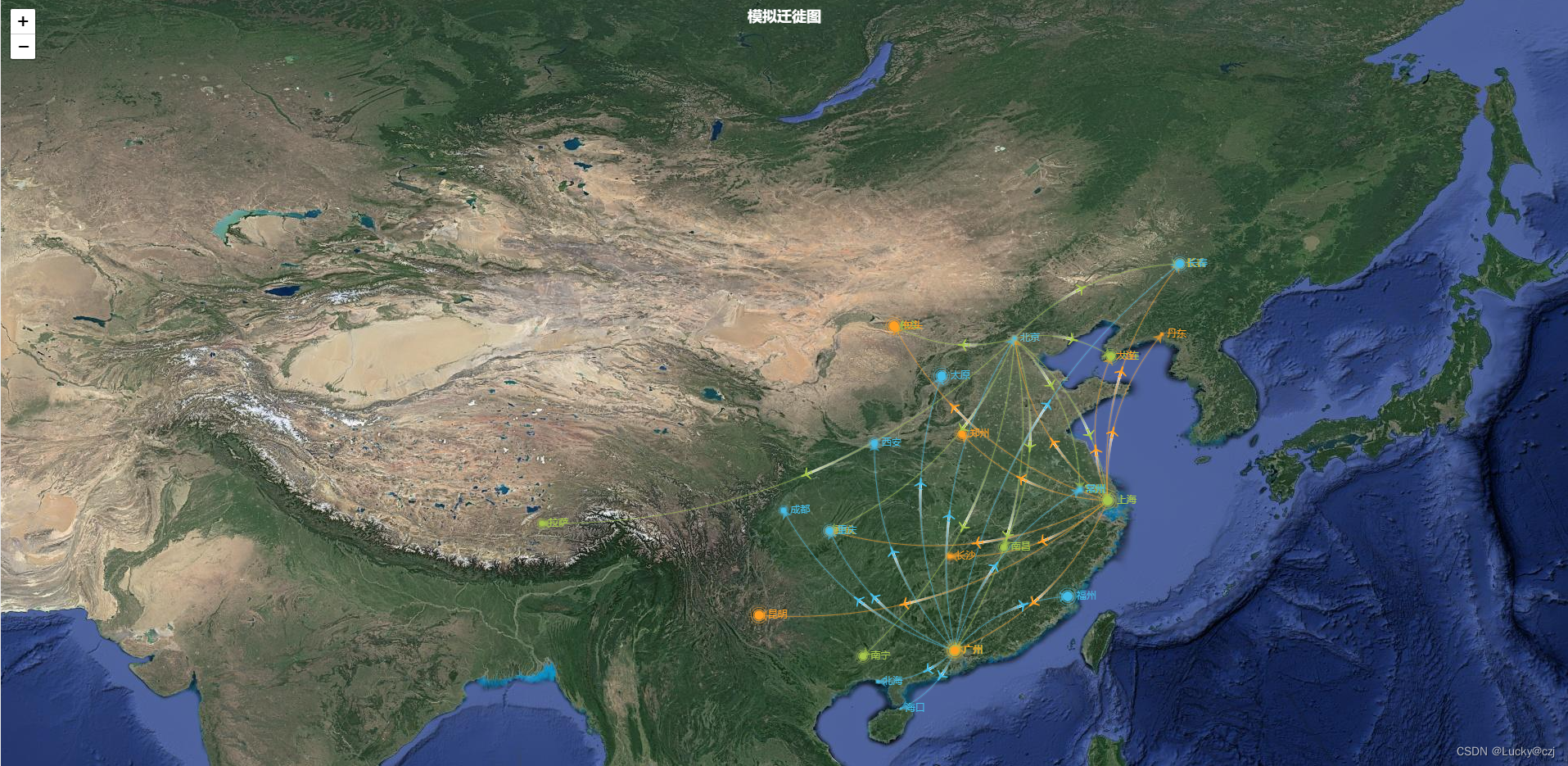

在以下 LUTRAM 读写潜在冲突示例中 , 数据写入含写时钟的 LUTRAM 内 , 而 LUTRAM 的输出则由读时钟捕获。当读写地址不同时, 写时钟与读时钟之间不存在 CDC 路径。但当读写地址相同时 , 即在写时钟与读时钟之间存在 CDC 路径。 为避免读写时钟之间出现 CDC 路径 , 需确保 LUTRAM 周围的逻辑在执行活动的读写操作期间 , 永远无法生成相同的读写地址。确保满足此条件时, 与此拓扑结构相关联的 CDC 违例即可获得豁免。例如 , AMD 的 FIFO Generator IP 具

有防止任意读写冲突的内置逻辑。