文章目录

- 一、移位寄存器定义

- 二、verilog源码

- 三、仿真结果

一、移位寄存器定义

移位寄存器定义

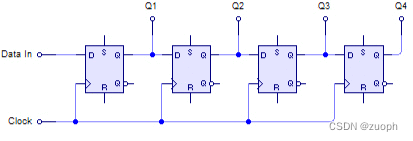

A shift register is a type of digital circuit using a cascade of flip flops where the output of one flip-flop is connected to the input of the next.

移位寄存器是一种将一组D触发器进行级联输出而形成的一种时序逻辑电路。

在设计中经常会用到的一种基础时序电路,比如下面串转并电路,通过将串行输入的码流移位将其转换成并行数据输出。

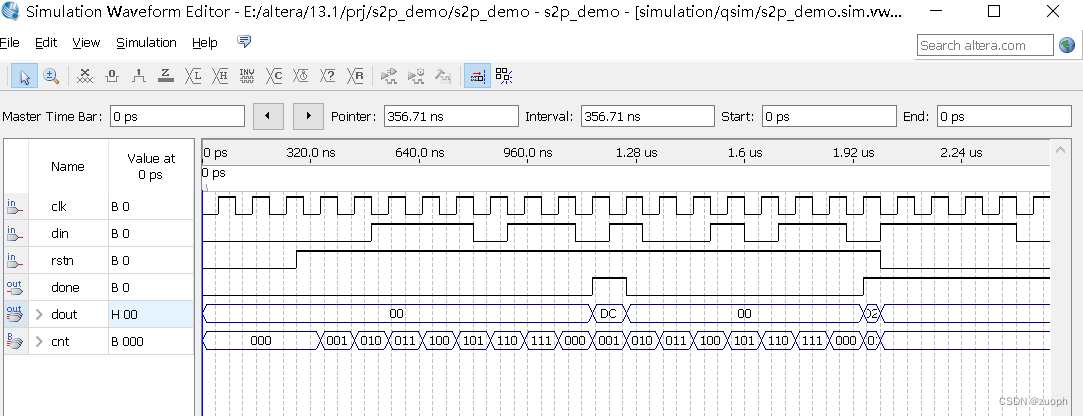

本文设计一个简单的串并转换器,实现将串行输入数据转换成8位的并行数据进行输出,同时输出一个转换完成标志。

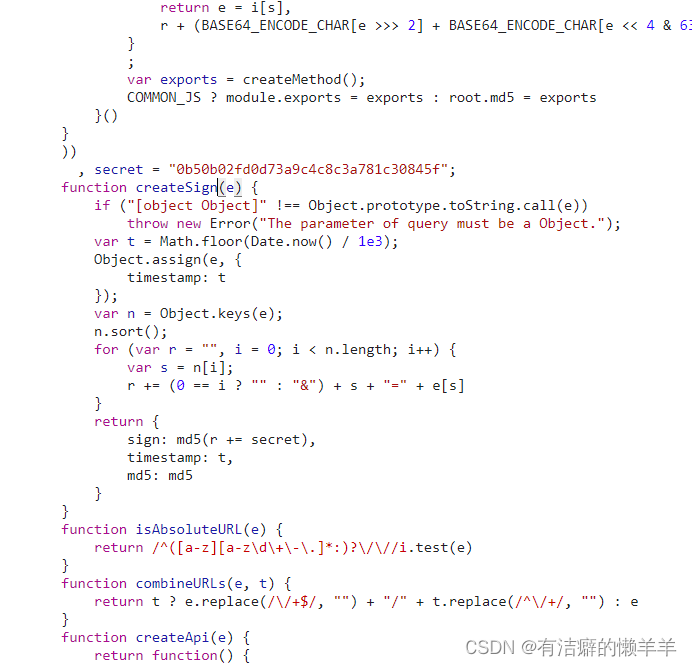

二、verilog源码

// implement a simple 8bit serial to paralle convertormodule s2p_demo (clk, rstn, din, dout, done);input clk;input rstn;input din;output [7:0] dout;output done;reg [2:0] cnt;reg done;reg done_dly;reg [7:0] dout;reg [7:0] dout_dly;always@(posedge clk or negedge rstn)beginif(!rstn) begindout_dly <= 8'bx; endelse begindout_dly[cnt] <= din; endendalways@(posedge clk or negedge rstn)beginif(!rstn) begindout <= 8'b0; endelse if(done_dly) begindout <= dout_dly;done <= done_dly; endelse begindout <= 8'b0;done <= done_dly; endendalways@(posedge clk or negedge rstn)beginif(!rstn) begincnt <= 3'b0;done_dly <= 1'b0; endelse if(cnt == 3'b111) begincnt <= 3'b0;done_dly <= 1'b1; endelse begincnt <= cnt + 1'b1;done_dly <= 1'b0;endend

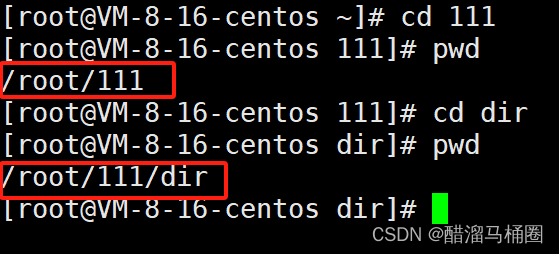

endmodule三、仿真结果

转载请注明出处!