使用细化视图对 RTL 进行最优化

完成任意实现步骤后使用 report_timing 、 report_timing_summary 或 report_design_analysis 分析时序结果时, 您必须审查关键路径结构 , 了解是否可通过修改 RTL 、使用综合属性或者使用其他综合选项来更有效地将其映射到逻辑原语。这对于包含大量逻辑层次的路径尤为重要, 因为大量逻辑层次会给实现工具施加压力并限制总体设计性能。

只要发现具有大量逻辑层次的路径 , 就必须确认路径功能是否需要如此大量的逻辑层次。通常确认逻辑层次的最佳数量并不容易, 因为它取决于您对设计的了解以及您对总体 RTL 最优化的了解程度。观察综合后经过最优化的网表并识别RTL 中的问题来源及其改进方法是一项复杂的任务。

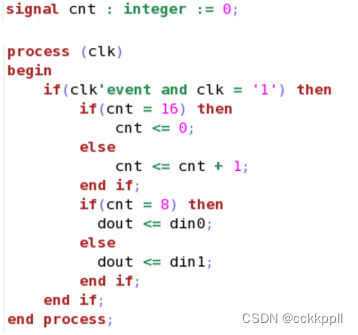

在工程模式下 , Vivado IDE 可在经过综合或实现的设计与经过细化的设计之间提供强大的交叉探测机制 , 从而帮助简化分析。请执行以下操作以对综合后/ 实现后的设计和细化设计进行交叉探测 :

1. 打开存储器中综合后 / 实现后的设计和细化的设计。

2. 选择综合后 / 实现后设计视图中的时序路径 , 按“ F4 ”键显示其板级原理图。

3. 选择 Flow Navigator 窗格中的“ Elaborated Design ” ( 细化设计 ) 。这样会同时选中对应于时序路径的 RTL 单元, 以便您可按“ F4 ”键打开 RTL 板级原理图 , 并在细化视图中查看该相同路径 , 或者从端点管脚反向走线回到起点单元。

4. 复查路径遍历的 RTL 逻辑 , 特别注意运算符或矢量的大小。

示例

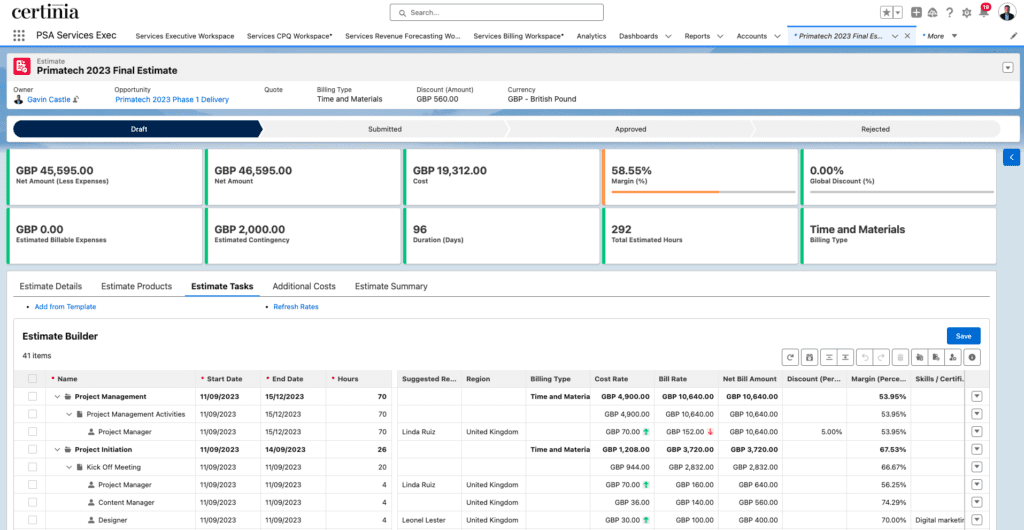

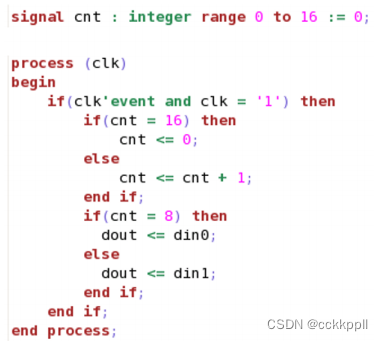

在以下示例中 , 用户编写了一个计数器 , 如下所示

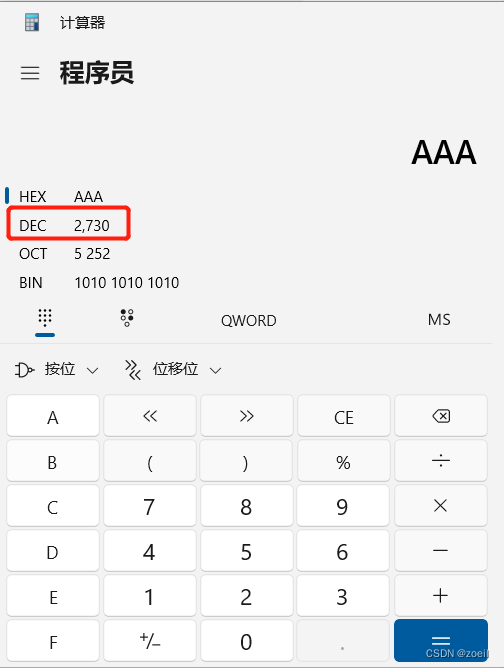

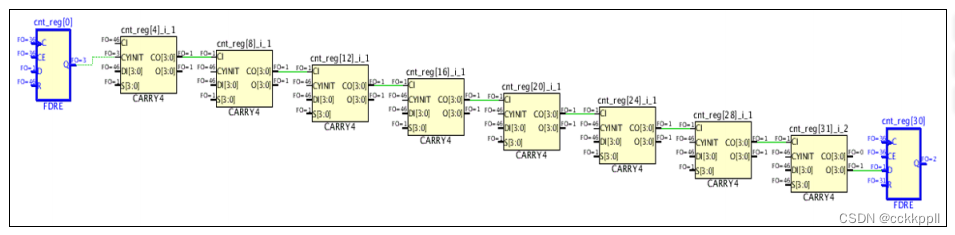

信号 cnt 按从 0 到 16 进行计数 , 需 5 位矢量用于编码。布线后关键路径的板级原理图如下图所示。端点为 cnt 信号的第 30 位。

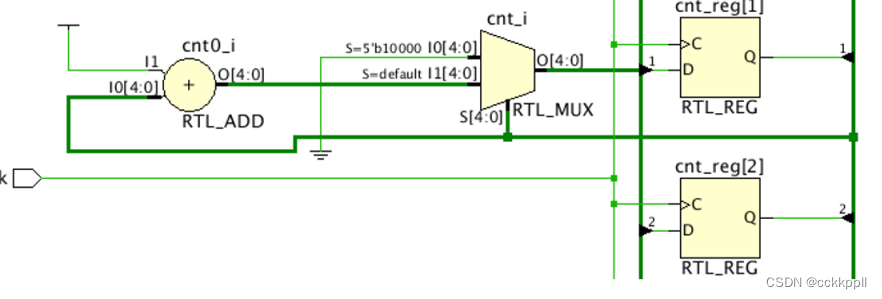

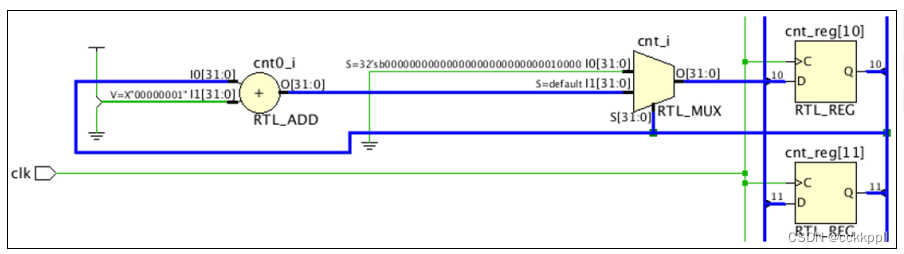

选中关键路径的起点和端点单元后 , 只需打开选定单元的板级原理图并展开从端点管脚返回到起点的逻辑 , 即可在细化视图中直观展示等效路径, 如下图所示。

细化视图显示加法器输入大小限制为 32 位 , 因为信号 cnt 已声明为整数。在此特定示例中 , 在整个综合最优化过程中均保持使用 32 位运算符。细化视图可明示所发生的变化 , 您可按如下方式更改 RTL 来获得进一步优化的网表和时序QoR。随着计数器从 0 递增至 16 , 您可为信号 cnt 定义范围 , 以强制将加法器输入宽度设置为 5 位而不是 32 位。

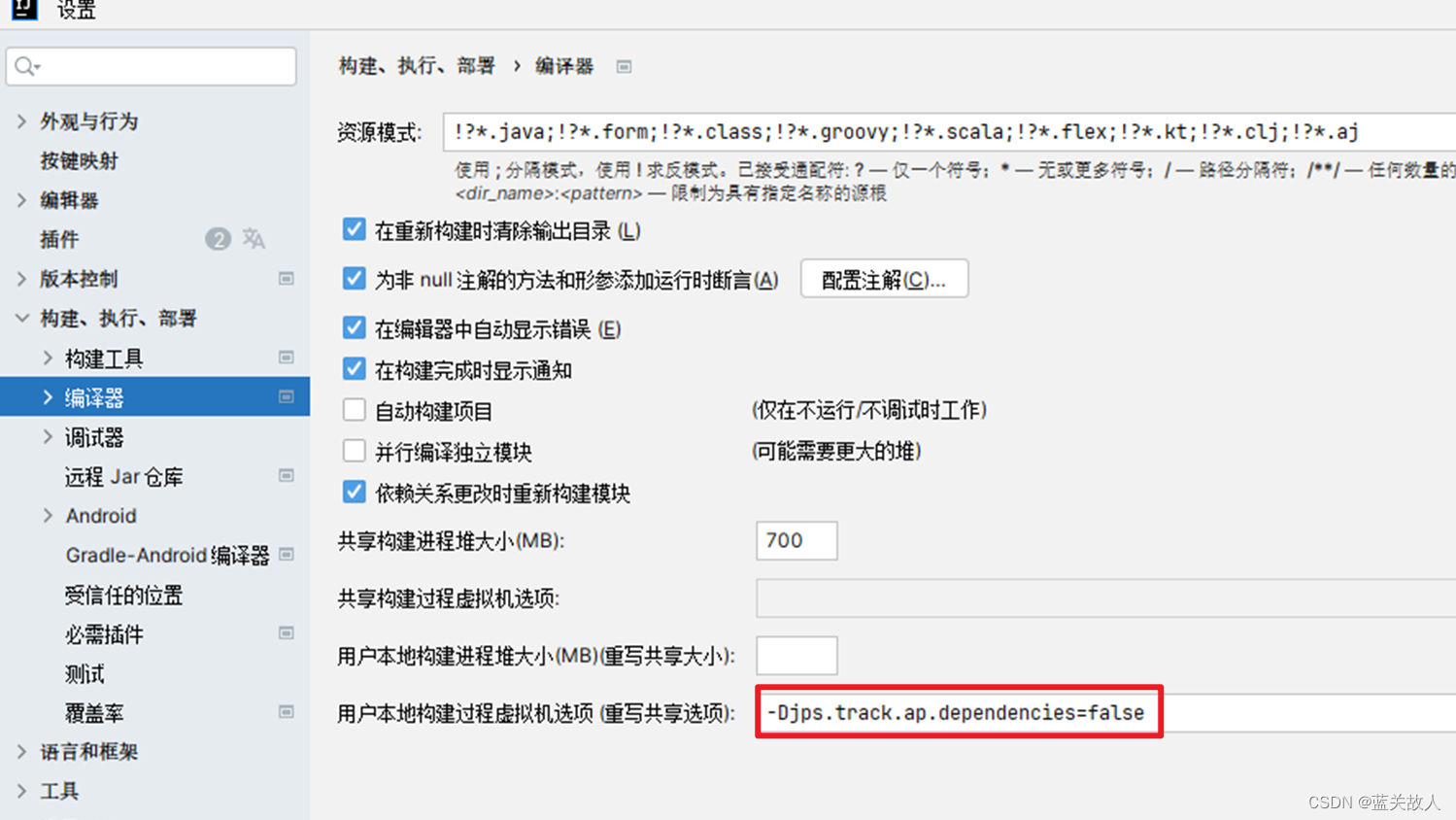

对 RTL 代码执行的更改后续将影响综合最优化 , 您可使用细化视图验证其影响 , 而无需执行整个编译流程 :