目录

一、序言

二、Set Disable Timing

2.1 基本概念

2.2 设置界面

2.3 命令语法

2.4 命令示例

三、工程示例

四、参考资料

一、序言

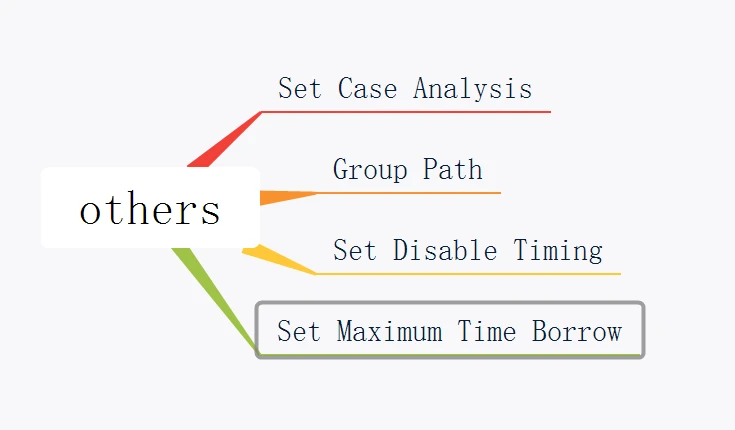

在Vivado的时序约束窗口中,存在一类特殊的约束,划分在others目录下,可用于设置忽略或修改默认的时序路径分析,以Vivado2022.1版本为例,主要包括以下4类,本文将介绍其中的Set_Disable_Timing,示例的为Vivado2022.1

二、Set Disable Timing

2.1 基本概念

时序弧:时序弧是时序路径的一部分,可以是两个引脚之间的连线,可以是输入端口和输出端口之间的逻辑单元的内部路径,或者时钟输入端口和数据输出端口间的路径

Set Disable Timing约束用于关闭时序弧,使该段路径不会进行时序分析。

约束生效范围:如果约束设置的对象是单元cell,那么所有涉及该单元的时序弧都是无效的;如果设置的是from/to 引脚,则from/to之间的时序弧是无效的;如果只设置了from或to,则所有from对象开始的时序狐是无效的,或所有终点为to所对应的对象的时序弧是无效的;如果约束的对象是port,在所有从设置的port开始或结束的时序弧也是无效的,时序弧无效自然不会进行对应的时序分析。

2.2 设置界面

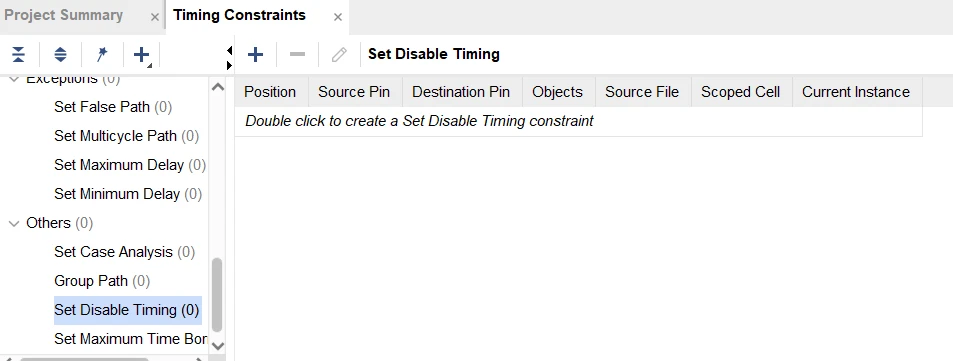

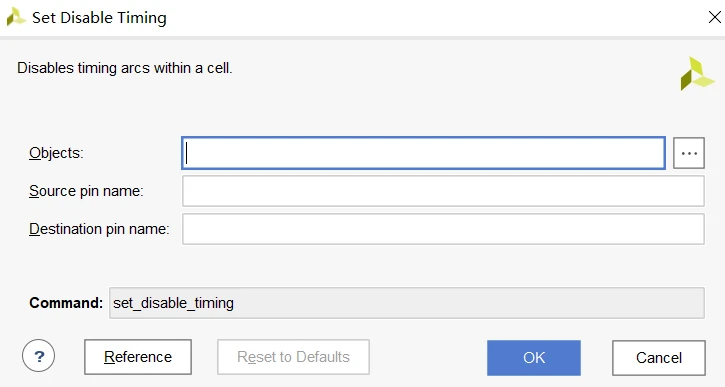

进入Timing Constraints界面,在左侧Others栏中选中Set Disable Timing,右侧即显示Set Disable Timing

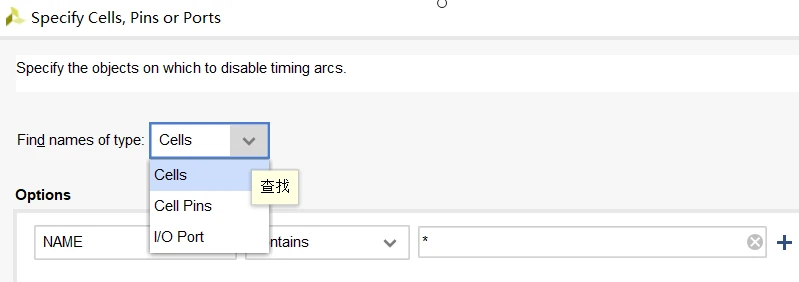

约束设置子界面需设置Objects,arcs的source引脚名字,目的引脚名字

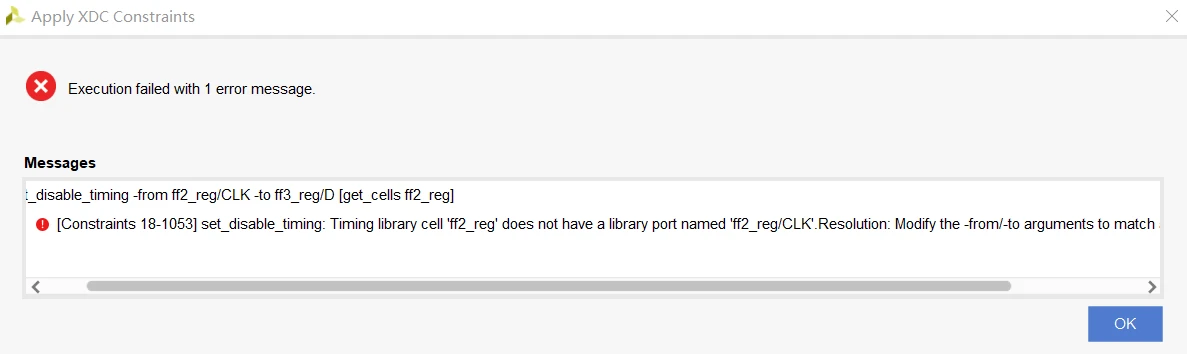

注意source引脚和Destination引脚不是可选的,需手动输入,一定要输入存在的有效引脚,否则报约束格式错误,要获取对应单元的pin引脚,也可通过命令get_lib_pins -of [get_cells {cells_name}]来获取

设置的对象可为Cells,或单元引脚,以及端口

2.3 命令语法

命令格式如下

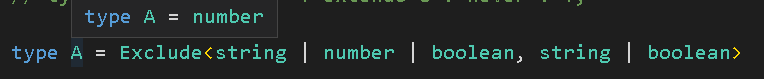

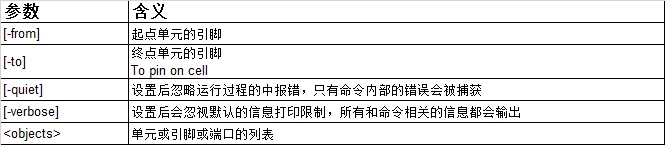

set_disable_timing [‑from <arg>] [‑to <arg>] [‑quiet] [‑verbose] <objects>参数含义列表如下

2.4 命令示例

1、对一个LUT的输入引脚I0到输出O的时序弧设置约束

set_disable_timing -from I0 -to O [get_cells div_dec_ff_i/U0/count_i_1]2、对一个块状RAM的输入引脚和输出引脚设置时序弧无效的约束

set_disable_timing -from WEBWE[3] -to CLKMEM [get_cells \ldpc_dout360_channel/U_AP_FIFO_ldpc_dout360_channel_ram/mem_reg_0]3、对经过指定单元存储器单元的所有时序弧设置无效约束

set arcs [get_timing_arcs -of_objects [get_cells \ldpc_dout360_channel/U_AP_FIFO_ldpc_dout360_channel_ram/mem_reg_0]]三、工程示例

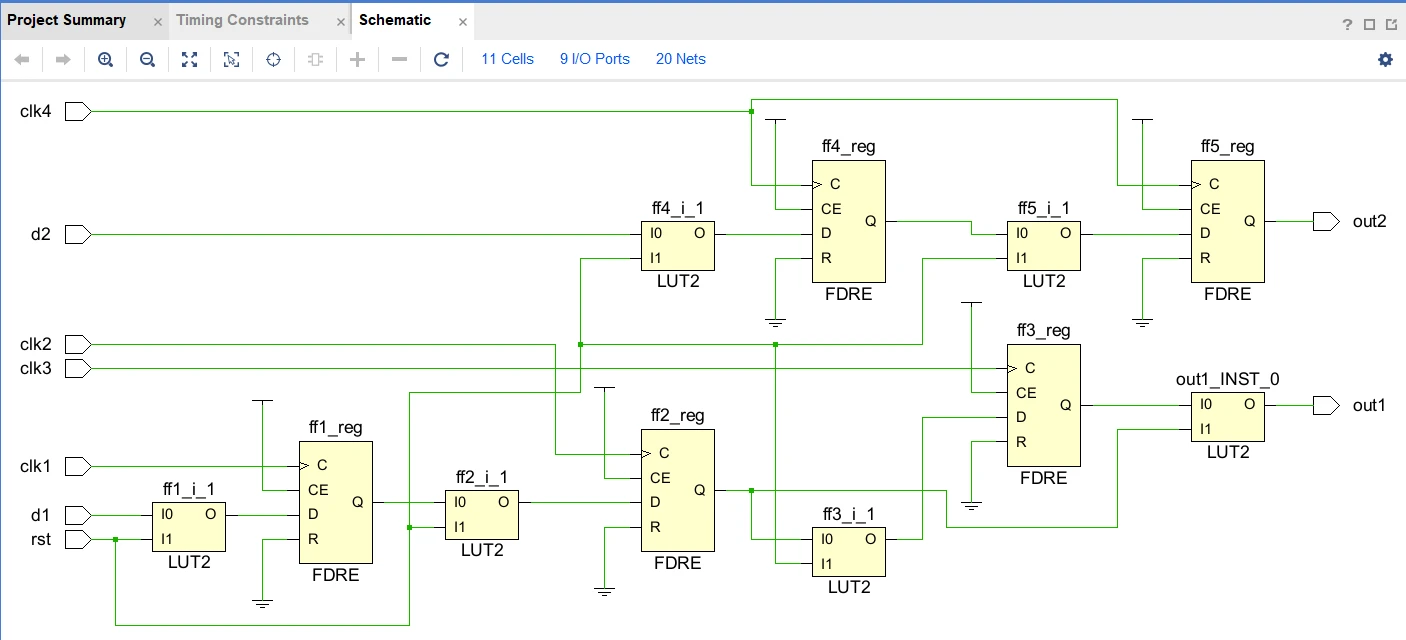

工程代码:

module timing_analysis(d1,d2,clk1,clk2,clk3,clk4,rst,out1,out2); input d1,d2,clk1,clk2,clk3,clk4,rst; output out1,out2; reg ff1,ff2,ff3,ff4,ff5; always @(posedge clk1) if(!rst) ff1<=0; else ff1<=d1; always @(posedge clk2) if(!rst) ff2<=0; else ff2<=ff1; always @(posedge clk3) if(!rst) ff3<=0; else ff3<=ff2; assign out1=ff3&ff2; always @(posedge clk4) if(!rst) ff4<=0; else ff4<=d2; always @(posedge clk4) if(!rst) ff5<=0; else ff5<=ff4; assign out2=ff5; endmodule 综合后网表连接图

约束内容如下,对经过clk4端口的时序弧和经过触发器引脚ff2_reg/Q的时序弧设置无效约束

create_clock -period 10.000 -name clk1 -waveform {0.000 5.000} [get_ports clk1]

create_clock -period 7.000 -name clk2 -waveform {0.000 3.500} [get_ports clk2]

create_clock -period 8.000 -name clk3 -waveform {0.000 5.000} [get_ports clk3]

create_clock -period 5.000 -name clk4 -waveform {0.000 3.500} [get_ports clk4]

set_input_jitter [get_clocks clk1] 1.660

set_disable_timing [get_ports clk4]

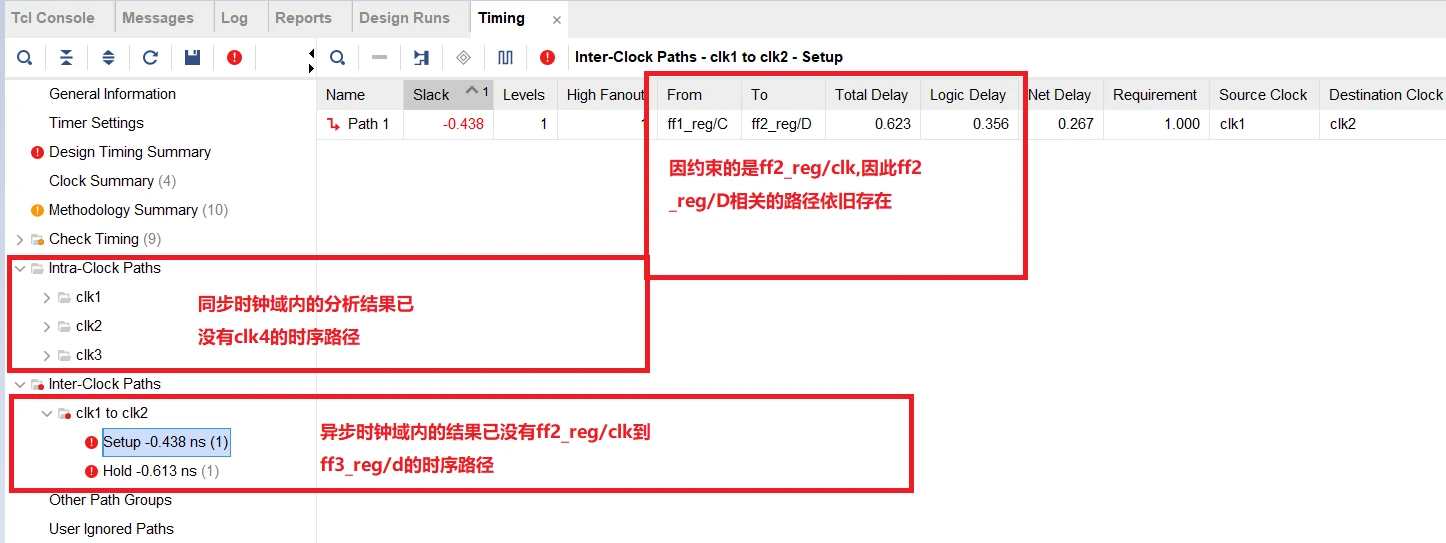

set_disable_timing [get_pins ff2_reg/Q]约束中不设置set_disable_timing约束时

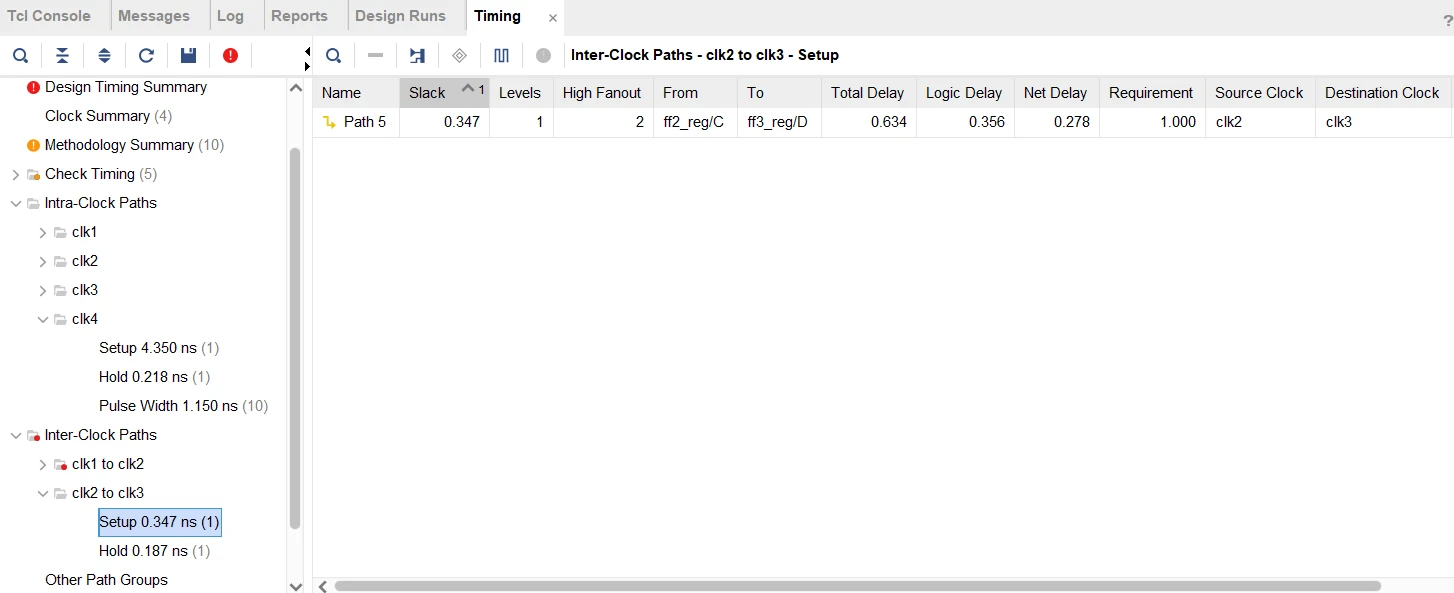

设置约束后时序分析结果

四、参考资料

用户手册:ug903-vivado-using-constraints-en-us-2022.2.pdf

链接:https://pan.baidu.com/s/17AK_-J4wRXiFLtLTorlrwg?pwd=mylt

提取码:mylt