依公知及经验整理,原创保护,禁止转载。

专栏 《深入理解NAND Flash》

<<<< 返回总目录 <<<<

前言

日本东芝最初发明半导体存储芯片时,认为它就像拍照时的闪光一样迅速,因此命名为闪存(Flash)。如今,我们使用的最常见的形式是NOR闪存和NAND闪存。根据不同的场景,我们使用不同的存储器。 NOR闪存通常用于嵌入式系统,而手机内部存储、PC硬盘和USB快闪等则使用NAND闪存。这些设备中存储的数据通常被读取的次数比写入的次数多,但写入的频率仍然相对较高,因此NAND闪存是更常见的选择。

1 Flash 物理结构

1.1 Flash 是什么?

Flash是一种非易失性存储设备。与易失性存储设备相对应,Flash Memory所存储的数据即使断电也不会丢失。除了Flash,其他常见的非易失性存储设备包括磁盘和光盘等。易失性存储设备就像其名字一样,一旦断电数据就会丢失。常见的易失性存储设备包括内存条,如DDR5等。

最小存储单元

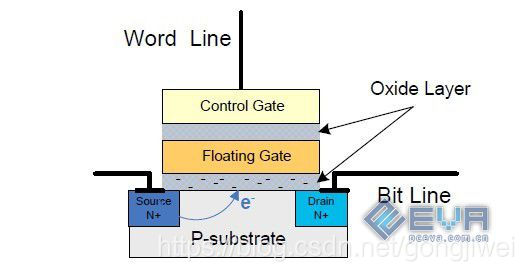

闪存的最小存储单元是“晶体管-栅极-漏极”(Transistor-Gate-Drain,TGD)结构。在这种结构中,栅极上的电子可以控制漏极和源极之间的电荷通量,从而实现存储和读取数据。

Flash存储器的数据是以电荷的形式存储在内部单元中的。电荷的数量取决于控制栅极施加的电压,控制栅极决定是否充电或放电。数据的表示方式则是根据存储单元中电荷的电压是否超过阈值Vth而确定的。

1.2 NAND Flash的结构

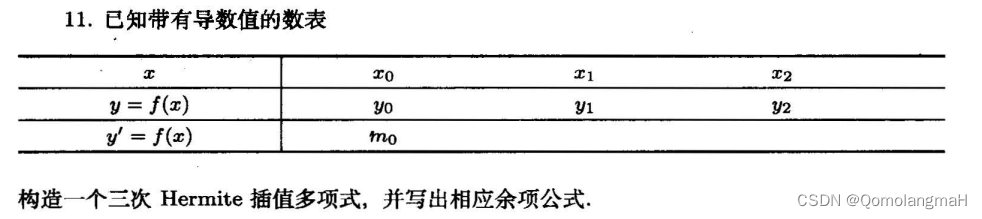

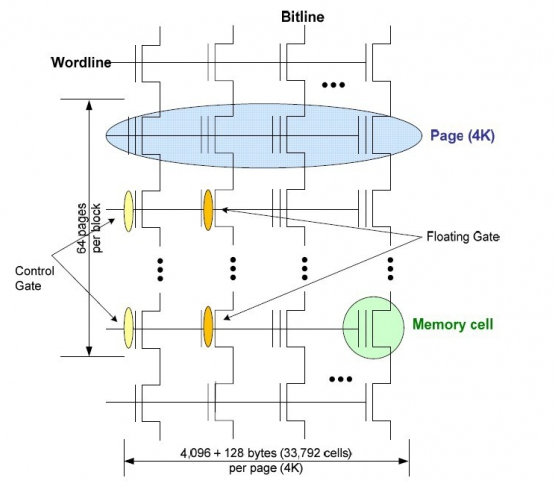

如上图所示,这是一个8Gb 50nm的SLC颗粒存储单元物理结构。

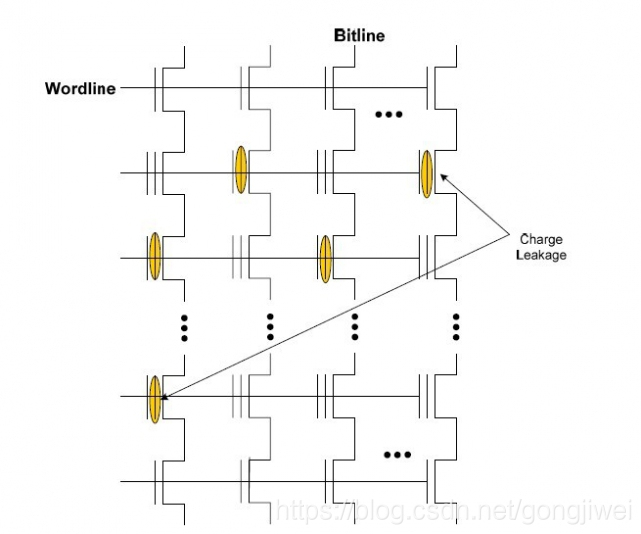

位线和字线

闪存需要使用位线(Bitline)和字线 (Wordline) 组成的矩阵。位线用于选择存储单元的行,而字线用于选择存储单元的列。利用这种方式,我们可以在矩阵中选择特定的存储单元,并对其进行读写操作。

1.3 闪存芯片组成结构

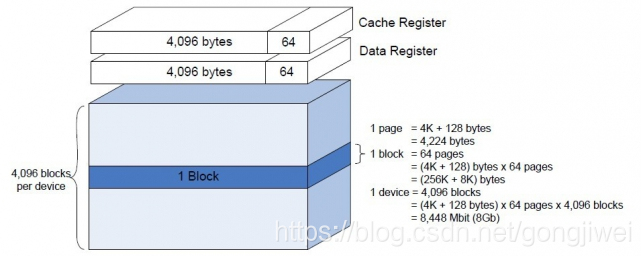

下图是个8Gb 50nm的SLC闪存芯片组成结构。

每个page有33,792个单元,每个单元代表1bit(SLC),所以每个page就是4096Byte + 128Byte(SA)。

每个Block有64个page组成,所以每个Block容量为262,114Byte + 8192Byte (SA)

page是NAND Flash上最小的读/写单位(一个page上的单元共享一根字符线Word line),块是最小的擦除单位(不同厂牌不同型号颗粒有不同的page和block大小)。

4KB的页大小,256KB的块大小。图中4096字节用于存储数据,另外128字节用来做管理和ECC用。

2 NAND Flash 的使用挑战

挑战1:需要先擦除才能写入。

擦除操作就是让块中所有的bit变为1,从一个干净的“已擦除”状态的block重新开始。当里面的页变为0后,只有擦除整个块才能让这个页变为1。为了尽量减少擦除的次数,成熟的块管理技术必不可少。

挑战2:读/写干扰。

NAND Flash的电荷非常不稳定,在读/写中很容易对邻近的单元造成干扰,干扰后会让附近单元的电荷脱离实际的逻辑数值,造成bit出错,因为阀值接近的关系,MLC相对SLC来说更容易受到干扰。

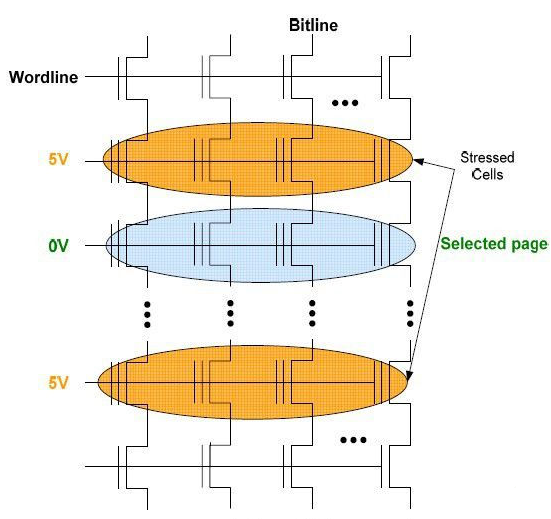

读取干扰

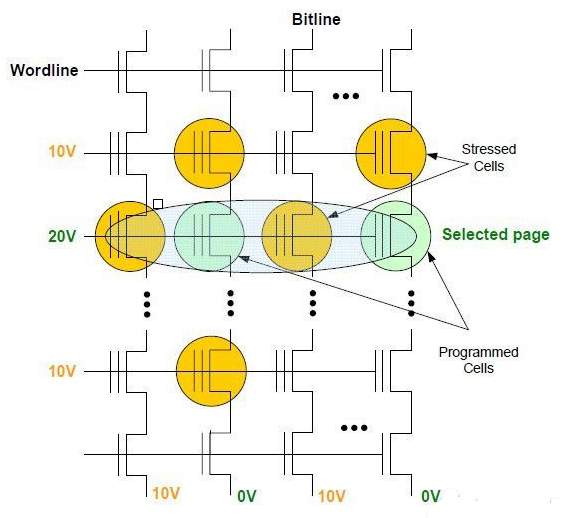

写入干扰

读取干扰指的是在读取某个page时,邻近的bit会受到升高电压的干扰,造成bit出错。写入干扰指的是,某个page在写入时,邻近bit的电压也被升高了,造成bit出错。相对写入干扰来说,读取干扰明显小的多。在读/写干扰中,可能造成某些bit被改变,结果造成数据出错。所以需要在返回数据给主机前,用ECC/EDC算法来纠正这些bit的错误。随着闪存工艺的提升,同样大小的晶片上被封装入更多的单元,造成干扰越来越厉害,所以需要更强大的ECC/EDC来纠正bit。

挑战3:数据保存期限

数据保存期指的是当完全断电后,数据能在NAND Flash里保存多久。NAND单元必须保证一个稳定的电压水平,来保证数据是有效的。典型的SLC一般为10年。电荷从悬浮门里漏出,我们叫做电子迁移,当随着时间的流逝,电荷泄漏到一定程度,改变了NAND单元里悬浮门的电压对应的逻辑值,这样就造成bit出错。

数据保存期会随着擦写次数的增加而明显降低,而且从上面的原理中看出,MLC的数据保存期明显会比SLC少。(更容易被干扰)

挑战4:坏块

NAND Flash里有2种坏块类型:

1,出厂坏块:由于为了保证产量和控制成本,出厂的NAND Flash某些就会有坏块。厂商保证SLC出厂坏块低于2%,MLC出厂坏块低于5%。

2,积累坏块:在多次的写入/擦除循环中,某些NAND单元的电荷电压被永久性的改变了,那就意味着包含这个NAND单元不可用了。

所以固态硬盘需要有坏块管理才能使用,主控制器用坏块表来映射出厂坏块和积累坏块到坏块区内,出厂时,颗粒的第一个块Block 0厂商会保证是可用的(至少ECC后可用)。

挑战5:擦写次数限制

造成NAND Flash有擦写次数限制的主要有2个因素:

1,电荷被困在氧化层,不能进入悬浮门。

2,氧化层结构被破坏。

如图,一旦氧化层损坏到达一定程度,造成电荷越来越难在P-substrate和悬浮门之间交流。电荷被困在氧化层造成悬浮门中的电压到不了阀值,所以说这个NAND单元就要被放入坏块区了。

当前主流SLC的P/E为10万次,50nm MLC为1万次,3xnm的MLC为5000次。到了这个数字并不意味着就不能用了,这个只是代表平均寿命,也就是说到了这个次数后,坏块就会开始大量增加了。

转载

https://blog.csdn.net/qq_41371349/article/details/104927524

NANDFlash原理_gongjiwei的博客-CSDN博客

参考