一、实验电路图、状态图、程序代码、仿真代码、仿真波形图(可以只写出核心功能代码,代码要有注释)

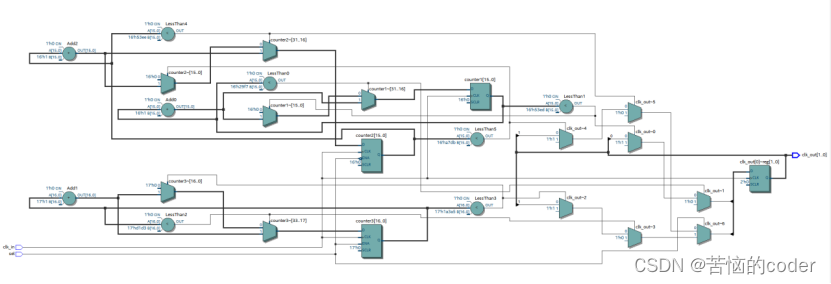

不管sel为0或者1,clk_out[0]的频率都是不变的,故在always块当中,可优先对clk_out[0]进行处理,由两频率相除得到比值,再由一计数器counter1计数,由于占空比为50%,故待到counter1达到clk_out[0]比值一半时将clk_out[0]反相。处理完clk_out[0]后,处理clk_out[1],根据不同的sel得到不同的比值,但是过程基本一样。

误差分析:

clk_out[0]:理论频率2327Hz 由于四舍五入程序中num1为21487

故clk_out[0]周期为20 × 21487 = 0.00042974 s 换算为频率约为 2326.988Hz

故误差为 (2327 - 2326.988)/ 2327 × 100% 约为 0.00052%

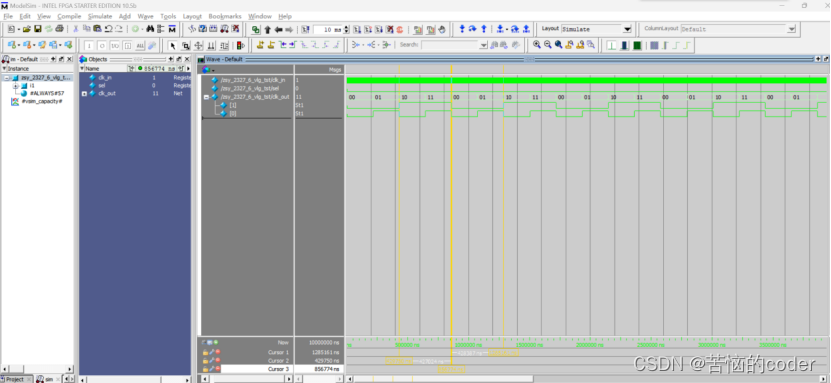

当sel为0时clk_out[1]:理论频率1163.5Hz 由于四舍五入程序中num2为42974

故clk_out[0]周期为20 × 42974 = 0.00085948 s 换算为频率约为 1163.494Hz

故误差为 (1163.5 - 1163.494)/ 1163.5 × 100% 约为 0.00052%

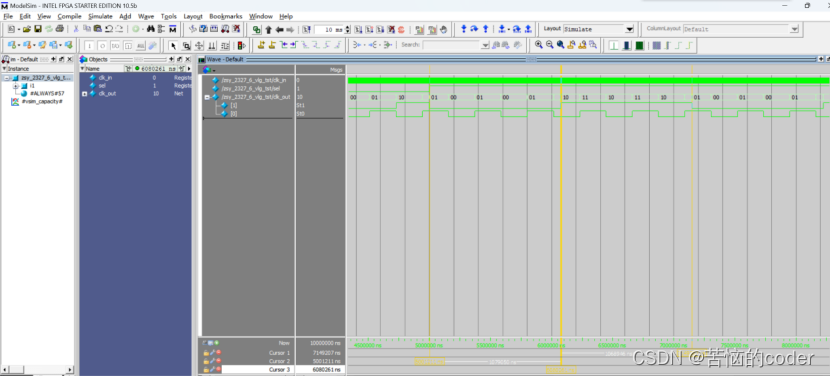

当sel为1时clk_out[1]:理论频率465.4Hz 由于四舍五入程序中num3为 107435

故clk_out[0]周期为20 × 107435 = 0.0021487 s 换算为频率约为 465.398Hz

故误差为 (465.4 - 465.398)/ 465.4 × 100% 约为 0.00043%

二、引脚分配表(电路中的信号名称->主板器件名称->引脚号PIN)

| 信号名 | 主板器件 | PIN | 信号名 | 主板器件 | PIN | |

| clk_in | 50MHz | PIN_90 | ||||

| clk_out[1] | LED1 | PIN_50 | ||||

| clk_out[0] | LED0 | PIN_46 | ||||

| sel | Key0/SW0/LED8 | PIN_24 | ||||

三、编译报告

| Top-level Entity name | Family | Device |

| zsy_2327_6 | Cyclone IV E | EP4CE6E22C8 |

| Total logic elements | Total registers | Total pins |

| 90/6,272( <1% ) | 51 | 4/92( 4% ) |

| Total memory bits | Embedded Multiplier 9-bit elements | Total PLLs |

| 0/276,480( 0% ) | 0/30( 0% ) | 0/2( 0% ) |