概述:

xilinx设计的触发器提供了多种配置方式,方便设计最简触发器,同步复位触发器,异步复位触发器,同步时钟使能触发器,异步时钟使能触发器。输出又分为同步复位和置位,异步清零和预置位。

官方提供的原语

FDCPE #(.INIT(1'b0) // Initial value of register (1'b0 or 1'b1)) FDCPE_inst (.Q(Q), // Data output.C(C), // Clock input.CE(CE), // Clock enable input.CLR(CLR), // Asynchronous clear input.D(D), // Data input.PRE(PRE) // Asynchronous set input);FDCE #(.INIT(1'b0) // Initial value of register (1'b0 or 1'b1)) FDCE_inst (.Q(Q), // Data output.C(C), // Clock input.CE(CE), // Clock enable input.CLR(CLR), // Asynchronous clear input.D(D) // Data input);FDRSE #(.INIT(1'b0) // Initial value of register (1'b0 or 1'b1)) FDRSE_inst (.Q(Q), // Data output.C(C), // Clock input.CE(CE), // Clock enable input.D(D), // Data input.R(R), // Synchronous reset input.S(S) // Synchronous set input);内容

1.同步复位和置位

2. 同步时钟使能

3. 异步清零和预置位

4. 异步时钟使能

1.同步复位和置位

verilog c代码

module primitive1(input clk,input rst_n,input a,output reg y,output reg y1);

always @ (posedge clk )if (rst_n==0) y <= 1'b0;else y <= a;always @ (posedge clk )if (rst_n==0) y1 <= 1'b1;else y1 <= a;endmoduleverilog 原语代码,FDR为复位原语,FDS置位原语

module primitive1 (clk, rst_n, a, y, y1

);input clk;input rst_n;input a;output y;output y1;wire a_IBUF_1;wire clk_BUFGP_3;wire rst_n_IBUF_5;wire rst_n_inv;wire y1_OBUF_9;wire y_OBUF_10;FDR y_1 (.C(clk_BUFGP_3),.D(a_IBUF_1),.R(rst_n_inv),.Q(y_OBUF_10));FDS y1_2 (.C(clk_BUFGP_3),.D(a_IBUF_1),.S(rst_n_inv),.Q(y1_OBUF_9));IBUF rst_n_IBUF (.I(rst_n),.O(rst_n_IBUF_5));IBUF a_IBUF (.I(a),.O(a_IBUF_1));OBUF y_OBUF (.I(y_OBUF_10),.O(y));OBUF y1_OBUF (.I(y1_OBUF_9),.O(y1));BUFGP clk_BUFGP (.I(clk),.O(clk_BUFGP_3));INV rst_n_inv1_INV_0 (.I(rst_n_IBUF_5),.O(rst_n_inv));

endmodule

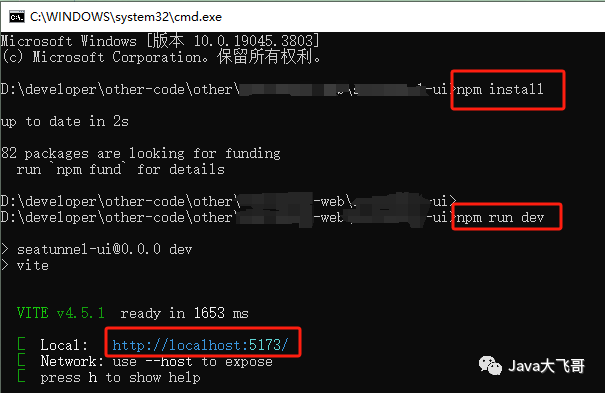

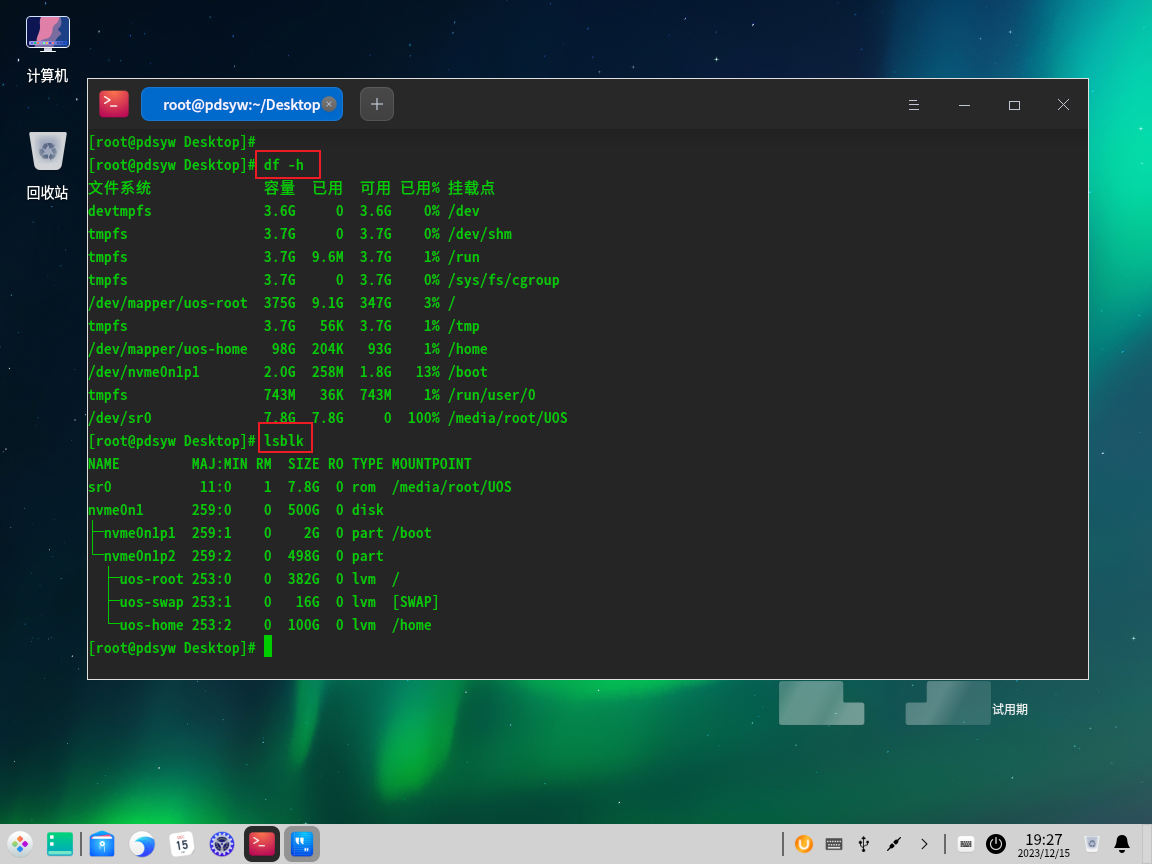

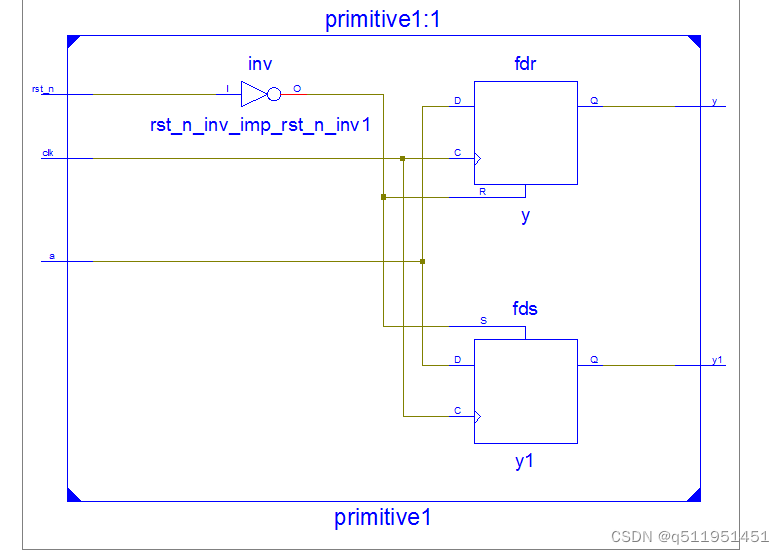

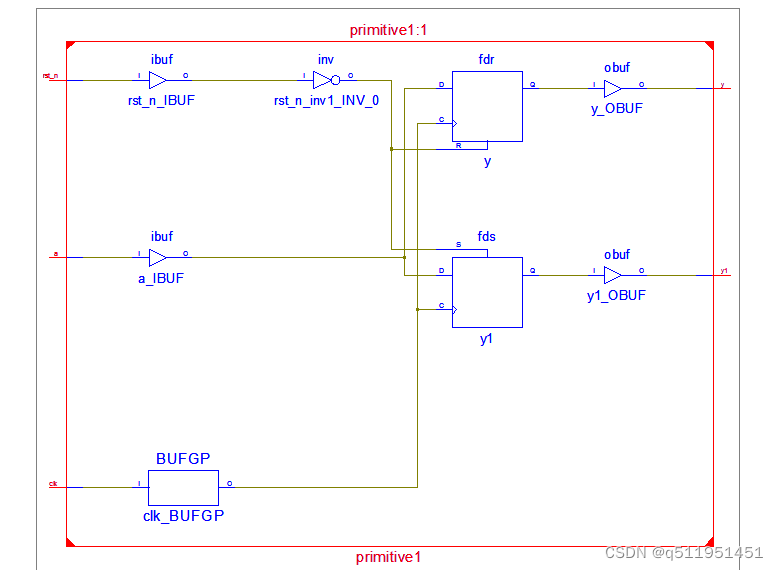

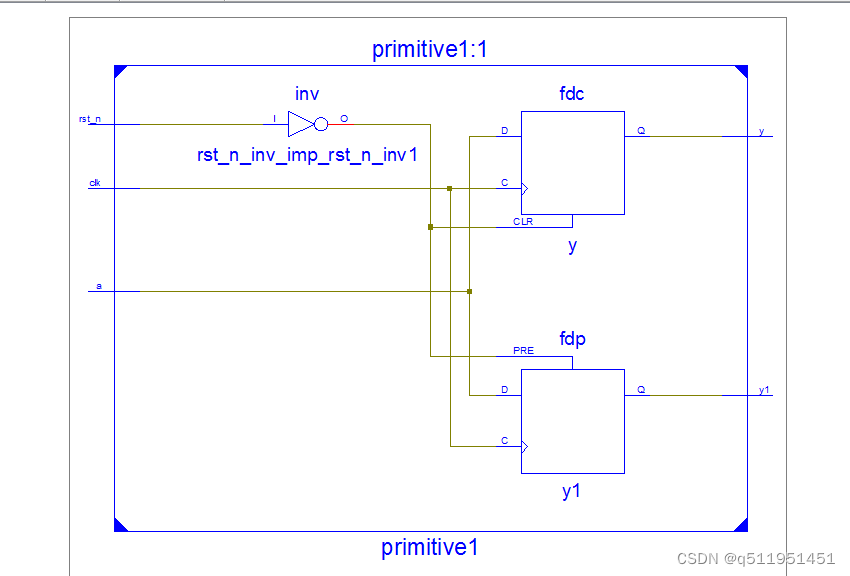

RTL结构图

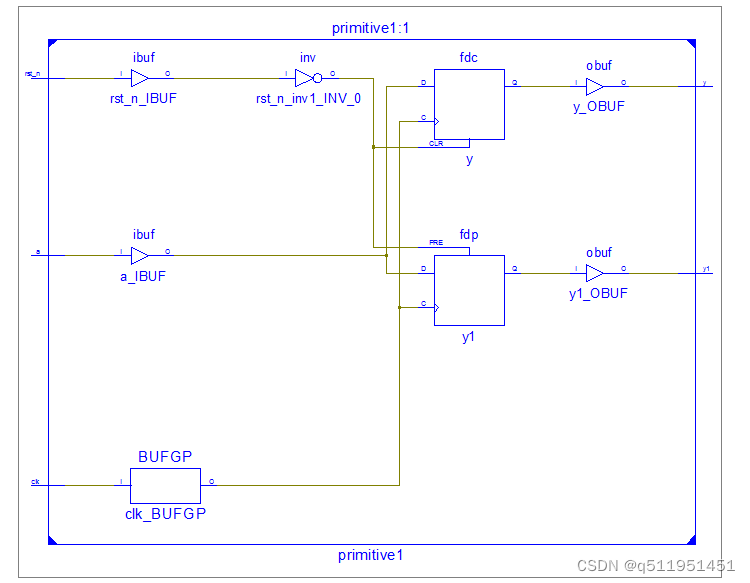

技术原理图

2. 同步时钟使能

verilog c代码

module primitive1(input clk,input rst_n,input a,input enable_clk,output reg y);

always @ (posedge clk )if (rst_n==0) y <= 1'b0;else if (enable_clk)y <= a;endmodule原语代码,使用了FDRE实现同步时钟使能原语

module primitive1 (enable_clk, clk, rst_n, a, y

);input enable_clk;input clk;input rst_n;input a;output y;wire a_IBUF_1;wire clk_BUFGP_3;wire enable_clk_IBUF_5;wire rst_n_IBUF_7;wire rst_n_inv;wire y_OBUF_10;FDRE y_1 (.C(clk_BUFGP_3),.CE(enable_clk_IBUF_5),.D(a_IBUF_1),.R(rst_n_inv),.Q(y_OBUF_10));IBUF enable_clk_IBUF (.I(enable_clk),.O(enable_clk_IBUF_5));IBUF rst_n_IBUF (.I(rst_n),.O(rst_n_IBUF_7));IBUF a_IBUF (.I(a),.O(a_IBUF_1));OBUF y_OBUF (.I(y_OBUF_10),.O(y));BUFGP clk_BUFGP (.I(clk),.O(clk_BUFGP_3));INV rst_n_inv1_INV_0 (.I(rst_n_IBUF_7),.O(rst_n_inv));

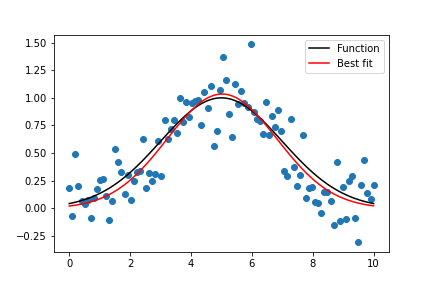

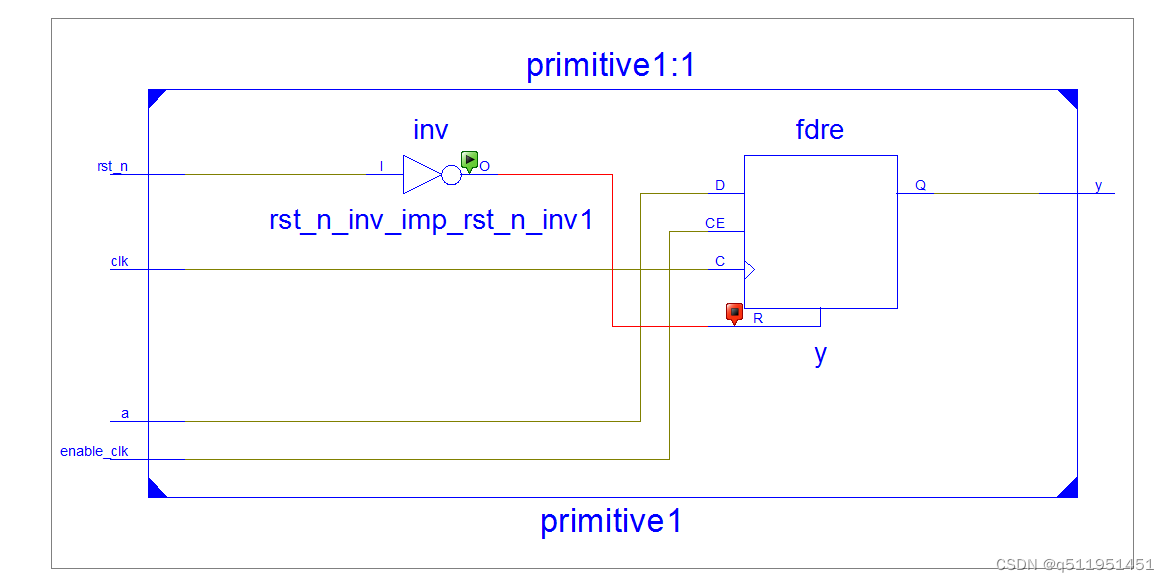

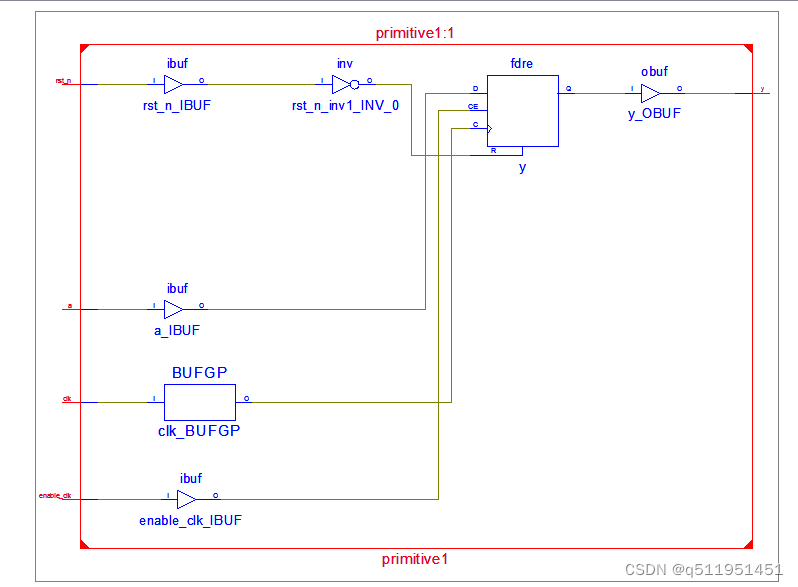

endmoduleRTL结构图,fdre使用了同步复位端口R,以及时钟使能端口CE。

技术原理图

3. 异步清零和预置位

verilog c代码

module primitive1(input clk,input rst_n,input a,output reg y,output reg y1);

always @ (posedge clk or negedge rst_n)if (rst_n==0) y <= 1'b0;else y <= a;always @ (posedge clk or negedge rst_n)if (rst_n==0) y1 <= 1'b1;else y1 <= a;endmodule

原语,使用FDC和FDP实现异步清零和预置位

module primitive1 (clk, rst_n, a, y, y1

);input clk;input rst_n;input a;output y;output y1;wire a_IBUF_1;wire clk_BUFGP_3;wire rst_n_IBUF_5;wire rst_n_inv;wire y1_OBUF_9;wire y_OBUF_10;FDC y_1 (.C(clk_BUFGP_3),.CLR(rst_n_inv),.D(a_IBUF_1),.Q(y_OBUF_10));FDP y1_2 (.C(clk_BUFGP_3),.D(a_IBUF_1),.PRE(rst_n_inv),.Q(y1_OBUF_9));IBUF rst_n_IBUF (.I(rst_n),.O(rst_n_IBUF_5));IBUF a_IBUF (.I(a),.O(a_IBUF_1));OBUF y_OBUF (.I(y_OBUF_10),.O(y));OBUF y1_OBUF (.I(y1_OBUF_9),.O(y1));BUFGP clk_BUFGP (.I(clk),.O(clk_BUFGP_3));INV rst_n_inv1_INV_0 (.I(rst_n_IBUF_5),.O(rst_n_inv));

endmodule

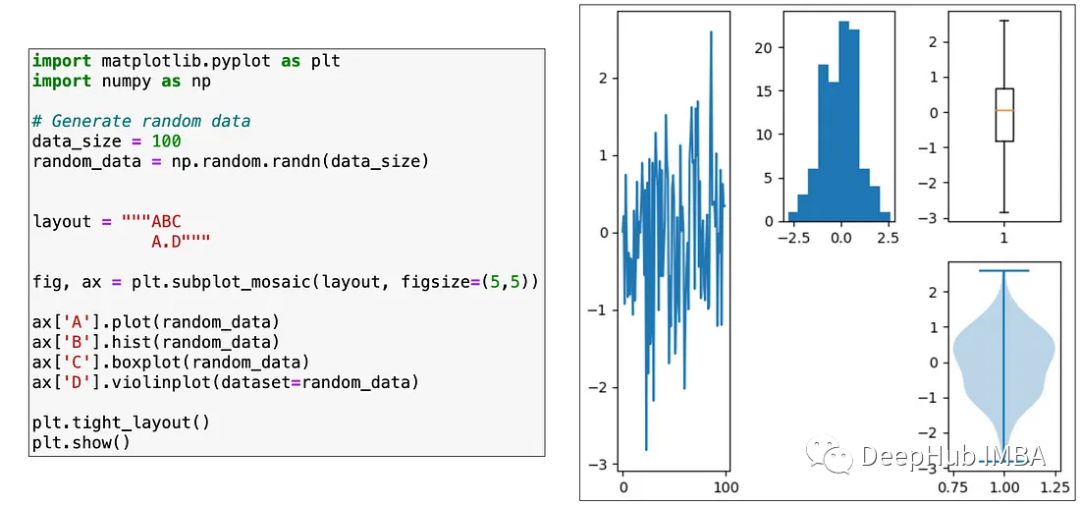

RTL结构图,异步清零连接到了CLR端口,异步预置位连接到了PRE端口

技术原理图

4. 异步时钟使能

verilog c代码

module primitive1(input clk,input rst_n,input a,input enable_clk,output reg y);

always @ (posedge clk or negedge rst_n)if (rst_n==0) y <= 1'b0;else if (enable_clk)y <= a;endmodule

原语,使能端连接到了CE,异步清零连接到了CLR。

module primitive1 (enable_clk, clk, rst_n, a, y

);input enable_clk;input clk;input rst_n;input a;output y;wire a_IBUF_1;wire clk_BUFGP_3;wire enable_clk_IBUF_5;wire rst_n_IBUF_7;wire rst_n_inv;wire y_OBUF_10;FDCE y_1 (.C(clk_BUFGP_3),.CE(enable_clk_IBUF_5),.CLR(rst_n_inv),.D(a_IBUF_1),.Q(y_OBUF_10));IBUF enable_clk_IBUF (.I(enable_clk),.O(enable_clk_IBUF_5));IBUF rst_n_IBUF (.I(rst_n),.O(rst_n_IBUF_7));IBUF a_IBUF (.I(a),.O(a_IBUF_1));OBUF y_OBUF (.I(y_OBUF_10),.O(y));BUFGP clk_BUFGP (.I(clk),.O(clk_BUFGP_3));INV rst_n_inv1_INV_0 (.I(rst_n_IBUF_7),.O(rst_n_inv));

endmodule

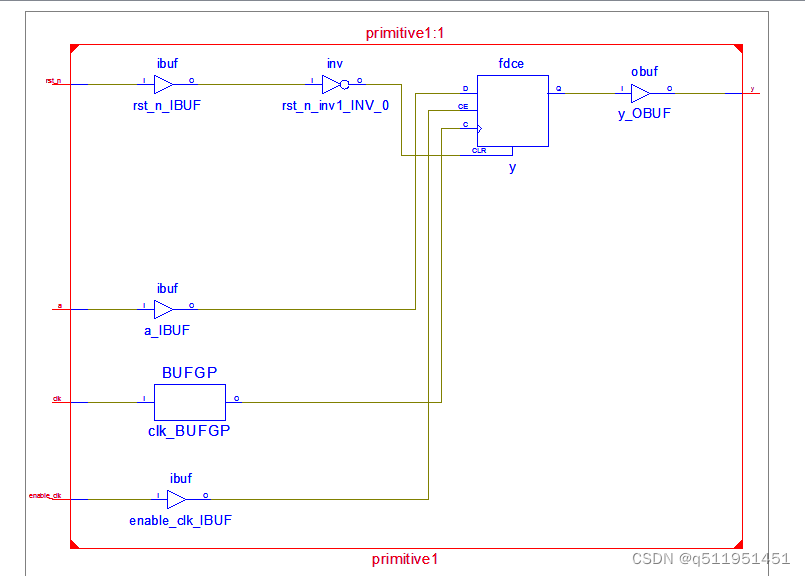

RTL结构图

技术原理图

5. 总结

1. 触发器是FPGA存储数据的基本单元

2. 触发器作为时序逻辑的基本元件,官方提供了丰富的配置方式,以适应各种可能的应用场景。