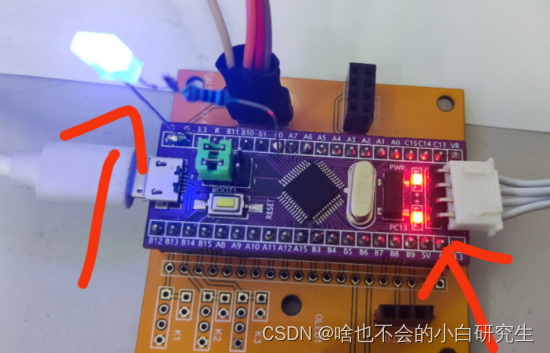

一.不通系列fpga对高速口的叫法不一样:

artix7——GTP

kintex7——GTX

virtex7——GTH

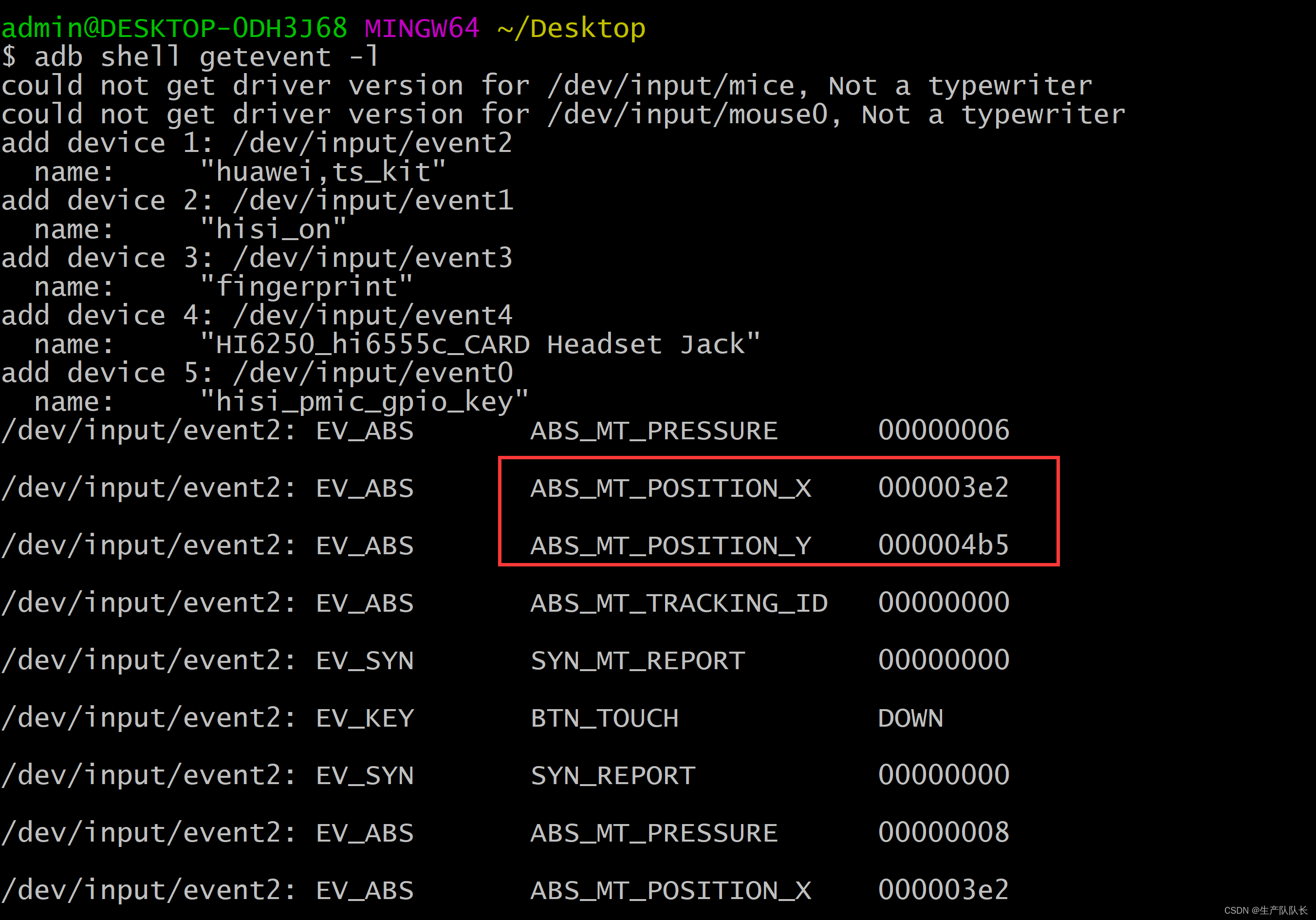

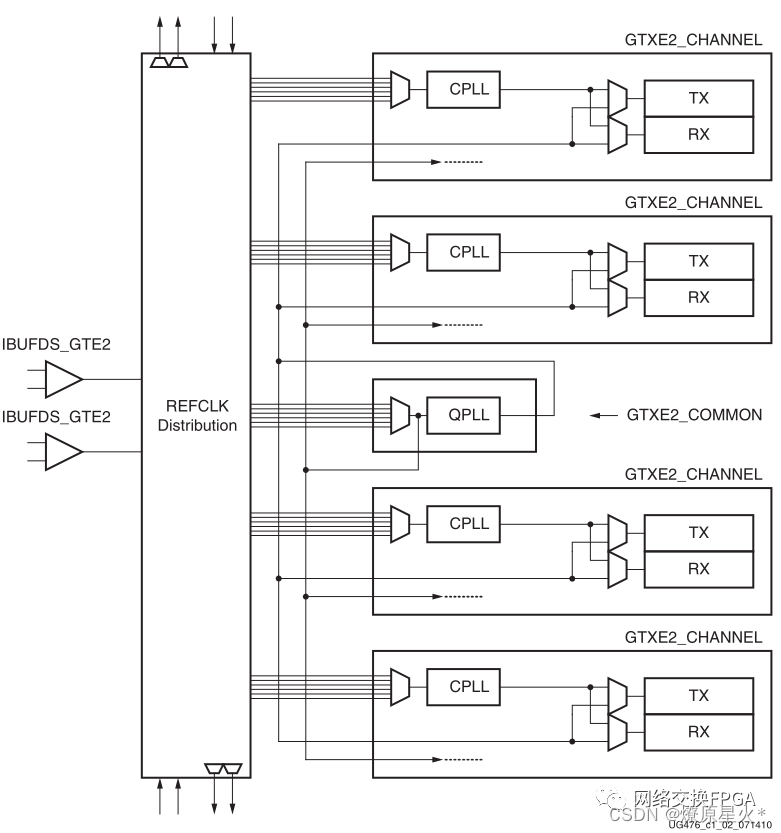

二.高速口的架构基本一致————4对rx/tx对+1个时钟模块(包含4个cpll+1个Qpll)

1:一个高速口【一个高速bank:(eg:bank116)】

2:如果需要更高的线速率则就需要更高频的pll(QPLL>cpll)一般在配置ip里面选择

3:一个时钟模块可以接2对差分时钟:满足于tx和rx不同时钟的需求。

4:一个高速口bank称为1个quad,每一个串行高速收发器称为一个Channel(如上图)

5:每个Quad有两个外部差分参考时钟源,每个外部参考时钟的输入必须经过IBUFDS_GTE2原语之后才能使用。——不然会报错,实践过。

6:7系列FPGA支持使用南北相邻Quad的参考时钟作为当前Quad的参考时钟,但是一个Quad的参考时钟源不能驱动超过3个Quad上的收发器(只能驱动当前Quad和南北方相邻两个Quad)。

7:对于一个GTX Channel来说,可以独立选择该收发器的参考时钟,可以选择QPLL,也可以选择CPLL,需要注意的是,每一个Quad上只有一个QPLL资源,重复例化会导致布线报错。

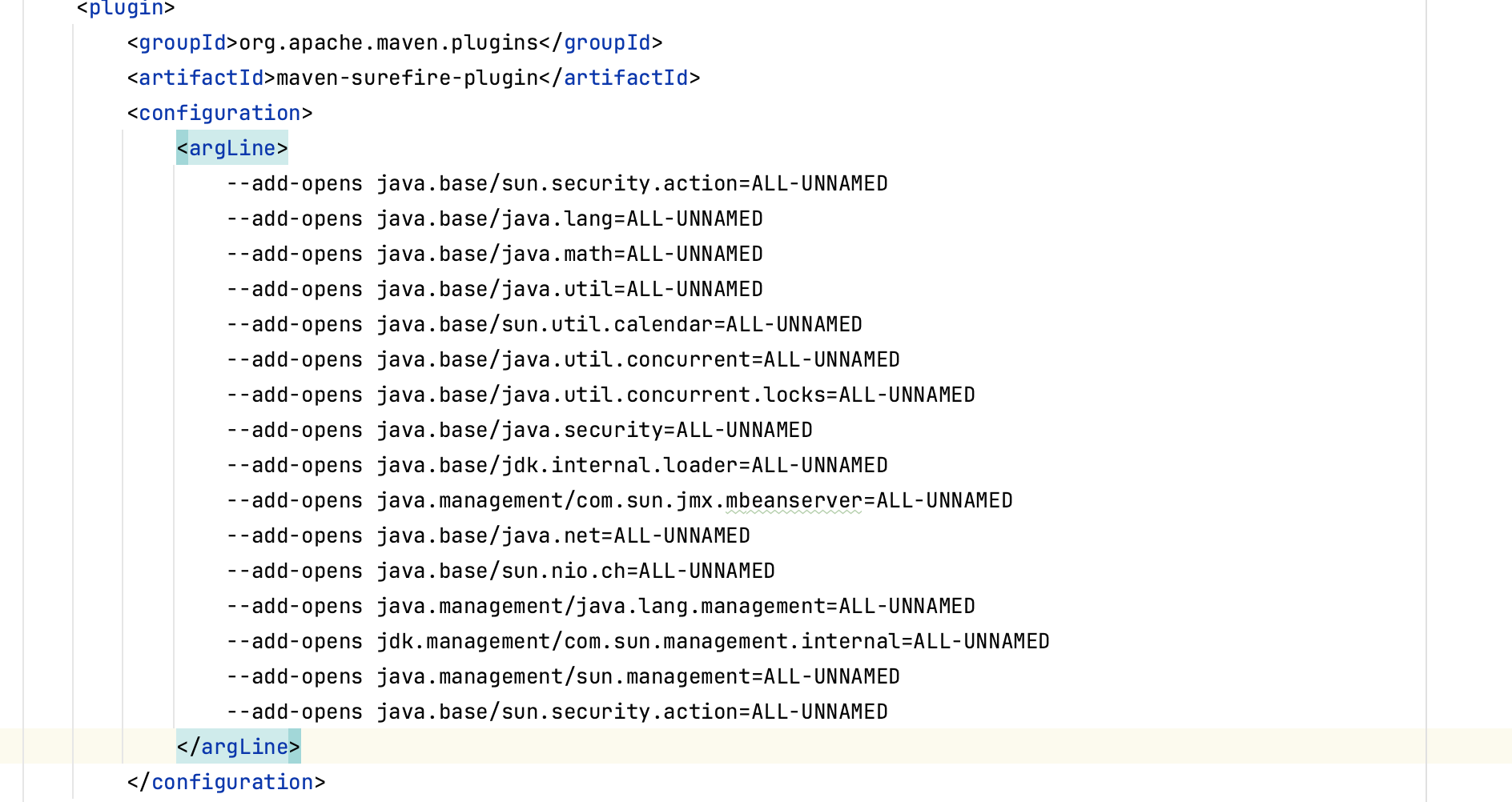

8:进入pcie ip核的系统时钟(sys_clk)最好不要给其他模块使用如(mmcm ip核)实测会报错的。