概述

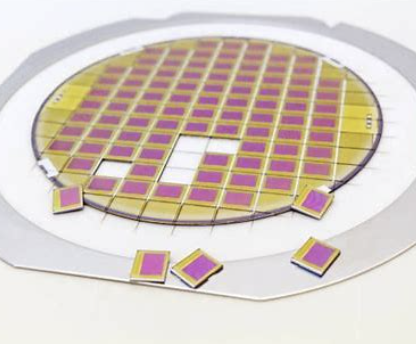

集成电路是由硅晶圆(wafer)切割出来的芯片(die)组成的。每个晶圆可以切割出数百个芯片。

ASIC是指针对特定应用而设计的集成电路(Application Specific Integrated Circuit),与通用的存储器、微处理器等不同。ASIC有以下几种类型:

全定制ASIC(Full-Custom ASIC):这种类型的ASIC是完全手工设计的,没有使用预先设计好的逻辑门,而是自己绘制芯片的版图(layout)。

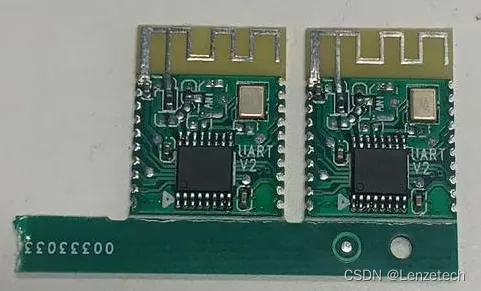

标准单元ASIC(Standard Cell ASIC):这种类型的ASIC是使用预先设计好的逻辑门,例如AND,NOR等,来构建电路。这些逻辑门被称为标准单元(Standard Cell)。标准单元ASIC的优点是设计者可以节省时间、金钱和风险,因为标准单元库已经过设计和测试。每个标准单元都是用全定制的方法设计的,可以进行单独的优化。

设计ASIC时,需要平衡以下几个目标:

速度(Speed):指芯片运行的时钟频率和响应时间,影响芯片的性能和效率。

面积(Area):指芯片占用的硅晶圆面积,影响芯片的成本和产量。

功耗(Power):指芯片运行时消耗的电能,影响芯片的可靠性和散热。

上市时间(Time to Market):指从设计开始到产品上市所需的时间,影响芯片的竞争力和市场占有率。

为了实现这些目标,设计者需要熟悉CMOS工艺,即使用互补金属氧化物半导体(Complementary Metal Oxide Semiconductor)制造芯片的技术。

CMOS工艺

1.1 CMOS工艺

CMOS工艺是目前最常用的芯片制造技术,它利用互补金属氧化物半导体(Complementary Metal Oxide Semiconductor)来构建电路。CMOS电路由NMOS和PMOS两种类型的MOSFET晶体管组成。

1.2 MOSFET晶体管

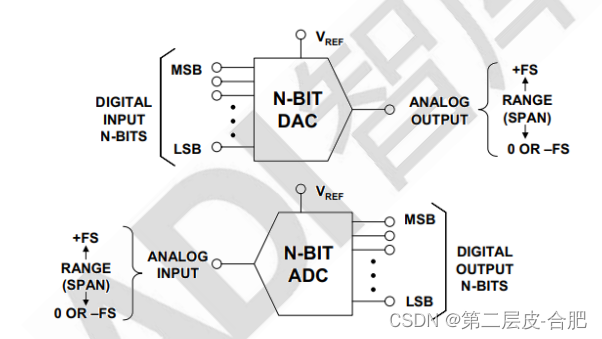

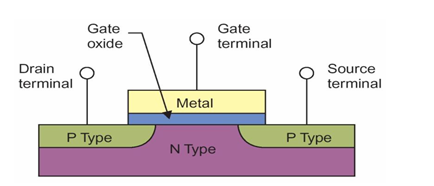

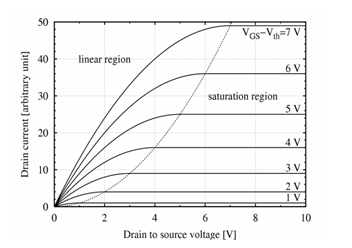

MOSFET是金属氧化物半导体场效应晶体管(Metal Oxide Semiconductor Field Effect Transistor)的简称,它是一种电压控制的开关器件,也是数字集成电路设计中的基本单元。MOSFET的结构和工作原理如下图所示。

CMOS工艺利用NMOS和PMOS两种MOSFET来实现高密度、复杂的数字集成电路,主要用于信号处理。CMOS工艺的优点是低功耗、高速度和易于集成等。在数字IC中,MOSFET可以看作是简单的开关。例如:CMOS反相器只需要一个PMOS和一个NMOS晶体管。

当输入为逻辑“0”时,PMOS导通,NMOS截止,输出负载电容被充电,输出为逻辑“1”。

当输入为逻辑“1”时,PMOS截止,NMOS导通,输出负载电容被放电,输出为逻辑“0”。

逻辑门的输出负载电容由两部分组成:本征电容和外部电容(走线、扇出等)。PMOS和NMOS的载流子分别是空穴和电子。由于电子的迁移率比空穴高出一倍多,导致输出上升时间和下降时间不对称。

为了平衡这种差异,通常让PMOS的宽长比(W/L)比NMOS的大一些。这样可以使PMOS和NMOS具有相近的驱动能力(drive strength)。

在标准单元库中,晶体管的长度L一般是固定的,而宽度W则根据不同门的驱动需求进行调整。

1.3 CMOS集成电路的功耗

CMOS集成电路的功耗主要有以下三个来源:

动态功耗:由于电路负载电容在开关过程中的充放电而产生。给定频率f,动态功耗为:负载电容* Vdd * Vdd * f

短路功耗:由于PMOS和NMOS在开关过程中同时导通而形成短路路径而产生。

静态功耗:由于晶体管存在漏电流而产生。

1.4 CMOS传输门

将PMOS和NMOS并联起来就形成了传输门。传输门可以将输入信号传递到输出端。

1.5 时序元件

在CMOS中,可以通过反馈回路来实现逻辑值的存储,这样的元件被称为时序元件。最简单的时序元件就是两个反相器相互连接。基于这种结构,可以有两种基本的时序元件,分别是:

1、锁存器(Latch):锁存器是在两个反相器之间加入一个传输门来控制数据的输入和输出。

当传输门的控制信号为逻辑“1”时,传输门打开,输入信号“D”可以传递到输出端。

当控制信号为逻辑“0”时,传输门关闭,输出端保持原来的值不变。

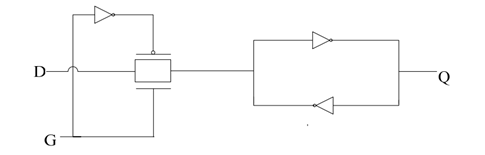

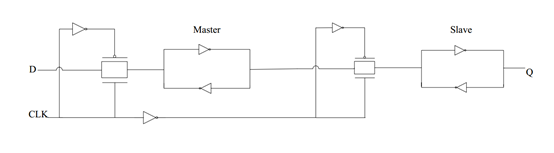

2、触发器(Flip-Flop):触发器是由两个锁存器串联而成的。第一个锁存器叫做主锁存器(Master latch),第二个锁存器叫做从锁存器(Slave latch)。

在这种情况下,传输门的控制信号就是时钟信号(Clock)。时钟信号经过反相后送到从锁存器的传输门。

当时钟信号为高电平时,主锁存器的传输门打开,输入信号“D”可以被两个反相器锁定。同时,由于时钟信号反相,从锁存器的传输门关闭,输出信号“Q”保持原来的值不变。

当时钟信号为低电平时,从锁存器的传输门打开,输出信号“Q”更新为主锁存器锁定的值。此时,输出信号“Q”与输入信号“D”的变化无关。

由于触发器只在时钟信号由低变高的上升沿更新数据,所以这种类型的触发器叫做正边沿触发器。如果触发器只在时钟信号由高变低的下降沿更新数据,则叫做负边沿触发器。

芯片设计的过程

要设计芯片,首先需要有一个清晰的设计目标和功能需求(Idea)。

在ASIC设计流程中,这个Idea会不断地转化为不同的表现形式。

ASIC设计流程的第一步就是把Idea写成详细的规格说明书(Specifications)。规格说明书包括:

设计的目标和约束条件。

设计的功能描述。

设计的性能指标,如速度和功耗。

设计的面积预估。

设计的制造工艺和设计方法选择。

传统意义上,ASIC设计流程如下所示:

1、给出设计的结构和功能分解(Structural and Functional Description)。这意味着要确定使用什么样的设计架构,例如 RISC / CISC,ALU,流水线等,并且将整个系统划分为若干个子模块。每个子模块的功能也要在规格说明书中明确定义。

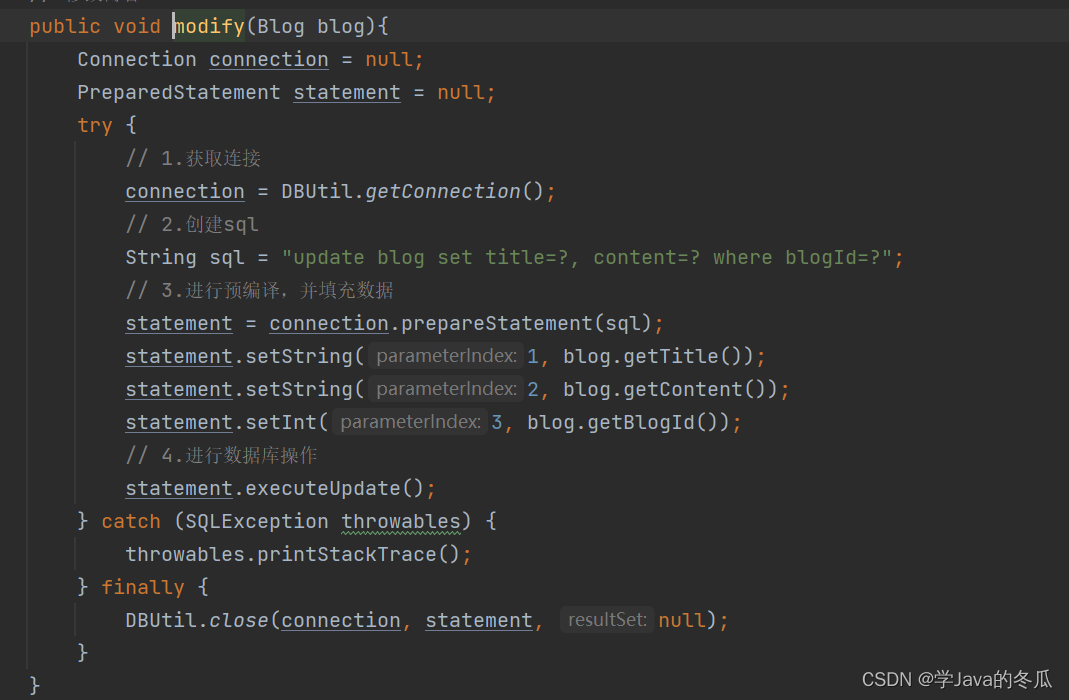

2、确定了系统层次结构之后,就要开始用具体的逻辑元素来实现设计的功能。这一步称为RTL级逻辑设计(Register Transfer Level)。RTL设计通常用硬件描述语言(Verilog、VHDL)来编写。硬件描述语言(HDL)是一种用于描述数字系统的语言,可以用来表示逻辑门、微处理器、存储器、触发器等任何级别的硬件。在这个阶段,要对设计进行功能验证,以确保设计符合规格说明书的要求。

3、功能验证

4、逻辑综合(Logic synthesis),使用Design Compiler (Synopsys),Genus(Cadence)等综合工具,将 RTL代码转换为优化后的门级网表(Gate Level Netlist)。综合工具需要输入RTL代码和标准单元库(Standard cell library),输出门级网表。标准单元库是集成电路设计中常用的基本逻辑模块的集合。综合工具在进行逻辑综合时,要考虑各种约束(Constraints),如时序、面积、可测性和功耗等。综合工具会根据不同的优化策略和代价函数(cost function),来寻找满足约束条件的最佳实现方案。逻辑综合完成之后,会得到一个只包含结构信息而不包含行为信息的门级网表。

5、对门级网表进行功能验证,以检查是否与RTL代码一致。

6、门级网表的物理实现(Physical Implementation)。这一步是将门级网表映射到芯片上的具体位置和连线。物理实现需要考虑制造工艺对布局布线(Layout)的限制条件,如DRC规则等。物理实现步骤包括三个子步骤:Floor planning->Placement->Routing。物理实现的输出是GDSII文件。这是芯片制造厂所需要的文件格式。物理实现可以由IC Compiler (Synopsys)、Innovus (Cadence)等软件完成。

7、进行物理验证(Physical Verification),以检查是否满足DRC规则、LVS规则等。

8、时序分析。对于任何有特定时钟频率要求的设计,都必须进行时序分析(timing analysis)。我们需要检查设计是否满足规格说明书中的时序要求。这是通过静态时序分析(Static Timing Analysis)工具完成的,例如Primetime(Synopsys)。它会检查设计中所有的时序路径,来验证设计是否存在时序违规(timing violations)。例如:建立时间(setup)、保持时间(hold)等。

9、在物理实现和时序分析都通过之后,设计就可以交付给制造厂进行制造(Fabrication)了。制造完成之后,芯片会被切割、封装和测试。

最后,值得思考的是,我们是否一定要遵从这种瀑布式开发流程???能否尽可能地流程左移。