目录

1.理论

2.代码

2.1 touch_ctrl_led.v

2.2 tb_touch_ctrl_led

1.理论

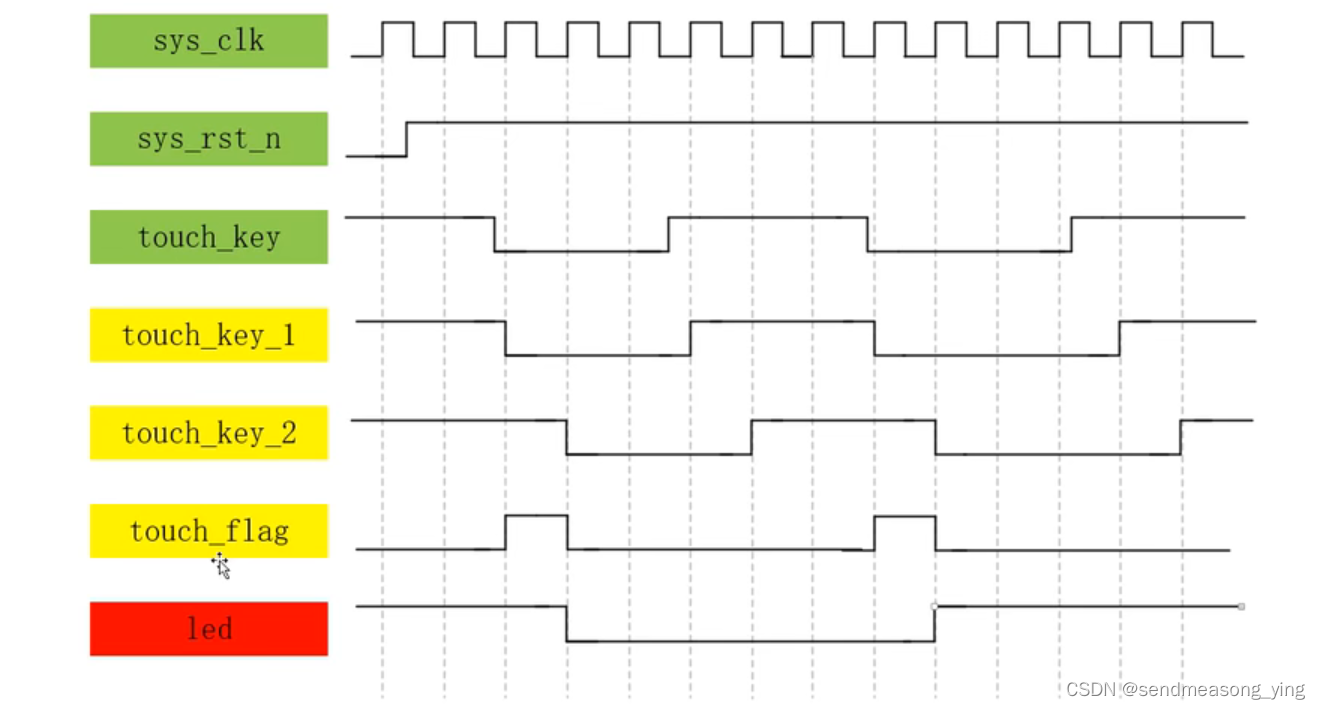

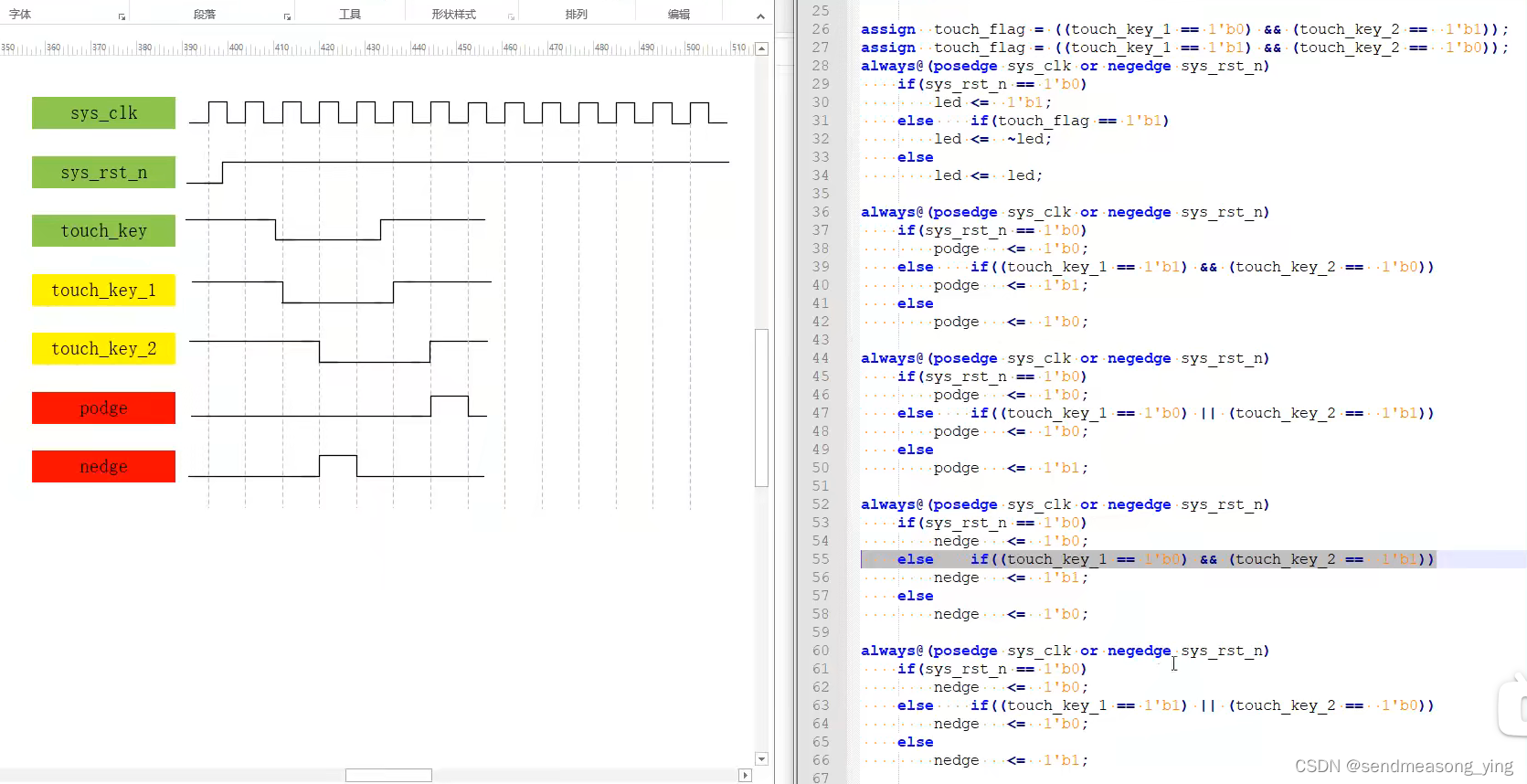

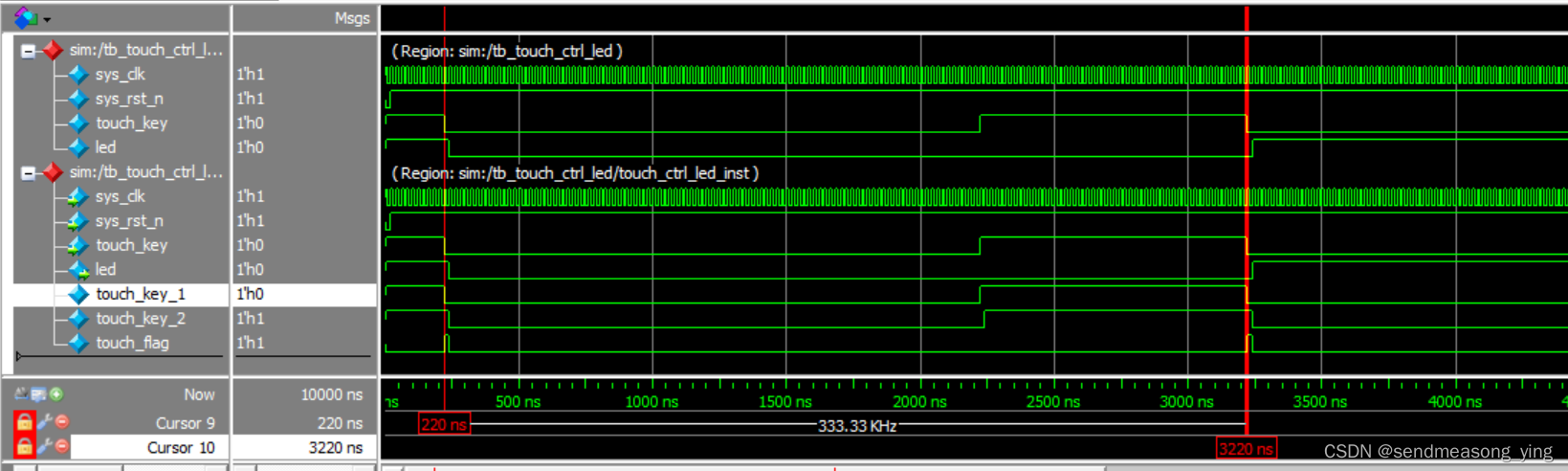

以上的波形图的touch_flag是采用组合逻辑的方式产生的。

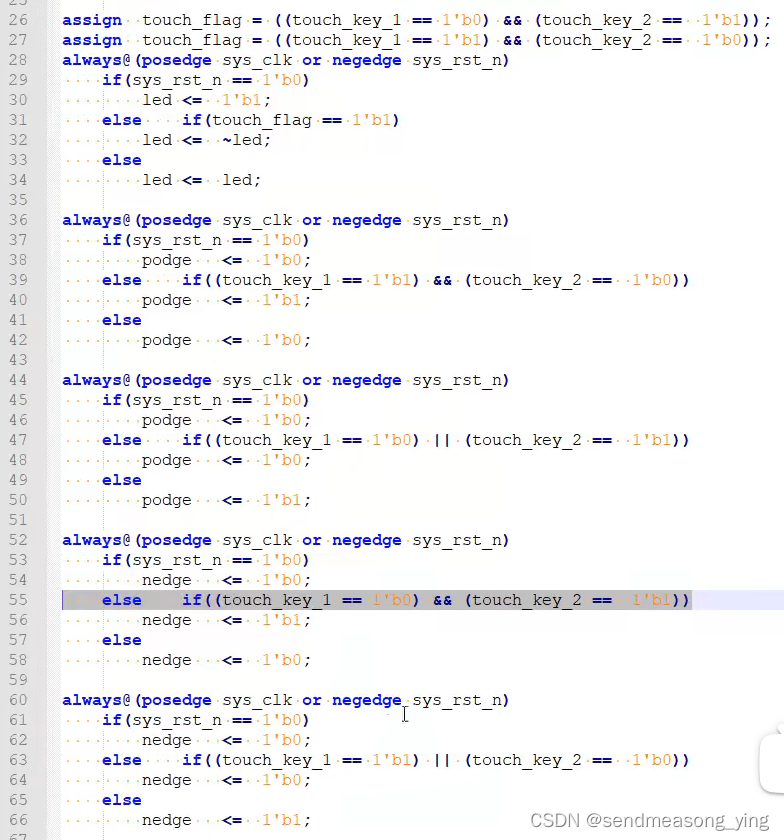

以上的touch_flag是采用时序逻辑产生的,时序逻辑会延迟一拍。

以上是上升沿和下降沿的组合逻辑和时序逻辑实现,逻辑或的写法刚好是逻辑与的两个寄存器的值反过来。

2.代码

2.1 touch_ctrl_led.v

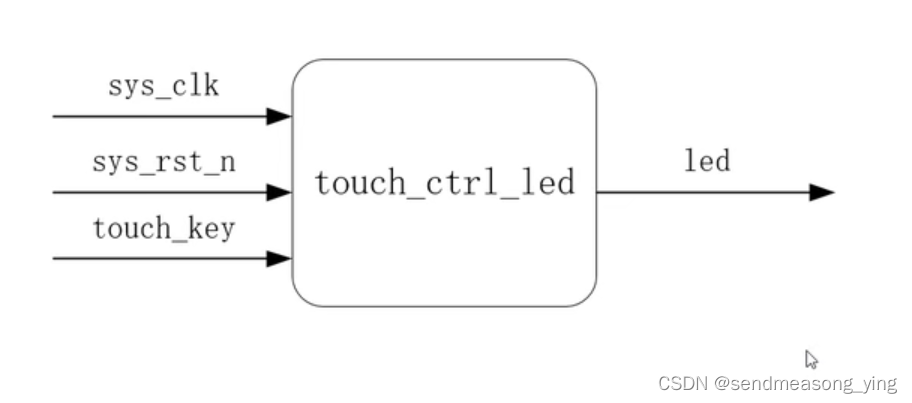

module touch_ctrl_led(input wire sys_clk ,input wire sys_rst_n ,input wire touch_key ,output reg led

);reg touch_key_1;

reg touch_key_2;

wire touch_flag; //因为没有延迟一拍所以是组合逻辑,wire形//边沿检测的作用就是能够准确识别出单比特信号的上升沿或下降沿

assign touch_flag=((touch_key_1==1'b0)&&(touch_key_2==1'b1));always@(posedge sys_clk or negedge sys_rst_n)if(sys_rst_n==1'b0)begintouch_key_1<=1'b1;touch_key_2<=1'b1;endelse if(sys_rst_n==1'b1)begintouch_key_1<=touch_key;touch_key_2<=touch_key_1;endalways@(posedge sys_clk or negedge sys_rst_n)if(sys_rst_n==1'b0)led<=1'b1;else if(touch_flag==1'b1)led<=~led;elseled<=led;endmodule2.2 tb_touch_ctrl_led

`timescale 1ns/1ns

module tb_touch_ctrl_led();reg sys_clk;

reg sys_rst_n;

reg touch_key;

wire led;initialbeginsys_clk=1'b1;sys_rst_n=1'b0;touch_key=1'b1;#20sys_rst_n=1'b1;#200touch_key=1'b0;#2000touch_key=1'b1;#1000touch_key=1'b0;#3000touch_key=1'b1;endalways #10 sys_clk=~sys_clk;touch_ctrl_led touch_ctrl_led_inst(.sys_clk (sys_clk),.sys_rst_n (sys_rst_n),.touch_key (touch_key),.led (led)); endmodule2.3 仿真结果

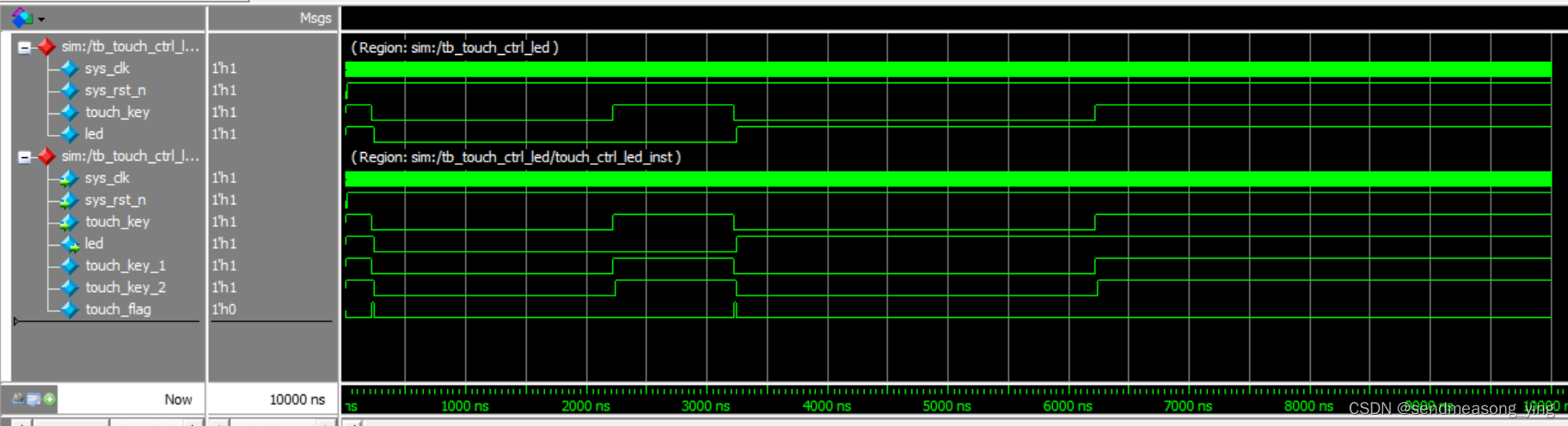

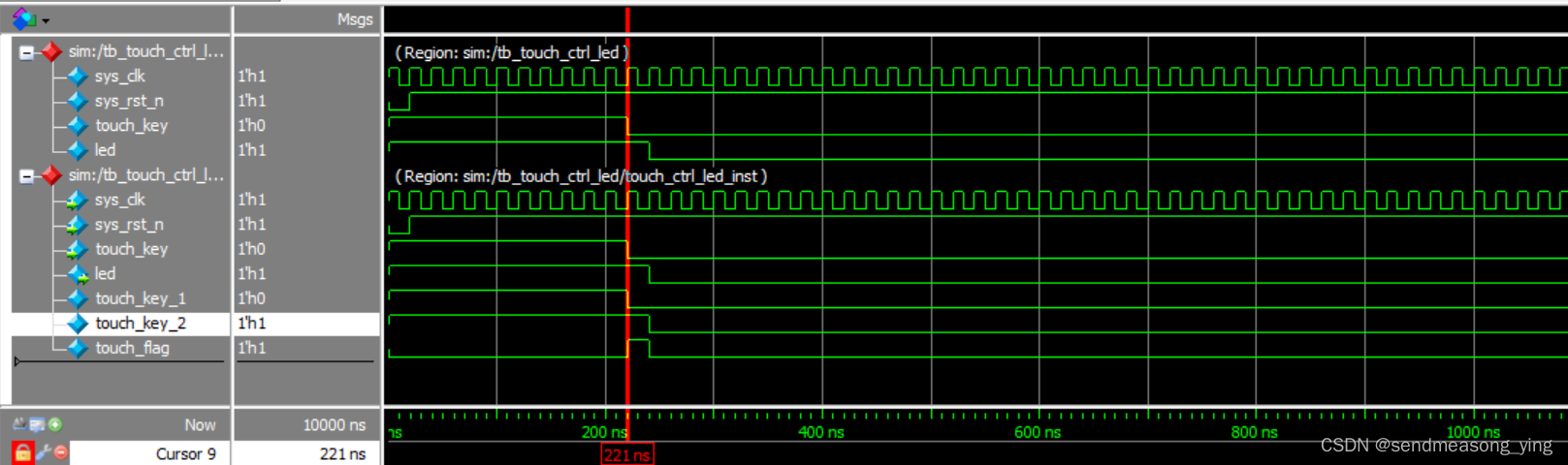

![[渗透测试学习] Hospital - HackTheBox](https://img-blog.csdnimg.cn/direct/65d696d108614b75942e2b82ff34a348.png)