IIC,存储器总结

- 存储器介绍

- AT24C02介绍

- IIC介绍

- 扩展 上拉,下拉,开漏

- IIC时序结构

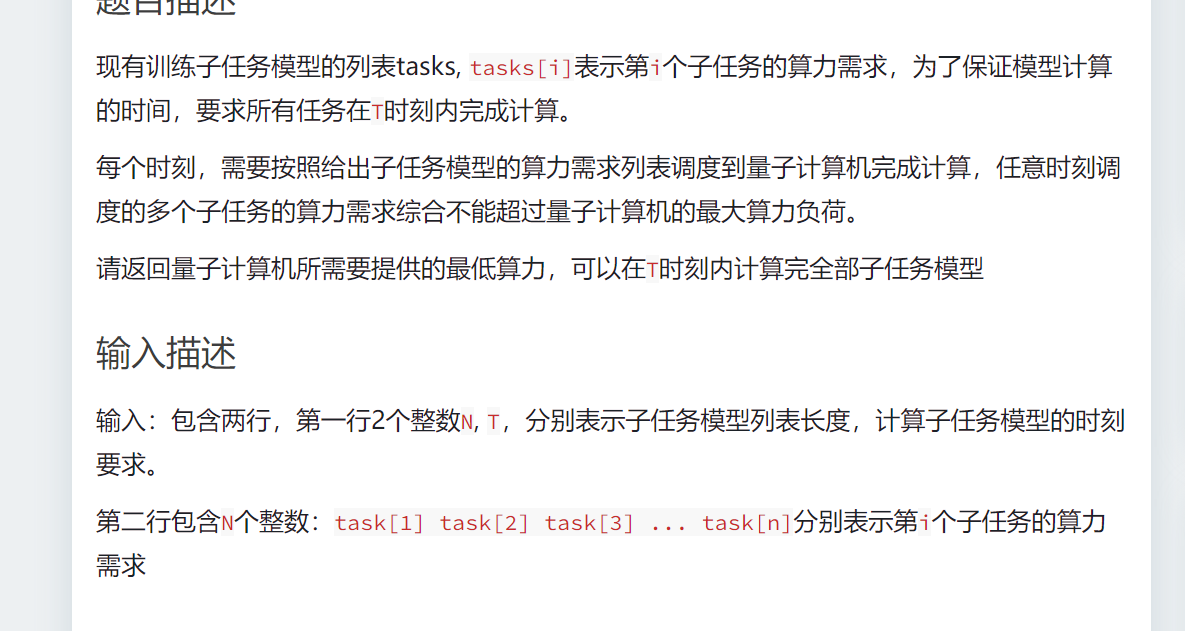

存储器介绍

存储器介绍:

RAM易失性存储器/RAM:随机存取存储器(英语:Random Access Memory,缩写:RAM),也叫主存,是与CPU直接交换数据的内部存储器。

ROM非易丢失存储器/读取只读存储器(英语:Read Only Memory,缩写:ROM),包括闪存,硬盘,外存,掉电并不丢失,存储速度慢

优点:ROM:掉电不丢失,存储容量大;RAM:存取速度快

缺点:ROM:存取速度慢;RAM:掉电丢失

分类:

RAM:SRAM(静态RAM)触发器,用电路存储数据;DRAM(动态RAM)速度最快,例如:内存条,电容存储数据常用CPU

ROM:Mask ROM(掩膜ROM)PROM(可编程ROM),EPROM(可擦除可编程),E2PROM(电可擦除可编程ROM) 前四种是一个家族,Flash(内存) 硬盘,软盘,光盘等

AT24C02介绍

AT24C02是一种可以实现掉电不丢失的存储器,可用于保存单片机运行时想要永久保存的数据信息

存储介质:E2PROM

通讯接口:I2C总线

容量:256字节

SCL、SDA I2C接口

A0、A1、A2 I2C地址

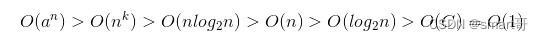

IIC介绍

IIC(Inter IC BUS)内部集成电路总线 是一种通用数据总线

两根 通信线:SCL (Serial Clock) 、SDA(Serial Data)

同步、半双工(只有一个Data数据线)、带数据应答(数据接收到后有个应答,确定数据收到成功)

优点:通信标准统一

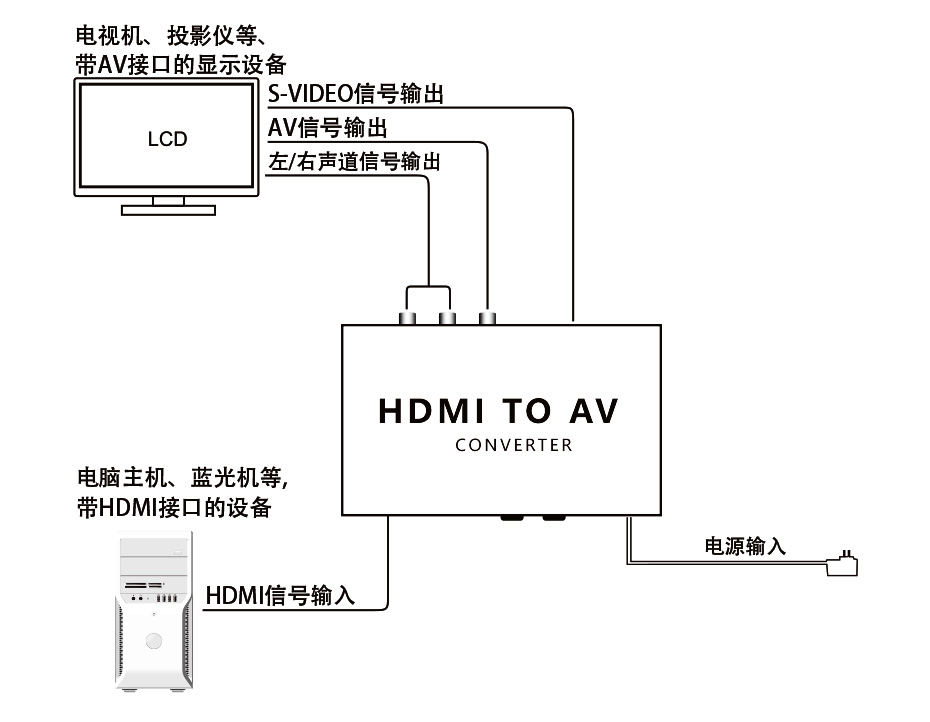

IIC电路规范:

所有IIC设备的SCL连在一起,SDA连在一起

设备的SCL和SDA模式要设置开漏输出模式

SCL和SDA各添加一个上拉电阻,阻值一般在4.7k

开漏输出与上拉电阻的共同作用实现了“线与”的功能,此设计主要是为了解决多机通信相互干扰的问题

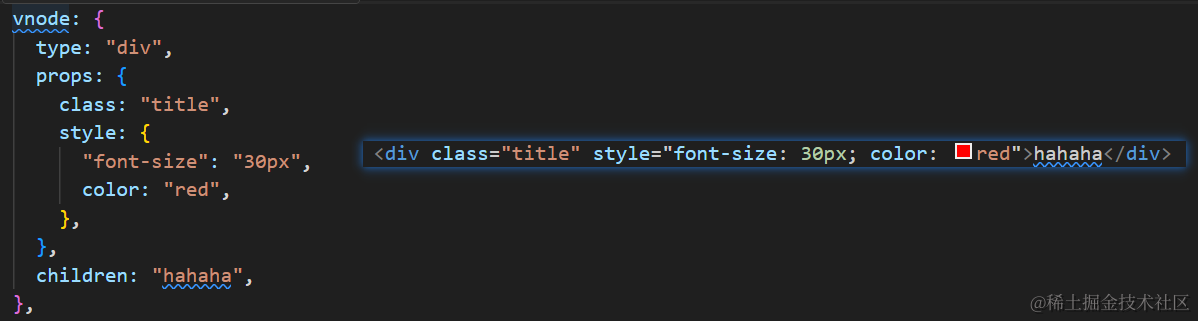

扩展 上拉,下拉,开漏

1.上、下拉电阻定义

上拉电阻是把一个信号通过一个电阻接到电源(Vcc),下拉电阻是一个信号通过一个电阻接到地(GND)。上下拉的最基本的作用是:将状态不确定的信号线通过一个电阻将其箝位至高电平(上拉)或低电平(下拉)

2.强上拉、弱上拉

强上拉、弱上拉的强弱只是上拉电阻的阻值不同,没有什么严格区分。例如:50Ω上拉,一般成为强上拉;100kΩ上拉则称为弱上拉。下拉也是一样的。强拉电阻的极端就是0Ω电阻,即将信号线直接与电源或低相连接。

芯片的管脚有三个类型,输出(Output,简称O)、输入(Input,简称I)和输入输出(Input/Output,简称I/O)。芯片的输入管脚,输入的状态有三个:高电平、低电平和高阻状态。高阻状态,即管脚悬空,很可能造成输入的结果是不定状态,引起输出震荡。有些应用场合不希望出现高阻状态,可以通过上拉电阻或下拉电阻使管脚稳定状态。

上拉电阻

如上图所示,若想让输出端out输出0 则In端给0,让开关闭合,此时数据输出线路到gnd,相当于下面的gnd那条线路接了个很大的电阻 此时,相当于下面很大的电阻和上方的电阻,(等效电路如下图所示)两个电阻并联,尽管输出端输出0,但被分到的电压大,驱动能力就较强,此时数据线上输出0

当In端给1时,开关断开,vcc直达数据输出,此时数据输出1,但这时由于串联电阻阻值大,所以驱动能力小

开漏输出

如上图所示,当out想输出0时,就让in给0,此时开关闭合时,out接地,输出0;

当cpu输出1时,开关断开,此时out处于悬空状态,浮空状态,电平不稳定,容易收到外界干扰

下拉电阻

为了简便观看,这里使用三极管来代替,三极管npn结构,np由于阻抗大,故而好像短路一样,若此时下拉电阻连的那根线没有电阻和gnd,则那根线(如下图)是不确定高低电平信号的,因为npn的np时阻抗大,相对于断开的状态。

若加下拉电阻(如下图所示)则可将此信号拉低,变为低电平,此时信号就确定了

但你可能会有一个这样的疑问,如果不要电阻了,直接接地,也可以实现输出为0,但如果直接接地,就只能给低电平了,如果想输入给高电平就需要按照下图:

当开关闭合时

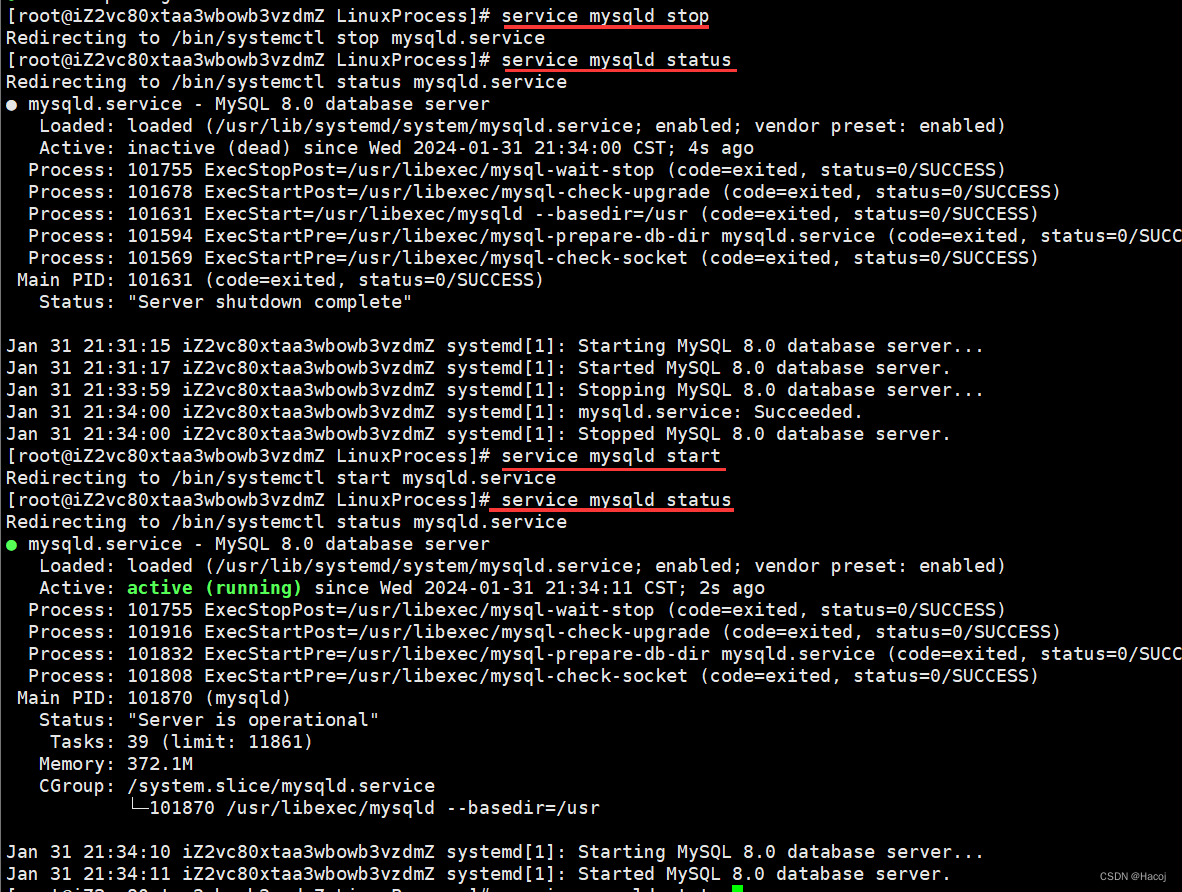

IIC时序结构

在时序图之前,先举个例子:

大家可以看到上图,一条杆子上有主机(单片机cpu)和从机1(AT24C02),从机2(OLED)…等等都是通过IIC通信的从机设备。如果主机想要和从机1想要通信,那么首先找到从机1的地址,怎么找到从机的地址的?如何通信呢?此时只有一个带有弹簧的杆子,可以上拉,下拉。可以想象,假如从机1,2,…都有自己的地址。假如从机1地址为0x80,从机2地址是0x84,那么如何找到这个从机1的地址呢?此时主机通过向下“拉杆子”,向上“松杆子”来实现,向下拉杆子代表低电平,松杆子代表高电平。此时输入1000 0000,即第一次不动,然后下拉杆子7次就可以找到0x80了,发送地址来进行对比,此时从机2一看,芜湖,和我的地址不同呀,它就开始自言自语道“那年我双手插兜,不知道什么是对手~”,此时从机1道:“嗨,我在这”。此时主机便和从机1匹配成功。那么怎么通信呢?仍然下拉杆子,松杆子实现呀,下拉1次代表低电平,松手代表高电平,如此循环八次,一个字节就实现完成发送了。如此完成了主机和从机通信,

那么如果从机想发信息到主机呢?同样的,这次我们把控制权交给从机1,让它拉杆子,在拉杆前要保证它能拉下来,也就是要恢复默认状态,杆子未被拉下来的状态,从机才能拉下来。记住,此时从机掌握控制权,它在控制着杆子

太快乐了。此时你是不是也觉得:原来IIC通信也是这样啊。太简单了。

好的,看完上面的咱们开始看时序图吧:

为了“拼图”正确,在scl高电平后将其拉低,什么?拼图?对的,就是拼图

主机发送数据:

注意:上图是时序SDA交叉的位置是说明数据在变化,0是下降沿,1是上升沿,当B7,B6…也即是SCL高电平时,下方SDA是不可以数据交换的,此时如果SDA是0,就读取0,是1就读取1,不能出现一会0,一会1数据时序图交叉变换的的情况了,因为此时SCL已经拉高了,B7代表高四位的最高位,依次B6,B5,…B0直到8次完成一个字节,所有的时序都是主机来进行的,单片机此时就是主机,AT24C02就是从机。

接收一个字节

注意:主机在接收前需要释放,还记得刚才讲的杆子的故事吗,从机想掌握控制权,那主机你必须要把杆子松开啊,你如果一直拉着杆子,我从机不就一直给你发送的就是0了吗?现在是我给你发数据,我需要掌握控制权啊。所以,要释放下SDA,把杆子先回到默认状态。

为了保证数据有反馈,必选在发送应答之后要调用一个接收应答,确保数据正常发送出去了;接收完应答后在发送应答

发送应答

在ACK时和上述原理相同,当ACK是高电平时就不在允许SDA有数据变化,此时读取SDA数据,如果是0,代表应答, 如果是1代表不应答。注意,发送应答也即是当主机接收来自从机的一个字节的数据之后,主机向从机发送应答,告诉从机,主机我收到小弟的数据了,如果想要给从机小弟发送应答,就发0,代表主机大哥已经接收到从机小弟的数据了,如果不想给从机小弟发送数据,就在刚开始时就释放SDA,这样默认就是1,给从机发送的也就是1了,此时代表非应答。

接收应答就是主机发送一个字节数据,然后从机小弟会给主机大哥发送一个字节的数据,这时主机大哥如果接收到的数据是0的话,代表从机小弟接收到主机大哥的数据了。从机小弟满怀感激的告诉从机大哥说“大哥,我收到你的数据了”,这边主机大哥说:“好的,收到了就好”。

注意:主机接收完从机的字节后,从机释放总线(为主机掌握控制权发送应答0做准备)此时如果从机一直控制着上方说的杆子,那么主机就没法发送一个数据0告诉从机 自己接收到数据了;主机接过总线,发送应答;而主机发送完字节后,先释放总线,从机接过总线,通过总线向主机发送应答。就像上面说的杆子故事一样

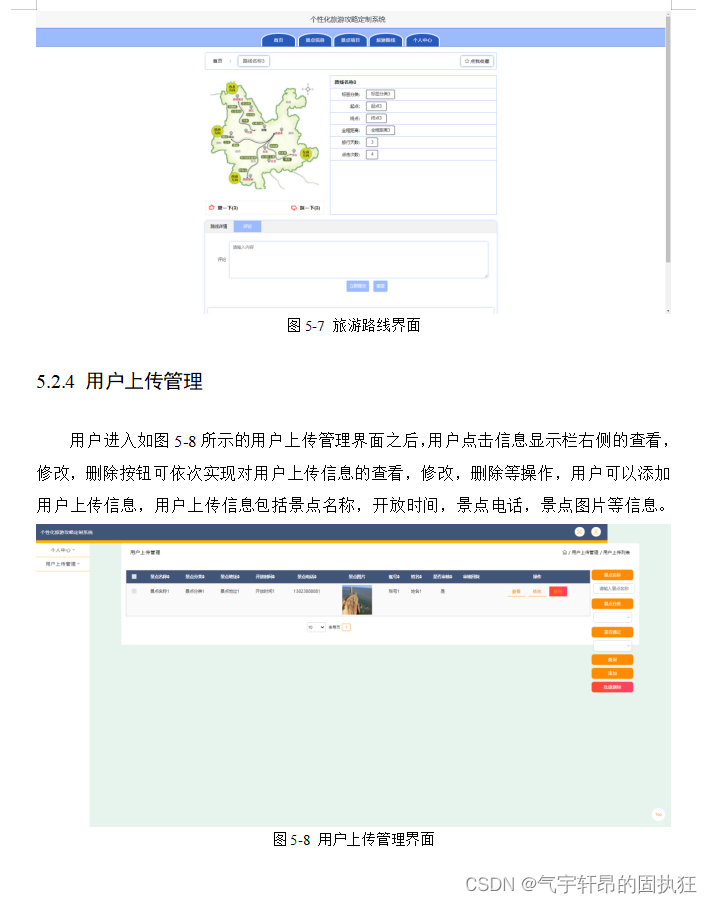

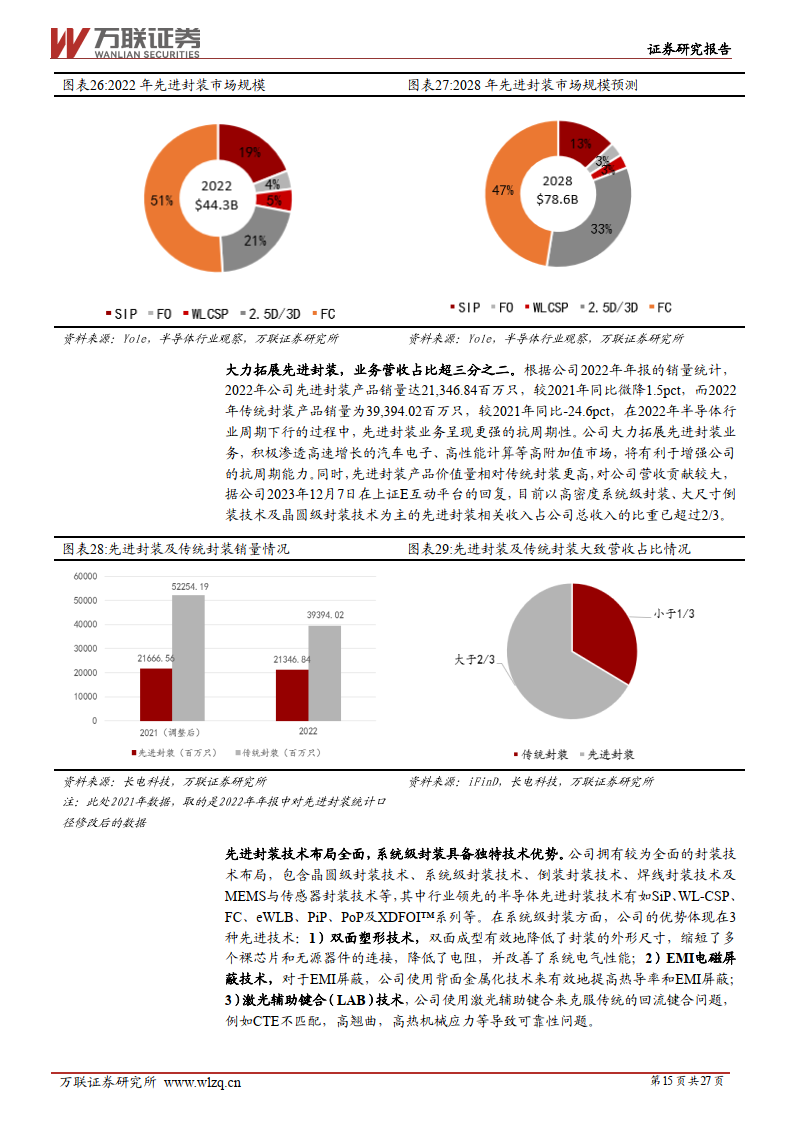

数据帧

主机向从机发送一帧数据

主机接收从机一帧数据

复合格式

复合格式

上面的前两种只有老师不说什么问题,就让小明回答问题,小明无奈,只能告诉老师自己临时想出来的答案,而采用下面的这种就可以避免这种弊端出现了。

AT24C02和一般的IIC通信结构

一般情况下,各种IIC通信时序图无非就上面三种的组合和拼装。

首先,给小可爱们的解释下,我们每一个设备也是有地址的,就跟我们的电脑的外设一样知道地址才能找到外设,找到设备后再确定存储设备内部的地址,好比得先找到这个人才能找他要什么东西

随机读

注意:每次读只能从上次写的地址开始读,所以提前假装写再去读,就能读到指定地址的数据